# AN13950

# TDA80xx EMVCo related measurements and calculations

Rev. 1.0 — 23 May 2023

**Application note**

### **Document Information**

| Information | Content                                                                                                                                                                                           |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | TDA8035, TDA8034, EMVCo, Low-Frequency-Oscillator                                                                                                                                                 |

| Abstract    | Measuring the internal low-frequency-oscillator of the TDA8034/35 and calculating the frequency of it. With the measured frequency the RSTIN timing for the activation procedure can be adjusted. |

### TDA80xx EMVCo related measurements and calculations

# **Revision history**

### **Revision history**

| Rev   | Date     | Description      |

|-------|----------|------------------|

| v.1.0 | 20230523 | Initial version. |

#### TDA80xx EMVCo related measurements and calculations

### 1 Introduction

Due to changes in the EMVCo test specification [1] which is ultimately tightening the window for pulling RST high. EMVCo compliancy fails on TDA8034 and TDA8035 could be observed.

This document describes:

- the changed EMVCo requirements and the impact of it

- the actual situation of the current TDA products and why some might fail in EMVCo reset cases

- · and how to overcome this issue

### 1.1 EMVCo requirements

The current EMVCo specification 4.3d ([1]), and later, enhanced the minimum clock frequency from 3.1 MHz to 4.7 MHz. The maximum clock frequency remains on 5 MHz.

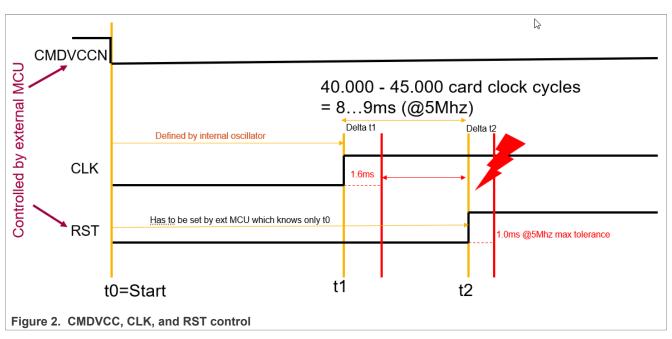

The acceptance criteria for RST is following, where t<sub>1</sub> refers to CLK applied and t<sub>2</sub> to RST high:

#### Acceptance criteria

The following acceptance criteria shall be met under all environmental and test conditions:

- 1. The time between t<sub>1</sub> and t<sub>2</sub> is between 40'000 and 45'000 clock cycles.

- 2. Each sequence of commands and answers is performed correctly.

Figure 1. EMVCo acceptance criteria

This results in a tighter window for pulling RST high in the activation, or reset procedure.

#### Before:

- Max: Every clock cycle is 1/3.1M 45.000 clock cycles are 14.516 ms (45.000/3.1M)

- Min: Every clock cycle is 1/5M 40.000 clock cycles are equal to 8 ms (40.000/5M)

#### Now.

- Max: Every clock cycle is 1/4.7M 45.000 clock cycles are equal to 9.574 ms (45.000/4.7M)

- Min: Every clock cycle is 1/5M 40.000 clock cycles are equal to 8 ms (40.000/5M)

### 1.2 Actual situation

Due to the frequency spread of the internal low-frequency-oscillator, the EMVCo requirement might not be met, if the actual running frequency of the oscillator is too low or high.

The host MCU is in control of CMDVCC and RST, but the CLK signal is controlled by the TDA and unknown to the MCU. EMVCo requires that after 40.000 to 45.000 clock cycles RST is pulled high. When CLK is started depends on the internal low-frequency-oscillator, but the actual clock frequency is unknown to the MCU.

#### TDA80xx EMVCo related measurements and calculations

If the low-frequency-oscillator is running on the minimum frequency side, CLK will be raised later and RST is ultimately pulled high, from the host MCU, too early. Vice versa, if the low-frequency-oscillator is running more on the maximum side of its frequency, CLK will be raised earlier and RST ultimately will be pulled high, from the MCU, too late.

### 1.3 Counter measure

To overcome this situation, one solution is that the host MCU is aware of the low-frequency-oscillators frequency and takes it into account for the time CMDVCC  $\rightarrow$  RST.

On following pages the measurement, calculation and the conclusion will be explained.

### **Other TDAs**

At the current version of the document, this proposal is explained by using a TDA8035. This solution can be used for all TDA products by adjusting the calculation respectively to the TDAs data sheet.

#### TDA80xx EMVCo related measurements and calculations

### 2 Measurements

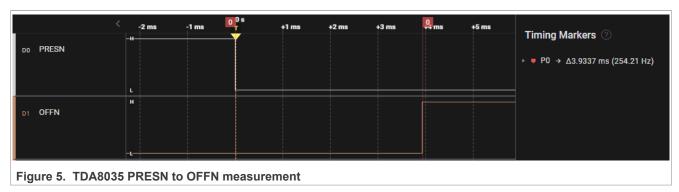

There is no direct way to measure the internal low-frequency-oscillator's frequency. But the debounce time of PRESN to OFFN is directly related to the internal low-frequency-oscillators frequency.

By measuring the time between the PRESN and OFFN signal, the frequency can be calculated.

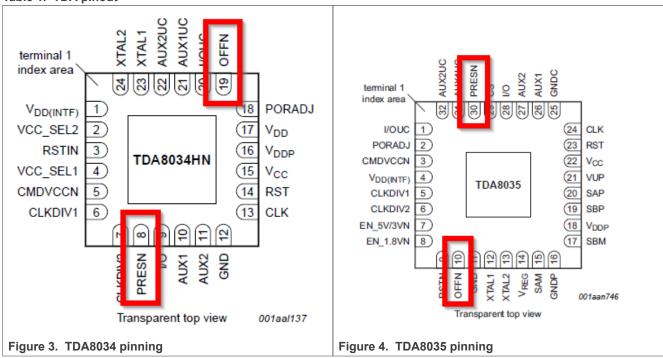

Table 1. TDA pinout

Usually the PRESN is not connected to the host MCU and only OFFN is known. But for this calculation it is necessary to measure the time between PRESN and OFFN. There are several ways how this can be achieved. Manual measuring, routing PRESN to the MCU or triggering PRESN at a well-known time.

For future designs, it is recommended to route PRESN to an MCU input to measure this timing at need.

In figure Figure 5 the time between PRESN high  $\rightarrow$  low to OFFN low  $\rightarrow$  high has been measured, on a TDA8035 with **3.9337 ms**.

**Note:** If the time is measured by the host MCU (PRESN  $\rightarrow$  OFFN), it has to be made sure that this time is measured as accurate as possible. Interrupt latency, a polling approach, or an RTOS may introduce a delay significant enough to falsify the result. An accuracy of 0.1 ms can be considered as good enough.

AN13950

#### TDA80xx EMVCo related measurements and calculations

### 3 Calculation

From the debounce time (see [2], [3]) we can calculate the frequency of the internal oscillator.

Table 2. Calculation formula of fosc(int)\_Low of TDA8035

| Symbol           | TDA8035                                        | TDA8034                                            |

|------------------|------------------------------------------------|----------------------------------------------------|

| t <sub>deb</sub> | $tdeb = 1280*\frac{1}{f_{osc(int)\_Low}} $ (1) | $tdeb = 640^* \ \frac{1}{f_{osc(int)low}} \tag{2}$ |

| fosc(int)_Low    | $f_{osc(int)\_Low} = 1280*\frac{1}{tdeb} $ (3) | $f_{osc(int)low} = 640^* \frac{1}{tdeb} $ (4)      |

With the time of 3.9337 ms measured in <u>Figure 5</u>, the resulting frequency of the TDA8035s internal low-frequency-oscillator is: **325.39 kHz**

$$1280*\frac{1}{3.9337ms} = 325,39 \ kHz \tag{5}$$

With the known frequency of the internal low-frequency-oscillator and the activation sequence from the data sheet (see [2] [8.7 Activation sequence]), the time until CLK rises can be calculated and the internal MCU timer for RST adjusted accordingly.

At <u>Figure 6</u>, the timing is calculated. Where 'act.' is the column with the actual measured frequency of the low-frequency-oscillator, compared to the calculation of the minimum, typical and maximum frequency.

| Signal | Frequency                      | act.   | min.  | typ.  | max.  |

|--------|--------------------------------|--------|-------|-------|-------|

|        | Toscint(freq high)             | 2500   | 2500  | 2500  | 2500  |

|        | Tosc(freq low)                 | 325,39 | 230   | 315   | 430   |

|        | fXtal                          | 5000   | 5000  | 5000  | 5000  |

|        | x                              | 0,002  | 0,002 | 0,002 | 0,002 |

|        | Marker                         |        |       |       |       |

|        | T = 64 x Toscint (freq high)   | 0,026  | 0,026 | 0,026 | 0,026 |

| CMDVCC | t0 = start                     |        |       |       |       |

| VUP    | t1 = t0 + 768 x Tosc(freq low) | 2,360  | 3,339 | 2,438 | 1,786 |

| VCC    | t2 = t1 + 3T/2                 | 2,399  | 3,378 | 2,476 | 1,824 |

| 1/0    | t3 = t1 + 10T                  | 2,616  | 3,595 | 2,694 | 2,042 |

| CLK    | t4 = t3 + x                    | 2,618  | 3,597 | 2,696 | 2,044 |

Figure 6. TDA8035 activation sequence calculation

**Note:** This calculation is for the **TDA8035**. For the TDA8034 it is slightly different, see [3] chapter [8.7 Activation sequence].

### TDA80xx EMVCo related measurements and calculations

### 4 Conclusion

With the known frequency of the internal low-frequency-oscillator and the activation sequence from the data sheet, the time until CLK rises can be calculated and the internal MCU timer for RST adjusted accordingly.

To have the best possible margin, it is recommended to target an RST low  $\rightarrow$  high transition at 42.500 cycles. At 5 MHz card clock (fXtal at Figure 6) this results in **8.5 ms**.

With the calculated time until CLK rise (see Figure 6) and the goal to have 8.5 ms between CLK rise and RST rise a total time of 2.6 + 8.5 = 11.1 ms from CMDVCC low to RST high shall be used.

#### TDA80xx EMVCo related measurements and calculations

### 5 TDA8034

The TDA8034s internal low-frequency-oscillator according to its data sheet ([3]):

| Internal o            | scillator           |               |     |     |     |     |

|-----------------------|---------------------|---------------|-----|-----|-----|-----|

| f <sub>osc(int)</sub> | internal oscillator | Shutdown mode | 100 | 150 | 200 | kHz |

|                       | frequency           | active state  | 2   | 2.7 | 3.2 | MHz |

Figure 7. TDA8034 internal oscillator

The activation sequence necessary for the calculation of CLK rise:

### 8.7 Activation sequence

The following device activation sequence is applied when using an external clock; see Figure 7:

- 1. Pin CMDVCCN is pulled LOW (t0).

- 2. The internal oscillator is triggered (t0).

- 3. The internal oscillator changes to high frequency (t1).

- 4. V<sub>CC</sub> rises from either 0 V to 3 V or 0 V to 5 V on a controlled slope (t2).

- 5. Pins I/OUC, AUX1UC and AUX2UC are driven HIGH (t3).

- 6. The clock on pin CLK is applied to the C3 contact (t4).

- 7. Pin RST is enabled (t5).

Calculation of the time delays is as follows:

- $t1 = t0 + 384 \times \frac{1}{fosc(int)low}$

- t2 = t1

- t3 = t1 + 17T / 2

- t4 = driven by host controller; > t3 and < t5

- t5 = t1 + 23T / 2

**Remark:** The value of period T is 64 times the period interval of the internal oscillator at high frequency ( $\frac{1}{fosc(int)high}$ ); t3 is called  $t_{d(start)}$  and t5 is called  $t_{d(end)}$ .

Figure 8. TDA8034 activation sequence

#### TDA80xx EMVCo related measurements and calculations

### 6 TDA8035

The TDA8035s internal low-frequency-oscillator "osc(int)\_Low" according to the data sheet [2] has following values:

| Internal os                           | cillator            |                              |     |     |     |     |

|---------------------------------------|---------------------|------------------------------|-----|-----|-----|-----|

| f <sub>osc(int)</sub>                 | internal oscillator | inactive state: osc(int)_Low | 230 | 315 | 430 | kHz |

|                                       | frequency           | active state: osc(int)_High  | 2.0 | 2.5 | 3.0 | MHz |

| Figure 9. TDA8035 internal oscillator |                     |                              |     |     |     |     |

The activation sequence according to the data sheet [2]:

### 8.7 Activation sequence

The following sequence then occurs with crystal oscillator (see Figure 8):

$T = 64 \times T_{oscint}$  (freq high)

- 1. CMDVCCN is pulled low (t0)

- 2. Crystal oscillator start-up time (t0).

- 3. The internal oscillator changes to its high frequency and DC-to-DC starts  $t1 = t0 + 768 \times T_{osc (freq low)}$

- 4.  $V_{CC}$  rises from 0 to selected  $V_{CC}$  value (5 V, 3 V, 1.8 V) with a controlled slope ( $t_2 = t_1 + 3T/2$ )

- 5. I/O, AUX1 and AUX2 are enabled ( $t_3 = t_1 + 10T$ ), until now, they were pulled LOW

- 6. CLK is applied to the C3 contact ( $t_4 = t_3 + \times$ ) with 200 ns <  $\times$  < 10  $\times$  1/f<sub>Xtal</sub>

- 7. RST is enabled ( $t_5 = t_1 + 13T$ ).

Figure 10. TDA8035 activation sequence

Used in the calculation Figure 6 "TDA8035 activation sequence calculation".

### TDA80xx EMVCo related measurements and calculations

### 7 References

- [1] EMV Contact Terminal Level 1 Type Approval Version 4.3d December 2021

- [2] TDA8035 High integrated and low power smart card interface Rev. 3.1 30 June 2016

- [3] TDA8034 Low power smart card interface Rev. 3.5 13 March 2020

#### TDA80xx EMVCo related measurements and calculations

## 8 Legal information

### 8.1 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

#### 8.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Suitability for use in non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <a href="mailto:PSIRT@nxp.com">PSIRT@nxp.com</a>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

**NXP B.V.** - NXP B.V. is not an operating company and it does not distribute or sell products.

### 8.3 Trademarks

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

AN13950

All information provided in this document is subject to legal disclaimers.

© 2023 NXP B.V. All rights reserved.

# TDA80xx EMVCo related measurements and calculations

| Tables  |             |         |                                                 |  |  |  |

|---------|-------------|---------|-------------------------------------------------|--|--|--|

| Tab. 1. | TDA pinout5 | Tab. 2. | Calculation formula of fosc(int)_Low of TDA8035 |  |  |  |

### TDA80xx EMVCo related measurements and calculations

# **Figures**

| Fig. 1. | EMVCo acceptance criteria3          | Fig. 6.  | TDA8035 activation sequence calculation | 6 |

|---------|-------------------------------------|----------|-----------------------------------------|---|

| Fig. 2. | CMDVCC, CLK, and RST control 4      | Fig. 7.  | TDA8034 internal oscillator             | 8 |

| Fig. 3. | TDA8034 pinning 5                   | Fig. 8.  | TDA8034 activation sequence             | 8 |

| Fig. 4. | TDA8035 pinning 5                   | Fig. 9.  | TDA8035 internal oscillator             | 9 |

| Fig. 5. | TDA8035 PRESN to OFFN measurement 5 | Fig. 10. | TDA8035 activation sequence             | 9 |

### TDA80xx EMVCo related measurements and calculations

### **Contents**

| 1   | Introduction       | 3  |

|-----|--------------------|----|

| 1.1 | EMVCo requirements |    |

| 1.2 | Actual situation   |    |

| 1.3 | Counter measure    | 4  |

| 2   | Measurements       | 5  |

| 3   | Calculation        | 6  |

| 4   | Conclusion         | 7  |

| 5   | TDA8034            | 8  |

| 6   | TDA8035            | 9  |

| 7   | References         | 10 |

| 8   | Legal information  | 11 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.