#### **Document information**

| Information | Content                                                                                                                                                                               |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | i.MX6ULL Applications Processor Evaluation Kit (MCIMX6ULL-EVK),<br>GenAVB/TSN stack, Audio Video Bridging (AVB), Media Clock Recovery,<br>tunable audio PLL                           |

| Abstract    | This document describes the required hardware rework to be applied on the i.MX6ULL Applications Processor Evaluation Kit (MCIMX6ULL-EVK) in order to support the NXP GenAVB/TSN stack |

#### i.MX6ULL EVK GenAVB/TSN Rework Application Note

## 1 Introduction

This document describes the required hardware rework to be applied on the i.MX6ULL Applications Processor Evaluation Kit (MCIMX6ULL-EVK) in order to support the NXP GenAVB/TSN stack.

To make MCIMX6ULL-EVK board fully support Audio Video Bridging (AVB), an important aspect is to add support for the Media Clock Recovery mechanism.

The NXP GenAVB/TSN stack supports two methods for media clock recovery depending on the underlying hardware:

- External method: Where an external low-jitter multiplier is needed on the board.

- Internal method: Can be implemented on SoCs with a tunable audio PLL on the fly. No external hardware is needed.

As the i.MX6ULL comes with a tunable audio PLL, the second method is implemented on the board.

# 2 Required connections

### 2.1 Media Clock Recovery: overall architecture

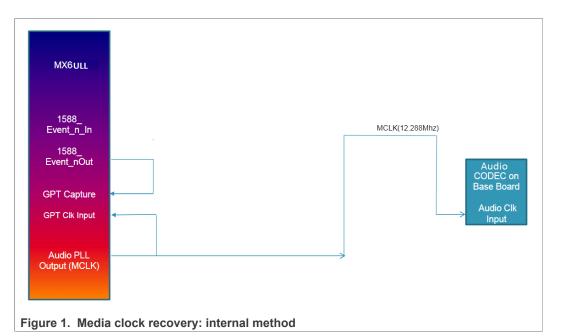

The media clock recovery mechanism is mainly implemented on the driver side. The internal of the mechanism is not the purpose of this document, but an overall description is given here.

The internal method relies on a few hardware blocks:

- The ENET 1588 timer in the Ethernet MAC (in Output Compare Mode): A stream of timestamps at a relatively low frequency drives the 1588\_EVENT signal.

- GPT timer: The GPT counter clock is connected to the Audio Master clock and the *GPT\_CAPTURE* input signal is connected to the *1588\_EVENT* from ENET. This arrangement makes drift calculation and adjustments, between the audio master clock and the media master clock (derived from the timestamps), possible on driver side.

i.MX6ULL EVK GenAVB/TSN Rework Application Note

# 2.2 Detailed connections and possible PAD assignments

For the MCIMX6ULL-EVK board, the mapping between the Linux network device name and the ENET instance number in the SoC is the following:

- ENET2: eth0

- ENET1: eth1

GenAVB/TSN stack works by default on eth0, therefore ENET2 is used.

**ENET2\_1588\_EVENTX\_OUT** signal from the Ethernet MAC should be connected to the **GPT2\_CAPTUREY** input capture channel in the General Purpose Timer (Instance 2).

#### Note:

- 1. In signal name **ENET2\_1588\_EVENTX\_OUT**, X represents the number of the IEEE 1588 Channel from 0 to 3, which is configurable in the device tree)

- 2. In signal name **GPT2\_CAPTUREY**, Y is one of the possible capture channels 1 or 2, which is configurable in the device tree.

In addition, **AUDIO MASTER CLOCK** serving the Audio codec, is connected to **GPT2\_CLK**. On MCIMX6ULL-EVK board, the audio master clock is on **SAI2\_MCLK** pad (However, this may vary for other audio interfaces).

On MCIMX6ULL-EVK, the codec is fed from the **SAI2\_MCLK**, which is already set to 12.288 MHz.

The GPT2\_CLK requires that its frequency **does not exceed the** <sup>1</sup>/<sub>4</sub> **of the peripheral clock** (66 MHz). This clock is by default set to 12.288 MHz. (Refer to the paragraph 30.2.1 in the *i.MX6ULL Reference Manual* [1].

Every signal can be routed through one or multiple routing pads. The table below summarizes the available i.MX6ULL signals and routing pads.

#### AN13678 Application note

Table 1. i.MX6ULL signal availability and routing pads

| Signal |                 | Pad (mode)        |

|--------|-----------------|-------------------|

| ENET2  | 1588_EVENT0_OUT | GPIO1_IO05(ALT6)  |

|        | 1588_EVENT1_OUT | UART1_RTS_B(ALT4) |

|        | 1588_EVENT2_OUT | LCD_DATA05(ALT3)  |

|        | 1588_EVENT3_OUT | LCD_DATA07(ALT3)  |

| SAI2   | MCLK            | JTAG_TMS (ALT2)   |

|        |                 | SD1_CLK (ALT2)    |

| GPT2   | CAPTURE1        | JTAG_TMS(ALT1)    |

|        |                 | SD1_DATA2(ALT1)   |

|        | CAPTURE2        | JTAG_TDO(ALT1)    |

|        |                 | SD1_DATA3(ALT1)   |

|        | CLK             | JTAG_MOD(ALT1)    |

|        |                 | SD1 DATA1(ALT1)   |

# 3 Implementation example

This section describes one of the possible combinations specified below. This implementation was tested for the Media Clock Recovery with the NXP GenAVB/TSN stack.

The needed steps are the following:

- 1. Software changes: Configure the GPIO1\_IO05 Pad (TP2120) to the ENET2\_1588\_EVENT0\_OUT signal.

- 2. Software changes: Configure the SD1\_DATA2 Pad (R1728) to the GPT2\_CAPTURE1 signal.

- 3. Hardware changes: Connect R1728 to TP2120 (Refer to <u>Connecting GPT CAPTURE</u> <u>to ENET EVENT OUT</u>).

- 4. Software changes: Configure the JTAG\_MOD Pad (R1023) to the GPT2\_CLK signal.

- Software changes: Configure the JTAG\_TMS Pad (JTAG Pin 7) to the SAI2\_MCLK signal.

- 6. Hardware changes: Connect R1023 to JTAG Pin 7 (Refer to figures <u>Figure 3</u> and <u>Figure 4</u>).

**Note:** Software changes (IOMUX pin control) are implemented in the Board AVB-specific Device Tree.

i.MX6ULL EVK GenAVB/TSN Rework Application Note

Figure 2. Connecting GPT CAPTURE to ENET EVENT OUT

i.MX6ULL EVK GenAVB/TSN Rework Application Note

Figure 3. Connecting AUDIO MCLK to GPT CLK (Top Side)

i.MX6ULL EVK GenAVB/TSN Rework Application Note

Figure 4. Connecting R1023 to JTAG Pin 7

## 4 References

- 1. https://www.nxp.com/docs/en/reference-manual/IMX6ULLRM.pdf

- 2. GenAVB/TSN Stack Evaluation User Guide (GenAVBTSNUG) available on <u>Real Time</u> <u>Edge Software Documentation</u>

AN13678 Application note

#### i.MX6ULL EVK GenAVB/TSN Rework Application Note

# 5 Revision history

#### Table 2. Document revision history

| Revision Number | Date         | Description                                             |

|-----------------|--------------|---------------------------------------------------------|

| 2               | 28 July 2022 | Updated for Real-Time Edge software version 2.3 release |

| 1               | May 2018     | Resistor Number of JTAG_MOD Pad fixed                   |

| 0               | January 2018 | Initial Release                                         |

#### i.MX6ULL EVK GenAVB/TSN Rework Application Note

# 6 Legal information

### 6.1 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

## 6.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Suitability for use in non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <u>PSIRT@nxp.com</u>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

## 6.3 Licenses

ICs with DPA Countermeasures functionality

NXP ICs containing functionality implementing countermeasures to Differential Power Analysis and Simple Power Analysis are produced and sold under applicable license from Cryptography Research, Inc.

### i.MX6ULL EVK GenAVB/TSN Rework Application Note

### 6.4 Trademarks

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

AN13678 Application note

$$\label{eq:NXP} \begin{split} \mathbf{NXP} & - \text{wordmark and logo are trademarks of NXP B.V.} \\ \mathbf{GreenChip} & - \text{ is a trademark of NXP B.V.} \end{split}$$

#### i.MX6ULL EVK GenAVB/TSN Rework Application Note

## Contents

| 2 |

|---|

| 2 |

| 2 |

|   |

| 3 |

| 4 |

| 7 |

| 8 |

| 9 |

|   |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© 2022 NXP B.V.

All rights reserved.

For more information, please visit: http://www.nxp.com

Date of release: 28 July 2022 Document identifier: AN13678