**Application note**

#### **Document information**

| Information | Content                                                                                                                                                                                                                  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | NX30P6093A, high voltage $\rm I^2C$ controlled overvoltage protection load switch with OTG                                                                                                                               |

| Abstract    | The NX30P6093A is a 5.6A I <sup>2</sup> C controlled overvoltage protection load switch for USB Type-C and PD application. It includes undervoltage lockout, overvoltage lockout and overtemperature protection circuits |

**Revision history**

| Rev   | Date     | Description     |

|-------|----------|-----------------|

| v.1.0 | 20220406 | Initial version |

## 1 Scope and setup of the application note

#### 1.1 Scope

This application note discusses the NX30P6093A functions for applications in general and the notes when using this device.

#### **1.2 General setup of the application notes**

The setup of this document is made in such a way, that a chapter or paragraph on a selected subject can be read as a stand-alone explanation with a minimum on cross-references to other document parts or the datasheet. This leads to some repetition of information within the application note and to descriptions or figures that are like the ones published in the NX30P6093A datasheet. In most cases typical values are given to enhance the readability.

**Chapter 2: Introduction and features**

Chapter 3: IC pin overview with a summary of the functions and typical levels

**Chapter 4: Application diagram**

Chapter 5: System description

Chapter 6: Debugging (or starting parts of) an application circuit Chapter 7:

optional circuits and application tricks

Chapter 8: PCB design and layout guidelines

#### 1.3 Related documents and tools

More documents and design tools can be found at the product page of NX30P6093A or are available through the local sales office.

## 2 Introduction

#### 2.1 Introduction

The NX30P6093A is a 5.6A I<sup>2</sup>C controlled overvoltage protection Load switch for USB Type-C and PD applications. It includes undervoltage lockout, overvoltage lockout and overtemperature protection circuits, designed to automatically isolate the power switch terminals when a fault condition occurs. It features input pin impedance detection function, providing USB power supply pin status to system to avoid short circuit damage for the Type-C port power supply pin.

#### 2.2 Features

NX30P6093A has a default overvoltage protection threshold, and the OVLO threshold can be adjusted by both external resistor divider on ADJ pin and internal I<sup>2</sup>C register. A 13ms debounce time is deployed every time before the device is switched ON, followed by a soft start to limit the inrush current.

USB OTG is supported when the plugged accessory is recognized as an OTG device by system and a 5V source is applied on VOUT pin of NX30P6093A. The current capability in USB OTG mode is limited to max 1.5A.

Designed for operation from 2.8V to 20.0V, it can be used in USB Type-C and PD power control applications to offer essential protection and enhance system reliability.

NX30P6093A is offered in a small 20-bump 1.7 x 2.16 mm, 0.4mm pitch WLCSP package.

#### 2.2.1 Key features

- Wide supply voltage range for VIN from 2.8V to 20.0V

- System Power supply VDD from 3.0V to 4.5V

- I<sub>SW</sub> maximum 5.6A continuous current for OVP mode

- Support 1.5A USB OTG

- 29V tolerance on VIN pin

- $16m\Omega$  (typical) ultra-low ON resistance

- Adjustable VIN overvoltage protection by both external resistor and I<sup>2</sup>C

- · Built-in slew rate control for inrush current limit

- · Integrated current source for VIN pin impedance detection

- Protection circuitry

- Overtemperature protection

- Overvoltage protection

- Undervoltage lockout

- Surge protection:

- IEC61000-4-5 exceeds ±100V on VIN

- ESD protection

- IEC61000-4-2 contact discharge exceeds 8kV on VIN

- IEC61000-4-2 air discharge exceeds 15kV on VIN

- HBM ANSI/ESDA/JEDEC JS-001 Class 2 exceeds 3kV on all pins

- MM Class B exceeds 100 V on all the pins

- Specified from -40 °C to +85 °C

# 3 Pin description

| Symbol | Pin                      | Туре      | Description                                                                                                                                                                   |  |  |  |

|--------|--------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| VIN    | B3, B4, B5<br>C3, C4, C5 | Power I/O | Power Input pins, these pins should be connected together on PCB                                                                                                              |  |  |  |

| VOUT   | A3, A4, A5<br>D3, D4, D5 | Power I/O | Power Input pins, these pins should be connected together on PCB                                                                                                              |  |  |  |

| GND    | B2, C2                   | Ground    | Ground pin, these pins should be connected to system ground with good connection for surge protection discharge current                                                       |  |  |  |

| EN     | A1                       | Input     | Enable pin, active low. When it is tied to high, the device enters low power standby mode and VOUT is disconnected from VIN. Internal pull down resistor integrated           |  |  |  |

| INT    | B1                       | Output    | $I^2C\text{-}bus$ interface interrupt to be connected to the $I^2C\text{-}bus$ master of the host processor                                                                   |  |  |  |

| VDD    | C1                       | Power     | System Power supply for chip                                                                                                                                                  |  |  |  |

| SDA    | D2                       | I/O       | I <sup>2</sup> C-bus interface serial data to be connected to the I <sup>2</sup> C-bus master of the host processor                                                           |  |  |  |

| SCL    | D1                       | Input     | I <sup>2</sup> C-bus interface serial clock to be connected to the I <sup>2</sup> C-bus master of the host processor                                                          |  |  |  |

| ADJ    | A2                       | Input     | External OVLO adjust pin. Connect to OVLO resistor divider when select OVLO level by this pin. Connect to ground when it is not used, in this case OVLO determined internally |  |  |  |

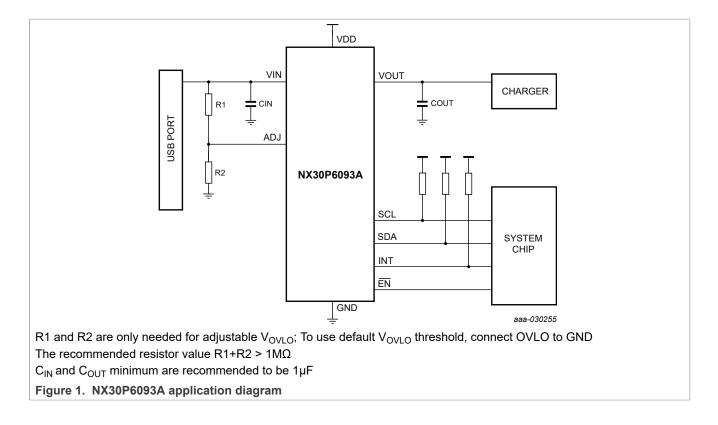

## 4 Application diagram

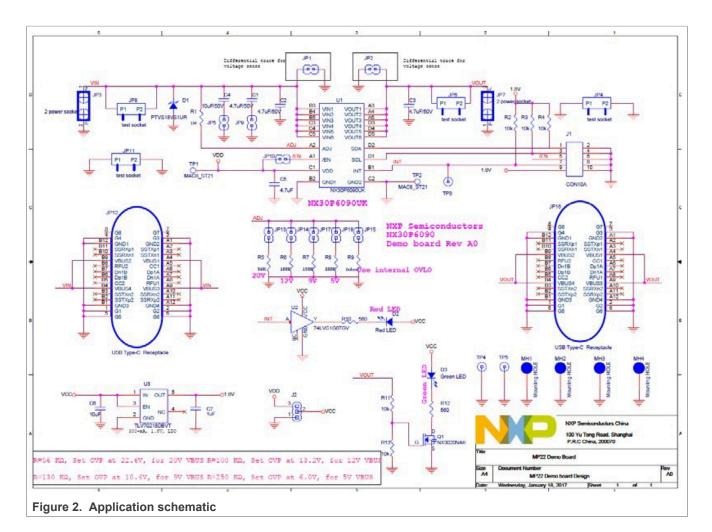

The NX30P6093 is typically used on a USB port charging path in a portable, battery operated device. The I<sup>2</sup>C signals require an external pull-up resistor which should be connected to a supply voltage matching the logic input pin supply level that it is connected to.

When the default internal OVLO threshold is used, the ADJ pin shall be shorted to GND. While OVLO threshold is adjusted by ADJ pin, a resister divider shall be connected.

In order to have better VIN pin impedance detection range, it is recommended that the total resistance of R1 and R2 are larger than  $1M\Omega$ .

For the best performance, it is recommended to keep input and output trace short and capacitors as close to the device as possible. Regarding the thermal performance, it is recommended to increase the PCB area around VIN and VOUT pins.

### NX30P6093A application note

#### NX30P6093A application note

## 5 System description

NX30P6093A is an integrated device with three major functions: programmable overvoltage protection, VIN pin impedance detection and USB OTG. It protects USB Type-C power supply pin and internal system by isolating high voltage when it is exceeds OVLO threshold. The VIN pin impedance detection provides a status monitoring for system to avoid damage by short circuit of USB Type-C power supply pin.

The impedance detection feature is activated when VIN <V<sub>UVLO</sub>, in this case NX30P6093A supplied by system power VDD. When VIN>V<sub>UVLO</sub>, this feature is disabled automatically.

USB OTG is supported when the plugged accessory is recognized as an OTG device by system and a 5V source is applied on VOUT pin of NX30P6093A.

### 5.1 EN input

A HIGH on  $\overline{EN}$  disables the channel MOSFET, all protection circuits, and VIN impedance detection circuits, putting the device into a low power mode. A LOW on  $\overline{EN}$  enables the protection circuits and the MOSFET. There is an internal 1 M $\Omega$  pull-down resistor on

the EN pin to ensure the power switch conducting in a dead-battery situation. A 13ms debounce time has been deployed before device turning on.

### 5.2 OTG mode

USB OTG is supported when the plugged accessory is recognized as an OTG device by system and a 5V source is applied on VOUT pin of NX30P6093A. The  $\overline{EN}$  pin and VOUT\_EN bit in register 0x01 must to be set LOW to support USB OTG mode. If  $\overline{EN}$ pin or VOUT\_EN bit is HIGH, the current is conducted by body diode that will induce much higher power dissipation due to body diode forward voltage and more heating in NX30P6093A. The overtemperature protection will not disable the main switch for the same reason, but only report interrupt to system. In this case, the system should turn off the power source of USB OTG to protect the device and system.

### 5.3 Slew rate tune

The slew rate control is integrated to avoid inrush current when the load switch turns on. It protects the internal circuits or blocks follow NX30P6093A. In order to increase the design flexibility on system level, the slew rate can be tuned through  $I^2C$  through register 0x0F as follows:

| Register Value SRT[2:0] | Switch turn on slew rate (TYP) |

|-------------------------|--------------------------------|

| 000                     | 0.42ms                         |

| 001                     | 0.44ms                         |

| 010                     | 0.5ms                          |

| 011                     | 0.65ms                         |

| 100                     | 0.9ms (Default)                |

| 101                     | 1.5ms                          |

| 110                     | 2.8ms                          |

| 111                     | 5.6ms                          |

Table 2. Slew rate tune setting by I<sup>2</sup>C register

## 5.4 Under-voltage lockout

When EN is LOW and VIN < VUVLO, the under-voltage lockout (UVLO) circuits disable the power MOSFET. Once VIN exceeds VUVLO, if no other protection circuit is active and EN is LOW, the MOSFET is turned on automatically no matter what is the status of VOUT\_EN in register 0x01h. If EN is HIGH, the MOSFET remaining at off and at low power mode.

### 5.5 Over-voltage lockout

When EN is LOW and VIN > VOVLO, the over-voltage lockout (OVLO) circuit will disable the power MOSFET. The OV\_FLG in register 0x03h is set as "1" and an interrupt will be issued to notify the host. Once VIN drops below VOVLO and no other protection circuit is active, the power MOSFET will resume operation.

The OVLO feature can be adjusted by both external resistor divider with ADJ pin and internal I2C register. The sequences are:

When NX30P6093A is powering up, the initial OVLO threshold is set by ADJ pin. If there is a resistor divider connected to ADJ pin, the OVLO threshold is set by resistor divider value; If ADJ is floating or pull to ground, the OVLO threshold is set by default

value. After power up, the OVLO threshold can be adjusted by system through I2C register 0x05h

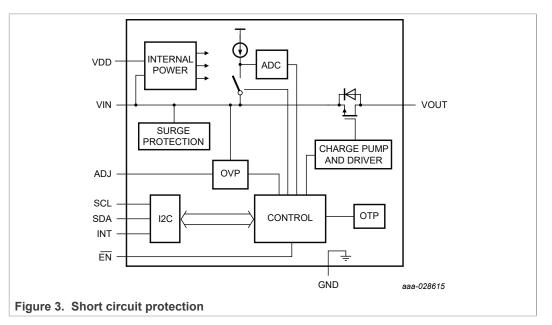

### 5.6 Short circuit protection

NX30P6093A has short circuit protection; after the MOSFET is fully turned on and when the current through it exceeds 10.5A typically, it turns the MOSFET off to protect the device and system. An interrupt is issued when short circuit protection is triggered by setting OC\_FLG as "1" in register 0x03h. Once the short circuit condition is removed and no other protection circuit is active, the state of the N-channel MOSFET is controlled by the EN pin again.

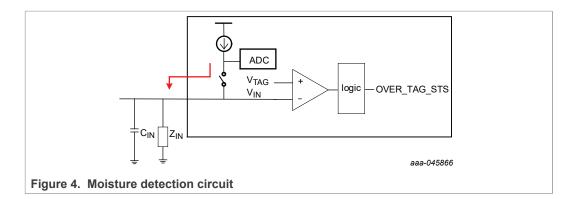

### 5.7 VIN impedance detection

VIN impedance detection function can only begin when EN is LOW and VIN <VUVLO. While in VIN detection mode, at any time when VIN pin exceeds VUVLO, NX30P6093A will exit from VIN detection mode to OVP mode immediately.

With the help of a host, NX30P6093A can start the VIN impedance detection according to the following sequence. First, set both VOUT\_EN and DETC\_EN bit to "1". After wake-up time tWAKEUP, the host must then write ISOURCE, tDET, tDUTY and VTAG voltage from registers 0x06h, 0x07h and 0x09h through I2C.

VIN detection ADC result is valid only after tDET times out, setting TMR\_OUT\_STS to "1" and an interrupt is triggered. The host can also read VIN detected Voltage VIN[7:0] at register 0x08h. At the same time NX30P6093A will compare the detected VIN Voltage against the VTAG Voltage TVIN[7:0] in register 0x09h. When the detected voltage is less than the VTAG voltage, the OVER\_TAG\_STS sets to "1" in register 0x02h and an interrupt is triggered.

### NX30P6093A application note

# 6 Debugging (or starting parts of) an application circuit

#### 6.1 Moisture detection procedure

When abnormal impedance is detected and reported to the system, the OS can show a warning message for end user:

- Unplug any accessory on USB connector

- · Clear the USB connector to remove possible moisture or dust

- 1. Write Enable Register (0x01h), VOUT\_EN=0, DETC\_EN=1; (0x40h)

| 14010 0 |          |      |                |                                                 |    |                                                  |  |  |

|---------|----------|------|----------------|-------------------------------------------------|----|--------------------------------------------------|--|--|

| Bit     | Name     | Туре | Reset<br>Value | Description                                     |    |                                                  |  |  |

| 7       | VOUT_EN  | R/W  | 0h             | 0h = Main switch MOSFET turned on               |    |                                                  |  |  |

|         |          |      |                | 1h = Main switch MOSFET turned off              |    |                                                  |  |  |

| 6       | DETC_EN  | R/W  | ETC_EN R/W 0h  | DETC_EN R/W 0h                                  | 0h | 0h = ISOURCE VIN impedance detection<br>turn off |  |  |

|         |          |      |                | 1h = ISOURCE VIN impedance detection<br>turn on |    |                                                  |  |  |

| 5:0     | Reserved | R/W  | 0h             | 0h = default                                    |    |                                                  |  |  |

#### Table 3. Enable Register (address 0x01h)

Write desired I<sub>SOURCE</sub> (0x06h) = 100μA (0x09h), I<sub>SOURCE</sub> Timing (0x07h) = (0x87h) for t<sub>DET</sub> 100ms (0x8-h), & t<sub>DUTY</sub> 1000ms (0x-7h) and Tag voltage (0x09h) to 2V = (0xBEh) for 256\*(2V/2.7V) = 190 = 0xBE

This is the register to set  $I_{\text{source}}$  value for VIN impedance detection.

| Table 4. | laguran to | register     | (address | 0x06h) |

|----------|------------|--------------|----------|--------|

|          | -source -  | <br>register | 10001033 |        |

| Bit | Name      | Туре | Reset<br>Value | Description                                    |

|-----|-----------|------|----------------|------------------------------------------------|

| 7:4 | Reserved  | R/W  | 0h             | 0h = Default                                   |

| 3:0 | ISRC[3:0] | R/W  | 0h             | I <sub>source</sub> current value setting bits |

This is the register to set I<sub>source</sub> timing for VIN impedance detection.

| Bit | Name      | Туре | Reset<br>Value | Description                                          |

|-----|-----------|------|----------------|------------------------------------------------------|

| 7:4 | TDET[3:0] | R/W  | 0h             | I <sub>source</sub> current pulse width setting bits |

| 3:0 | DUTY[3:0] | R/W  | 0h             | VIN Impedance detection duty cycle setting bits      |

Table 5. Isource timing register (address 0x07h)

This is the register to set the tag of VIN voltage in VIN impedance detection.

Table 6. Set tag on VIN register (address 0x09h)

| Bit | Name      | Туре | Reset<br>Value | Description                                                                                                                                                                                          |

|-----|-----------|------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TVIN[7:0] | R/W  | 00h            | Set tag of VIN voltage bits. The TVIN [7:0]<br>can be calculated as:<br>$TVIN[7:0] = \frac{V_{TAG}}{2.7} \times 256$<br>Where, TVIN is decimal data and should<br>be transfer to binary to TVIN[7:0] |

Poll 3 consecutive times VIN DETECT (0x08h) & Status (0x02h) bit 6 == 1→ MOISTURE DETECTED

This is the register to store the VIN voltage detection results from ADC.

| Bit | Name     | Туре | Reset<br>Value | Description                                                                                                                                                                        |

|-----|----------|------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | VIN[7:0] | R    | 0h             | VIN voltage detection results. The detected VIN voltage can be calculated as:<br>$VIN[7:0] = \frac{V_{DET}}{2.7} \times 256$<br>Where, VIN[7:0] is decimal value of this register. |

Table 7. Voltage on VIN register (address 0x08h)

#### Table 8. Status register (address 0x02h)

| Bit | Name         | Туре | Reset<br>Value | Description                                                                     |

|-----|--------------|------|----------------|---------------------------------------------------------------------------------|

| 7   | PWRON_STS    | R    | 0h             | 0h = VIN voltage less than V <sub>UVLO</sub>                                    |

|     |              |      |                | 1h= VIN voltage larger than V <sub>UVLO</sub> . An interrupt will be issued     |

| 6   | OVER_TAG_STS | R    | Oh             | 0h = VIN detected voltage larger than Tag<br>voltage                            |

|     |              |      |                | 1h = VIN detected voltage less than Tag<br>voltage. An interrupt will be issued |

| 5   | TMR_OUT_STS  | R (  | Oh             | 0h = t <sub>DET</sub> timer is not out                                          |

|     |              |      |                | $1h = t_{DET}$ timer out. An interrupt will be issued                           |

| 4   | SWON_STS     | R    | 0h             | 0h = The main switch is turn off                                                |

### NX30P6093A application note

| Bit | Name     | Туре | Reset<br>Value | Description                                                 |

|-----|----------|------|----------------|-------------------------------------------------------------|

|     |          |      |                | 1h= The main switch is turn on. An interrupt will be issued |

| 3   | OTG_STS  | R    | 0h             | 0h = The device is not in OTG mode                          |

|     |          |      |                | 1h = The device is in OTG mode                              |

| 3:0 | Reserved | R    | 0h             | 0h = default                                                |

Table 8. Status register (address 0x02h)...continued

# 7 Optional circuit and application tricks

## 7.1 NX30P6093A USB OTG

USB OTG is supported when the plugged accessory is recognized as an OTG device by system and a 5V source is applied on VOUT pin of NX30P6093A. The EN pin and VOUT\_EN bit in register 0x01 must to be set LOW to support USB OTG mode. If EN pin or VOUT\_EN bit is HIGH, the current is conducted by body diode that induces much higher power dissipation due to body diode forward voltage and more heating in NX30P6093A. The over temperature protection will not disable the main switch for the same reason, but only report an interrupt to the system. In this case, the system should turn off the power source of USB OTG to protect the device and system.

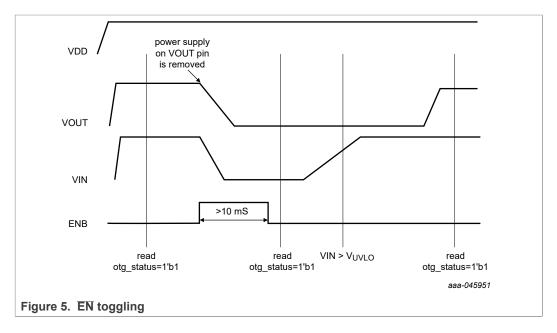

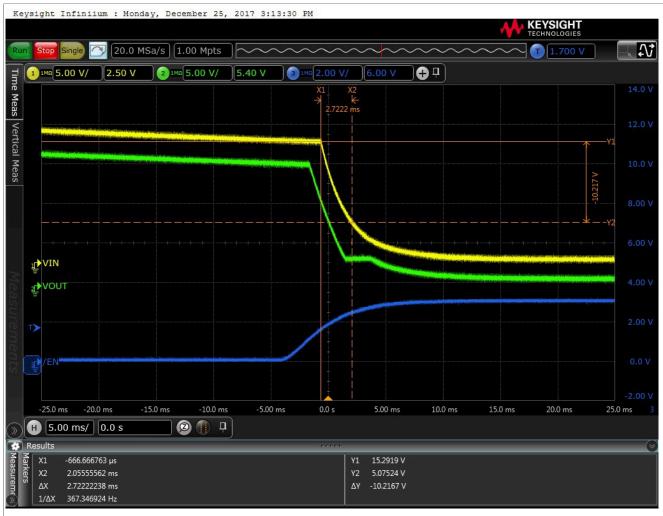

To exit USB OTG mode, it is suggested to use EN toggling. The VIN, along with VOUT, is discharged by internal ~150ohm resistor when NX30P6093A is disabled (EN pulled HIGH) when VDD is present. If the total equivalent capacitance on VIN and VOUT is less than 22uF, the required time of ENB pulling HIGH is 10mS.

Application note

NX30P6093A application note

## 7.2 VIN discharge function

Figure 6. VDD= 3.3V, Load Capacitance = 10uF

#### NX30P6093A application note

Figure 7. VBUS pin going down below Vsafe0V and Vsafe5V after VBUS detached and switch disabled. Maximum 650ms below Vsafe0V, and Maximum 275ms below Vsafe5V

#### NX30P6093A application note

# 8 Legal information

### 8.1 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

## 8.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Suitability for use in non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <u>PSIRT@nxp.com</u>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

## 8.3 Trademarks

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

# **Tables**

| Tab. 1. | Pin description5                          | Tab. 5. | Isource timing register (address 0x07h) 11 |  |  |

|---------|-------------------------------------------|---------|--------------------------------------------|--|--|

| Tab. 2. | Slew rate tune setting by I2C register8   | Tab. 6. | Set tag on VIN register (address 0x09h) 11 |  |  |

| Tab. 3. | Enable Register (address 0x01h)10         | Tab. 7. | Voltage on VIN register (address 0x08h)11  |  |  |

| Tab. 4. | Isource to VIN register (address 0x06h)10 | Tab. 8. | Status register (address 0x02h)11          |  |  |

| Figures |                                           |         |                                            |  |  |

| Fig. 1. | NX30P6093A application diagram6 | 5 |

|---------|---------------------------------|---|

| Fig. 2. | Application schematic           | 7 |

| Fig. 3. | Short circuit protection        | ) |

| Fig. 4. | Moisture detection circuit 10   | ) |

| Fig. 5. | EN toggling13                   | 3 |

| Fig. 6. | VDD= 3.3V, Load Capacitance = 10uF 14  |

|---------|----------------------------------------|

| Fig. 7. | VBUS pin going down below Vsafe0V and  |

|         | Vsafe5V after VBUS detached and switch |

|         | disabled. Maximum 650ms below Vsafe0V, |

|         | and Maximum 275ms below Vsafe5V15      |

## Contents

| 1     | Scope and setup of the application note | 3  |

|-------|-----------------------------------------|----|

| 1.1   | Scope                                   |    |

| 1.2   | General setup of the application notes  | 3  |

| 1.3   | Related documents and tools             | 3  |

| 2     | Introduction                            | 3  |

| 2.1   | Introduction                            | 3  |

| 2.2   | Features                                | 3  |

| 2.2.1 | Key features                            | 4  |

| 3     | Pin description                         | 5  |

| 4     | Application diagram                     | 5  |

| 5     | System description                      | 7  |

| 5.1   | EN input                                | 7  |

| 5.2   | OTG mode                                | 8  |

| 5.3   | Slew rate tune                          | 8  |

| 5.4   | Under-voltage lockout                   |    |

| 5.5   | Over-voltage lockout                    | 8  |

| 5.6   | Short circuit protection                |    |

| 5.7   | VIN impedance detection                 | 9  |

| 6     | Debugging (or starting parts of) an     |    |

|       | application circuit                     | 10 |

| 6.1   | Moisture detection procedure            |    |

| 7     | Optional circuit and application tricks | 13 |

| 7.1   | NX30P6093A USB OTG                      | 13 |

| 7.2   | VIN discharge function                  | 14 |

| 8     | Legal information                       | 16 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© NXP B.V. 2022.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 6 April 2022 Document identifier: AN13609