## AN13592 Application Hints for i.MX RT1040 and i.MX RT1060X Rev. 1 — 19 October 2022

**Application note**

#### **Document information**

| Information | Content                                                                                                                                                                        |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | RT1060X, FlexSPI, 125C                                                                                                                                                         |

| Abstract    | This document focuses on the differences between i.MX RT1040 and i.MX RT1050, and between i.MX RT1060 and i.MX RT1060X. At the same time, it adds some application key points. |

## 1 Introduction

i.MX RT1040 and i.MX RT1060X are new members of i.MX RT family. They feature advanced implementation of the Arm Cortex-M7 core of NXP by extending industrial qual to Tj 125C. To provide high CPU performance and also best real-time response, it retains operation at the speed up to 600 MHz for commercial qual spec and 528 MHz for extended industrial qual spec.

In addition, the new number provides more package options. For details, see the package section in Datasheet.

This document focuses on the differences between i.MX RT1040 and i.MX RT1050, and between i.MX RT1060 and i.MX RT1060X. At the same time, it adds some application key points.

## 2 Comparison between i.MX RT1040 and i.MX RT1050

<u>Table 1</u> lists the key differences between i.MX RT1040 and i.MX RT1050. In conclusion, i.MX RT1040 reduces a few features but provides higher Tj and one more FlexSPI interface.

|                 | i.MX RT1040 | i.MX RT1050 |

|-----------------|-------------|-------------|

| GPIO number     | 108         | 124         |

| CAN-FD          | Y           |             |

| CSI             | _           | Y           |

| KPP             | —           | Y           |

| CCM_CLK1_P/N    | _           | Y           |

| ACMP Output pin | _           | Y           |

| FlexSPI         | 2           | 1           |

| LPSPI           | 3           | 4           |

| Tj (industrial) | 125°C       | 105℃        |

| Package         | BGA169      | BGA196      |

Table 1. Comparison between i.MX RT1040 and i.MX RT1050

## 3 i.MX RT1040 lower cost board design

i.MX RT1040 optimized ball map with MAPBGA169, 0.8 mm pitch and 11 × 11 mm mechanical package. To save board cost by enabling two-layer PCB designs, pay attention to below design points.

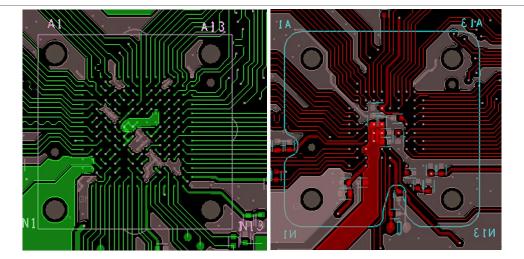

1. The signals of first two rows can fan out on the top layer directly. Other signals can fan out using vias on the bottom layer. Power and ground pin is distributed in the third row. It can fan out directly using a via hole on the bottom layer, as shown in Figure 1.

Figure 1. Top and bottom layer of RT1040-EVK

- 2. USB signal pins are placed in the first row and routed to connector. Keep  $USB_P/N$  connected directly, no layer changed. The default impedance of the differential pair is 90  $\Omega$ .

- 3. The clock of 24 MHz and 32.768 KHz is placed in the first row, connected to crystal with shorter trace length.

- 4. The pitch between pins on the package is 0.8 mm, so vias can be a regular plating hole, 18-mil circle pad and 8-mil drill hole, meeting the capabilities/requirements of all PCB manufacturers.

- 5. The impedance requirement is difficult to control for a two-layer board. To ensure sufficient impedance, place serial resistors and shorter trace stubs for high-speed signals. The resistor values can be adjusted according to the EMC test results. For example, use 47 Ω serial resistors for SDRAM signals.

- 6. Most devices are placed on the top layer, and the bottom layer is used as ground reference layer. It must be GND copper shape as much as possible. Especially between the chip and power supply, sufficient ground return path is required.

- 7. Place layer changes for clocks and sensitive signals near to a ground via or decoupling capacitor.

## 4 Comparison between i.MX RT1060 and i.MX RT1060X

<u>Figure 1</u> lists the key differences between i.MX RT1060X and i.MX RT1060. In conclusion, compared to i.MX RT1060, i.MX RT1060X has a FlexSPI2 dedicated interface, more GPIO pins, and higher Tj.

|                                 | i.MX RT1060 | i.MX RT1060X |

|---------------------------------|-------------|--------------|

| FlexSPI2 dedicated<br>interface | _           | Y            |

| GPIO number                     | 124         | 146          |

| Tj (industrial)                 | 105 ℃       | 125 °C       |

| Package                         | BGA 196     | BGA 225      |

Table 2. Comparison between i.MX RT1060 and i.MX RT1060X

## 5 More GPIOs of i.MX RT1060X

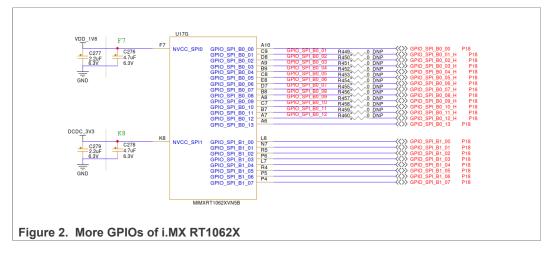

i.MX RT1060X has an additional 22 GPIOs when compared to i.MX RT1060 (added to GPIO10), providing more flexibility for system designs. Those added GPIOs can also be configured as FlexSPI function to interface with different memories. These additional GPIO signal locations are show in Figure 2.

### 6 FlexSPI2 in i.MX RT1060X

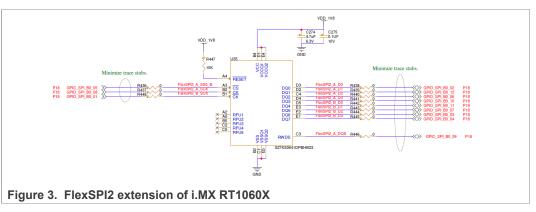

The FlexSPI2 module in i.MX RT1060X parts includes two ports, **Port A** and **Port B**. Each port can operate in quad mode up to 133 MHz. To support Octal devices or HyperBus devices, **Port A** and **Port B** can be combined.

#### Note:

**Port A** of FlexSPI2 can work up to 166 MHz but **Port B** of FlexSPI2 can only work up to 133 MHz.

To use Octal devices or HyperBus devices at a higher frequency than 133 MHz, use FlexSPI1. Details of the FlexSPI2 ports are shown in Figure 3.

Note: To boot from FlexSPI2, set fuse0x6d0[20] to 1.

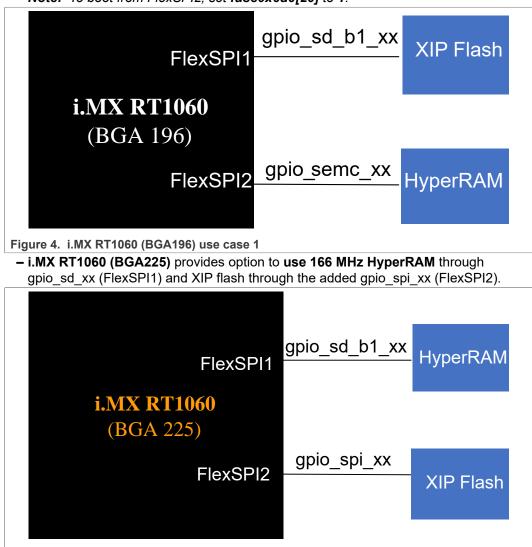

## 7 Use case comparison between RT1060 and RT1060x

- i.MX RT1060 family expansion FLEXSPI USE CASE example 1

- i.MX RT1060 (BGA196) is limited to use XIP flash through gpio\_sd\_xx (FlexSPI1) and ONLY extend 133 MHz HyperRAM through gpio\_semc\_xx (FlexSPI2) because it cannot boot using FlexSPI through gpio\_semc\_xx.

Note: To boot from FlexSPI2, set fuse0x6d0[20] to 1.

Figure 5. i.MX RT1060 (BGA225) use case 1

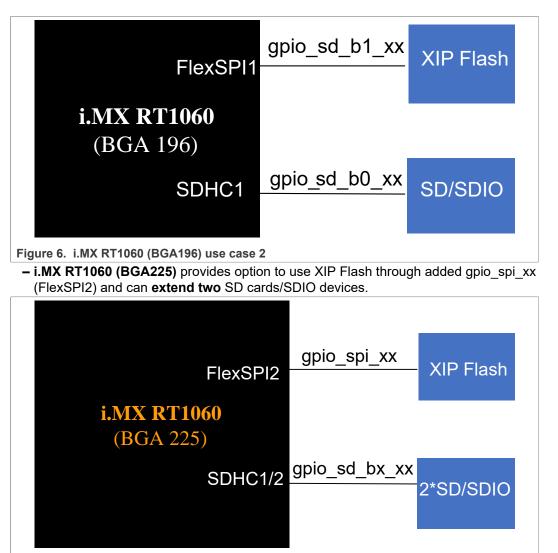

• i.MX RT1060 family expansion – flexspi USE CASE example 2

- i.MX RT1060 (BGA196) is limited to use XIP flash through gpio\_sd\_b1\_xx (FlexSPI1) and can ONLY extend one SD/SDIO device because SDHC2 PINMUX is multiplexed with FlexSPI1.

# AN13592

Application Hints for i.MX RT1040 and i.MX RT1060X

Figure 7. i.MX RT1060 (BGA225) use case 2

## 8 Revision history

| Rev. | Date            | Description                                                                                                                    |

|------|-----------------|--------------------------------------------------------------------------------------------------------------------------------|

| 1    | 19 October 2022 | <ul> <li>Updated <u>Table 1</u></li> <li>Added a note in <u>Section 6</u></li> <li>Added a note in <u>Section 7</u></li> </ul> |

| 0    | 11 March 2022   | Initial release                                                                                                                |

AN13592 Application note

# AN13592

### Application Hints for i.MX RT1040 and i.MX RT1060X

## 9 Legal information

### 9.1 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

### 9.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Suitability for use in non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <u>PSIRT@nxp.com</u>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

### 9.3 Trademarks

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

# AN13592

Application Hints for i.MX RT1040 and i.MX RT1060X

### Contents

| 1 | Introduction                                      | 2 |

|---|---------------------------------------------------|---|

| 2 | Comparison between i.MX RT1040 and<br>i.MX RT1050 | 2 |

| 3 | i.MX RT1040 lower cost board design               |   |

| 4 | Comparison between i.MX RT1060 and                |   |

|   | i.MX RT1060X                                      | 3 |

| 5 | More GPIOs of i.MX RT1060X                        | 4 |

| 6 | FlexSPI2 in i.MX RT1060X                          | 4 |

| 7 | Use case comparison between RT1060 and RT1060x    | 5 |

| 8 | Revision history                                  |   |

| 9 | Legal information                                 |   |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© NXP B.V. 2022.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 19 October 2022 Document identifier: AN13592