# AN12579 Using SLCD controller on K32L2B3 MCU

Rev. 0 — 12/2019

**Application Note**

| 4 Introduction                                                                 | Contents                  |  |  |

|--------------------------------------------------------------------------------|---------------------------|--|--|

| 1 Introduction                                                                 | 1 Introduction1           |  |  |

| We can find customized Segment Liquid Crystal Displays (SLCD) technologies     | 2 Hardware1               |  |  |

| everywhere. For example:                                                       | 3 Basic usgae5            |  |  |

| <ul> <li>in products that measure the PH level of swimming pools.</li> </ul>   | 4 Usage in low power mode |  |  |

| <ul> <li>monitors used to measure specific gases in a mine.</li> </ul>         | 5 Conclusion10            |  |  |

| <ul> <li>in thermometers used to see if a child is running a fever.</li> </ul> | 6 References 10           |  |  |

|                                                                                |                           |  |  |

SLCD is one of the oldest display technologies. It is still one of the most popular technologies, due to the lowest price and power consumption.

Segment LCD displays, also called static displays or glass-only displays, consist of two pieces of Indium Tin Oxide (ITO) glass with a twisted nematic fluid sandwiched in between. A static display is a segment display with one pin for each segment. A segment is any line, dot, or symbol that can be turned on and off independently.

NXP K32L2B3 MCU integrates an SLCD controller module with up to eight backplanes and 47 frontplanes, such as, 8 × 47 or 4 × 51. This document describes the usage of on-chip SLCD controller by enabling an SLCD device, S401M16KR, which is a fourdigit 0.17" seven segment custom LCD panel.

# 2 Hardware

# 2.1 S401M16KR SLCD device

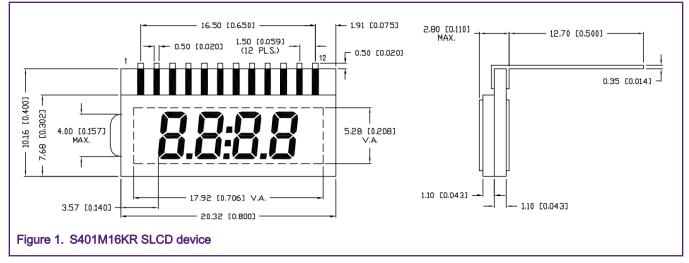

S401M16KR SLCD device contains four digits displayed on the panel. Each digit is shown with seven segments and one dot or colon, as shown in Figure 1.

S401M16KR SLCD device contains four COM pins and eight DATA pins as the control signals. COM pins and data pins control a matrix indicating which segments is ON and others are OFF at a specific time, as shown in Figure 2.

| I Introduction          | 1  |

|-------------------------|----|

| 2 Hardware              | 1  |

| Basic usgae             | 5  |

| Usage in low power mode | 8  |

| 5 Conclusion            | 10 |

| 8 References            | 10 |

|                         |    |

| PIN  | 1    | 2    | 3    | 4    | 5  | 6   | 7  | 8   | 9  | 10  | 11 | 12         |

|------|------|------|------|------|----|-----|----|-----|----|-----|----|------------|

| COMO | COMO | /    | /    | /    | 1D | DP1 | 2D | DP2 | 3D | DP3 | 4D | COL        |

| COM1 | /    | COM1 | /    | /    | 1E | 1C  | 2E | 2C  | 3E | 30  | 4E | 4C         |

| COM2 | /    | /    | COM2 | /    | 1G | 1B  | 2G | 2B  | 3G | 3B  | 4G | 4B         |

| COM3 | /    | /    | /    | COM3 | 1F | 1A  | 2F | 2A  | ЗF | 3A  | 4F | <b>4</b> A |

|      |      |      |      |      |    |     |    |     |    |     |    |            |

### Figure 2. S401M16KR SLCD device

COM pins are enabled one by one for each step. In each step, activated by their own COM pin, the eight data pins are outputting the control level signals to turn on and off the segments. The segments for each COM are ON and OFF line by line. Once the cycle with the four steps runs quickly, some segments are seen ON together, as a whole displaying view (even they are not in the same line in the matrix).

Considering the controlling signals as an activating matrix, see Table 1.

Table 1. Activating metrix for controlling signals

| nCS  | D0 | D1  | D2 | D3  | D4 | D5  | D6 | D7  |

|------|----|-----|----|-----|----|-----|----|-----|

| COM0 | 1D | 1DP | 2D | 2DP | 3D | 3DP | 4D | 4DP |

| COM1 | 1E | 1C  | 2E | 2C  | 3E | 3C  | 4E | 4C  |

| COM2 | 1G | 1B  | 2G | 2B  | 3G | 3B  | 4G | 4B  |

| СОМЗ | 1F | 1A  | 2F | 2A  | 3F | 3A  | 4F | 4A  |

For each digit position, different numbers are assembled by various segments. Figure 3 shows 0-9 numbers in the direct segment way.

Table 2 described the related information.

### Table 2. SLCD digit information

| Number | Segment | COM0 (.D)  | COM1 (CE)  | COM2 (BG)  | COM3 (AF)  |

|--------|---------|------------|------------|------------|------------|

| 0      | ABCDEF  | *D (0 × 1) | CE (0 × 3) | B* (0 × 2) | AF (0 × 3) |

| 1      | BC      | *D (0 × 1) | CE (0 × 3) | B* (0 × 2) | AF (0 × 3) |

| 2      | ABDEG   | *D (0 × 1) | CE (0 × 3) | B* (0 × 2) | AF (0 × 3) |

| 3      | ABCDG   | *D (0 × 1) | CE (0 × 3) | B* (0 × 2) | AF (0 × 3) |

| 4      | BCFG    | *D (0 × 1) | CE (0 × 3) | B* (0 × 2) | AF (0 × 3) |

Table continues on the next page ...

| Number | Segment | COM0 (.D)  | COM1 (CE)  | COM2 (BG)  | COM3 (AF)  |

|--------|---------|------------|------------|------------|------------|

| 5      | ACDFG   | *D (0 × 1) | CE (0 × 3) | B* (0 × 2) | AF (0 × 3) |

| 6      | ACDEFG  | *D (0 × 1) | CE (0 × 3) | B* (0 × 2) | AF (0 × 3) |

| 7      | ABC     | *D (0 × 1) | CE (0 × 3) | B* (0 × 2) | AF (0 × 3) |

| 8      | ABCDEFG | *D (0 × 1) | CE (0 × 3) | B* (0 × 2) | AF (0 × 3) |

| 9      | ABCDFG  | *D (0 × 1) | CE (0 × 3) | B* (0 × 2) | AF (0 × 3) |

| None   | —       | *D (0 × 1) | CE (0 × 3) | B* (0 × 2) | AF (0 × 3) |

| Dot    | DP      | *D (0 × 1) | CE (0 × 3) | B* (0 × 2) | AF (0 × 3) |

Table 2. SLCD digit information (continued)

As shown in Table 2, we can get the code to show different numbers for each period activated by indicated COMx pin.

### We have the code array in source file:

```

#define SLCD ON SHOW COUNT 11u

const uint8 t SLCD NUMBER TABLE[][SLCD COMx COUNT] =

{

/* COM0, COM1, COM2, COM3 */

{ 0x1, 0x3, 0x2, 0x3 }, /* SLCD ON SHOW NUMBER 0 */

{ 0x0, 0x2, 0x2, 0x0 }, /* SLCD ON SHOW NUMBER 1 */

{ 0x1, 0x1, 0x3, 0x2 }, /* SLCD ON SHOW NUMBER 2 */

{ 0x1, 0x2, 0x3, 0x2 }, /* SLCD_ON_SHOW_NUMBER 3 */

{ 0x0, 0x2, 0x3, 0x1 }, /* SLCD ON SHOW NUMBER 4 */

{ 0x1, 0x2, 0x1, 0x3 }, /* SLCD_ON_SHOW_NUMBER_5 */

{ 0x1, 0x3, 0x1, 0x3 }, /* SLCD_ON_SHOW_NUMBER 6 */

{ 0x0, 0x2, 0x2, 0x2 }, /* SLCD_ON_SHOW_NUMBER_7 */

{ 0x1, 0x3, 0x3, 0x3 }, /* SLCD_ON_SHOW NUMBER 8 */

{ 0x1, 0x2, 0x3, 0x3 }, /* SLCD_ON_SHOW_NUMBER_9 */

{ 0x0, 0x0, 0x0, 0x0 }, /* SLCD ON SHOW NONE */

{ 0x2, 0x0, 0x0, 0x0 }, /* SLCD ON SHOW DP */

};

```

### NOTE

The array only contains two pins for each digit. A four-digit parallel can be extended duplicately with eight pins. The following section describes the usage of four digits.

### 2.2 FRDM-K32L2B3 board

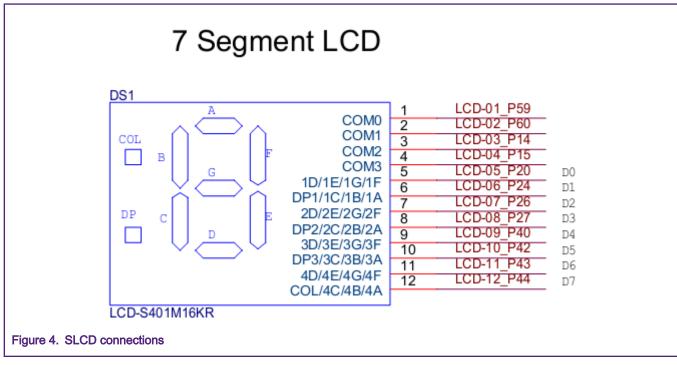

On the FRDM-K32L2B3 board, the SLCD device is connected to the MCU with the pins. The schematic is as shown in Figure 4.

Table 3 shows the functional information about pin settings.

| Functional ID | SLCD pin | MCU pin | ALT  | Comments |

|---------------|----------|---------|------|----------|

| LCD-01        | P59      | PTE20   | ALT0 | COM0     |

| LCD-02        | P60      | PTE21   | ALT0 | COM1     |

| LCD-03        | P14      | PTB18   | ALT0 | COM2     |

| LCD-04        | P15      | PTB19   | ALT0 | СОМЗ     |

| LCD-05        | P20      | PTC0    | ALT0 | D0       |

| LCD-06        | P24      | PTC4    | ALT0 | D1       |

| LCD-07        | P26      | PTC5    | ALT0 | D2       |

| LCD-08        | P27      | PTC6    | ALT0 | D3       |

| LCD-09        | P40      | PTD0    | ALT0 | D4       |

| LCD-10        | P42      | PTD2    | ALT0 | D5       |

| LCD-11        | P43      | PTD3    | ALT0 | D6       |

| LCD-12        | P44      | PTD4    | ALT0 | D7       |

Considered as a bus, the data signals are assembled by eight separated pins, named from **D0** to **D7**. The coding is performed to control these signals and the signals from each pin are seen as a whole data through the bus.

To operate all the control signals like a bus, the signal indexes are arranged into two arrays in the source code:

```

/* Define the sync bus and the data bus. */

#define SLCD_COMx_COUNT 4u

#define SLCD_DATA_BUS_WIDTH 8u

/* Define the pins for sync bus and data bus. */

```

```

Basic usgae

```

```

const uint8 t SLCD PIN COMx[SLCD COMx COUNT] =

{

59, /* COM0. */

60, /* COM1. */

14, /* COM2. */

15 /* COM3. */

};

const uint8 t SLCD PIN DATA[SLCD DATA BUS WIDTH] =

{

20, /* D0. */

24, /* D1. */

26, /* D2. */

27, /* D3. */

40, /* D4. */

42, /* D5. */

43, /* D6. */

44 /* D7. */

};

```

# 3 Basic usgae

The SLCD controller on K32L2B is easy to use. After enabling clock and setting up pin mux functions, for the basic usage without the blink and fault detection feature, only one control register, LCD General Control Register (LCD\_GCR), is necessary for initializing the controller. The following provides a group of typical settings:

```

/* Setup slcd controller. */

LCD->GCR = LCD GCR DUTY(3) /* Selects the duty cycle of the LCD controller driver. 3: 4 COMx

lines. */

| LCD GCR LCLK(2)

/* Clock divider for clock source. 0-7 */

| LCD_GCR_SOURCE(0) /* LCD clock source. 1:use MCGIRCLK. 0:OSC32K */

| LCD_GCR_LCDEN(0)  /* Disable the controller during setting. */

| LCD_GCR_LCDSTP(0)  /* Keep LCD module alive in STOP modes. */

| LCD GCR LCDDOZE(1) /* Keep LCD module alive in DOZE mode. */

| LCD GCR FFR(0) /* Select the frame rate mode. 0:standard frame rate. */

| LCD GCR ALTSOURCE(0) /* Select the alternate clock source. no available when using default

clock source.*/

| LCD GCR_ALTDIV(0)

/* Clock divider for alternate clock source. no available when using

default clock.*/

/* Enables an LCD interrupt event when fault detection is completed.

| LCD GCR FDCIEN(0)

*/

| LCD GCR PADSAFE(0)

/* Force safe state on LCD pad control, locking all LCD control bits.

*/

| LCD GCR VSUPPLY(0)

/* Select the power voltage supply. 0: from internal Vdd. */

LCD_GCR_LADJ(1)

/* Configures SLCD to handle different LCD glass capacitance.*/

| LCD GCR CPSEL(1)

/\star Selects the LCD controller charge pump or a resistor network to

supply the LCD voltages V LLx. */

| LCD GCR RVTRIM(8) /* Regulated Voltage Trim. no available when disabled.*/

| LCD GCR RVEN(0)

/* Regulated Voltage Enable. disabled. */

```

The pins on the MCU are required to be mapped to the SLCD control bus for COMX signals and DX signals.

- The mappings of the COMX signals are configured as the back panel pins.

- The mappings of the Dx signals are configured as the front panel pins.

- The used pins are initialized with the LCD Pin Enable registers (LCD\_PEN0, LCD\_PEN1), LCD Back Plane Enable registers (LCD\_BPEN0, LCD\_BPEN1), while LCD\_PENx enables all the pins in use and LCD\_BPENx selects them as front panel or back panel.

• LCD WF8Bx registers are for signal timing sequence of each pin.

The following describes the usage of LCD WF8Bx registers:

- Each register in the LCD\_WF8Bx array is for one LCD signal pin. The index of the array is also for the functional pin of the SLCD module. For example, LCD WF8B[59] is for the signal pin of the SLCD module, LCD P59.

- Each bit in the LCD\_WF8Bx register is for Step 1, while the index of bit is also for Step 1. For example, the bit 2 in LCD\_WF8B[59] responds to the believer of LCD\_P59 when in Step 2 of the whole cycle (including four steps or eight steps).

In the software, controlling the data signals is a little different from the hardware. The software searches the data for the parallel pins first, and then arrange the data timing sequence. However, the hardware searches the data timing for each pin first, and then assemble the parallel pins into bus with 8-bit width. Therefore, a converting function is designed in the source code project.

```

/**

* @brief Set the data on SLCD control bus

\star @param com idx The index of step (COMx), 0-3.

* @param show dat The display code to the bus for current step.

*/

void slcd_set_bus_data(uint8_t com_idx, uint8_t show_dat)

{

uint8 t bit mask = (1u << com idx);</pre>

for (uint8 t i = Ou; i < SLCD DATA BUS WIDTH; i++)

{

if (show dat & 0x1)

{

LCD->WF8B[SLCD_PIN_DATA[i]] |= bit_mask;

}

else

{

LCD->WF8B[SLCD PIN DATA[i]] = ~bit mask;

}

show_dat >>= lu;

}

}

```

An API function is created to assemble the segment codes into the displaying matrix for the four digits. With this API, the complex matrix conversion is not required. You just need to tell the MCU which number you want to show and in which position you want it to be, as the software handles all the conversion automatically.

```

/* keep the unchanged displaying code in the matrix. */

static uint8 t slcd on show numbers[SLCD COMx COUNT];

/**

* @brief Set the displaying number in the digital position of SLCD device.

* @param index The index of digital position, 0-3.

* @param number The value of showing number, 0-10, while 10 is "none".

* @param en dp Enable showing the dop in current digital positon, true or false.

*/

void slcd set number(uint8 t index, uint8 t number, bool en dp)

{

uint8 t tmp8 = 0u;

for (uint8_t i = 0u; i < SLCD_COMx_COUNT; i++)</pre>

tmp8 = slcd on show numbers[i] & (~(0x3 << (2 * index))); /* clear old setting code.*/</pre>

tmp8 |= (SLCD_NUMBER_TABLE[number][i] << (2 * index)); /* add new setting code. */</pre>

if (en dp)

{

tmp8 |= SLCD NUMBER TABLE[SLCD ON SHOW NUMBER DP][i] << (2 * index); /* add new setting</pre>

```

```

for dot point. */

}

slcd_on_show_numbers[i] = tmp8;

slcd_set_bus_data(i, slcd_on_show_numbers[i]);

}

}

```

In the application main () function, the source code to show the changing numbers on the target SLCD is as below:

```

int main (void)

{

bool en_dp;

/* init board hardware. */

BOARD InitPins();

BOARD BootClockRUN();

BOARD InitDebugConsole();

PRINTF("slcd basic example.\r\n");

/* init the clock and pins for slcd, setup the controller for slcd. \star/

slcd init();

en dp = false;

while (1)

{

for (uint8 t i = 0u; i < SLCD ON SHOW COUNT; i++)

{

GETCHAR();

slcd_stop(); /* stop the slcd controller before updating displaying. */

slcd_set_number(0, i , en_dp);

slcd_set_number(1, (i+1)%SLCD_ON_SHOW_COUNT, en_dp);

slcd set number(2, (i+2)%SLCD ON SHOW COUNT, en dp);

slcd set number(3, (i+3)%SLCD ON SHOW COUNT, en dp);

slcd start();

}

en_dp = !en_dp;

}

}

```

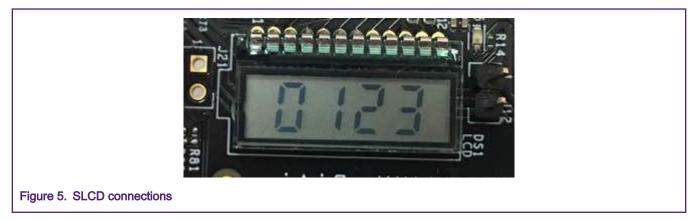

Download the project and run it on the FRDM-K32L2B board. The numbers are displayed on the SLCD, as shown in Figure 5.

For the whole runnable source code project, slcd\_basic, see to the attached code package

# 4 Usage in low power mode

On the MCU with SLCD controller, the SLCD controller is specially supported by some extra low power STOP modes. In these modes, almost all the hardware are powered off to same energy. The SLCD controller controls its pins to refresh the SLCD device, to keep it displaying on the panel.

The SLCD can work in almost all the power mode except the VLLS0 mode. For details, refer to the **Power Management** chapter in User Manual.

### Table 4. SLCD in low power mode

| Modules     | VLPR                            | VLPW | Stop                            | VLPS            | LLS             | VLLSx                               |

|-------------|---------------------------------|------|---------------------------------|-----------------|-----------------|-------------------------------------|

| Segment LCD | FF Async<br>operation in<br>CPO | FF   | Async operation<br>FF in PSTOP2 | Async operation | Async operation | Async<br>operation, OFF<br>in VLLS0 |

The critical settings to keep the SLCD working in low power modes are:

- Clock source: Make sure that the clock source for SLCD controller is still alive in the target low power mode. For example, if the clock source of the SLCD controller is 32 K OSC, this clock source is enabled in every mode, even low in the VLLSx mode.

- **Pin mux**: Make sure that the used pins for SLCD controller are configured as analog function (ALT0) and the pins of the other (digital) functions are locked (the voltage level can not be changed) in VLLSx mode. Only when the pins of the SLCD controller are active, the SLCD controller outputs the waves and the SLCD panel keeps displaying the digits.

- The low power mode of the SLCD controller: Enable the lower power support of the SLCD controller by setting LCD\_GCR[LCDSTP] bit and LCD\_GCR[LCDDOZE] bit as 0s, to keep the SLCD controller still working in STOP and WAIT modes.

After completing the parameters above, set the SLCD controller for displaying and then enter the lower power STOP mode. In the lower power STOP modes, the displaying on the SLCD panel is ON, as the SLCD controller is still outputting the refresh waves.

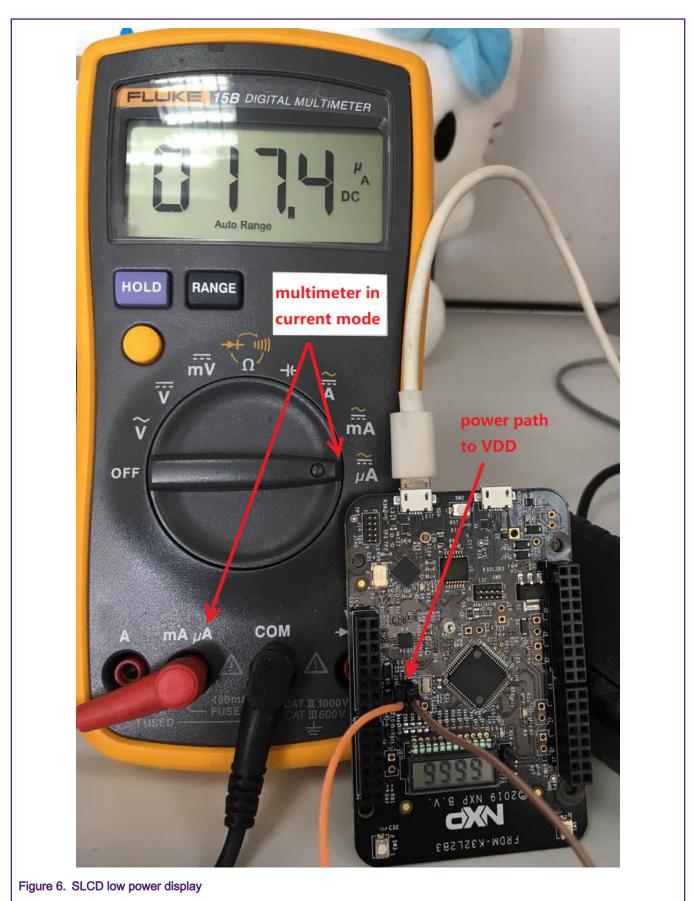

In the example project shown in Figure 6, in the VLLS3 mode, with RTC and SLCD controller running, the measuring current on FRDM-K32L2B board is as low as about 7 uA.

For the whole runnable source code project, slcd\_low\_power, see the attached code package.

# 5 Conclusion

This document descibes basic usages of on-chip SLCD controller on K32L2B MCU, with the example projects based on the FRDM-K32L2B board. The SLCD controller can control the SLCD device to display the contents on its panel automatically with suitable configurations on the hardware. Even in the low power modes, the SLCD controller can still work with very low energy. It indicates that the K32L2B with on-chip SLCD controller can be used in the energy-sensitive application field.

# 6 References

https://focuslcds.com/segment-lcd/

How To Reach Us

Home Page:

nxp.com

Web Support:

nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/ SalesTermsandConditions.

While NXP has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities on customer's applications and products, and NXP accepts no liability for any vulnerability that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorlQ, QorlQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamIQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro,  $\mu$ Vision, Versatile are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

#### © NXP B.V. 2019.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

> Date of release: 12/2019 Document identifier: AN12579