## **AN12398**

# **EdgeLock SE05x Quick start guide with Visual Studio project examples**

Rev. 2.5 — 12 September 2022 534625

**Application note**

#### **Document information**

| Information | Content                                                                                                                                                                                                                                                                                                  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | EdgeLock SE05x, EdgeLock SE05x Plug & Trust Middleware, Visual Studio projects                                                                                                                                                                                                                           |

| Abstract    | This document explains how to get started with EdgeLock SE05x Plug & Trust middleware using the Visual Studio project examples. It provides detailed instructions to run the Microsoft Visual Studio projects using the CMake-based build system included in the EdgeLock SE05x Plug & Trust middleware. |

## EdgeLock SE05x Quick start guide with Visual Studio project examples

## **Revision history**

#### **Revision history**

| Revision number | Date       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0             | 2019-06-08 | First document release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.1             | 2019-06-20 | Update of board figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.0             | 2019-11-25 | Update of CMake buld system materials                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.1             | 2019-12-17 | Corrected OM-SE05xARD J14 jumper setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.2             | 2020-11-19 | Update for EdgeLock SE051                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.3             | 2020-12-07 | Updated to the latest template and fixed broken URLs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.4             | 2022-06-02 | Add EdgeLock SE050E and EdgeLock A5000 product variants.  Update Table 1, Figure 1, Figure 2, Figure 3, Figure 5, Figure 6, Figure 7, Figure 8, Figure 9, Figure 10, Figure 11, Figure 12, Figure 13, Figure 14, Figure 15, Figure 16, Figure 17, Figure 18, Figure 19, Figure 20, Figure 21, Figure 22, Figure 23, Figure 31, Figure 32, Figure 33, Figure 34, Figure 35, Figure 36, Figure 44 and Figure 45.  Add Section Section 5 Product specific CMake build settings.  Add Section Binding EdgeLock SE05x to a host using Platform SCP Binding EdgeLock SE05x to a host using Platform SCP.  Update tool versions in Section 7, Section 8 and Section 9.  Moved section "Update FRDM-K64F board with DAPLink firmware" into Section 10. |

| 2.5             | 2022-07-04 | Update to EdgeLock SE Plug & Trust Middleware version 04.02.xx.  Update Section Section 5 Product specific CMake build settings.  Update Section Binding EdgeLock SE05x to a host using Platform SCP Binding EdgeLock SE05x to a host using Platform SCP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

EdgeLock SE05x Quick start guide with Visual Studio project examples

#### 1 How to use this document

The Plug & Trust middleware package is delivered with the CMake files that include the set of directives and instructions describing the project's source files and targets. The CMake architecture allows developers to build files for their platform and native build environment and run exactly the same project example on PC/Windows/Linux and embedded targets.

This document provides detailed instructions to run Visual Studio examples provided in the Plug & Trust middleware using FRDM-K64F and OM-SE05xARD boards. The main body of this document should be used in this sequence:

- 1. Order board samples. <u>Section 2</u> contains the ordering details of the boards required in this document

- 2. Setup your boards. <u>Section 3</u> describes how to setup the OM-SE05xARD and FRDM-K64F boards.

- 3. Run project examples. Go to <u>Section 4</u> for instructions to import and run EdgeLock SE05x Visual Studio project examples.

Supplementary material has been provided in the appendices.

EdgeLock SE05x Quick start guide with Visual Studio project examples

## 2 Hardware required

The EdgeLock SE05x works as an auxiliary security device attached to a host controller, communicating with through an I<sup>2</sup>C interface. To follow the instructions provided in this document, you need an EdgeLock SE05x development board and a FRDM-K64F MCU board, acting as a host controller.

#### EdgeLock SE05x development boards ordering details

The EdgeLock SE05x and EdgeLock A5000 product support packages are providing development boards for evaluating EdgeLock SE05x and EdgeLock A5000 features. Select the development board of the product you want to evaluate. Table 1 details the ordering details of the EdgeLock SE05x and EdgeLock A5000 development boards.

Table 1. EdgeLock SE05x development boards.

| Part number   | 12NC           | Description                                | Picture |

|---------------|----------------|--------------------------------------------|---------|

| OM-SE050ARD-E | 9354 332 66598 | SE050E Arduino® compatible development kit |         |

| OM-SE050ARD-F | 9354 357 63598 | SE050 Arduino® compatible development kit  |         |

| OM-SE050ARD   | 9353 832 82598 | SE050F Arduino® compatible development kit |         |

| OM-SE051ARD   | 9353 991 87598 | SE051 Arduino® compatible development kit  |         |

| OM-A5000ARD   | 9354 243 19598 | A5000 Arduino® compatible development kit  |         |

**Note:** The pictures in this guide will show SE050E, but all boards in <u>Table 1</u> can be used as well with the same hardware configuration.

#### FRDM-K64F MCU board ordering details

<u>Table 2</u> details the ordering details for the FRDM-K64F board.

## EdgeLock SE05x Quick start guide with Visual Studio project examples

Table 2. FRDM-K64F details

| Part number | 12NC         | Content                                                                 | Picture |

|-------------|--------------|-------------------------------------------------------------------------|---------|

| FRDM-K64F   | 935326293598 | Freedom development<br>platform for Kinetis<br>K64, K63 and K24<br>MCUs |         |

EdgeLock SE05x Quick start guide with Visual Studio project examples

### 3 Boards setup

This section explains how to prepare the OM-SE05xARD boards and FRDM-K64F board to run the Plug & Trust middleware project examples. This consists of:

- 1. OM-SE05xARD jumper configuration.

- 2. OM-SE05xARD and FRDM-K64F board connection.

**Note:** If your FRDM-K64F board does not already contain the DAPLink firmware, you need to update the FRDM-K64F board as described in Section 10.

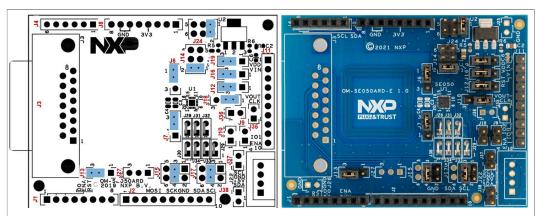

### 3.1 OM-SE05xARD jumper configuration

The OM-SE05xARD boards have jumpers that allow you to configure the I<sup>2</sup>C interface of EdgeLock SE05x secure elements via the Arduino header. Configure the jumper settings as shown in Figure 1 to enable this option.

**Note**: For more information about the jumper settings, refer to <u>AN13539</u> OM-SE05xARD hardware overview.

Figure 1. Jumper configuration for FRDM-K64F

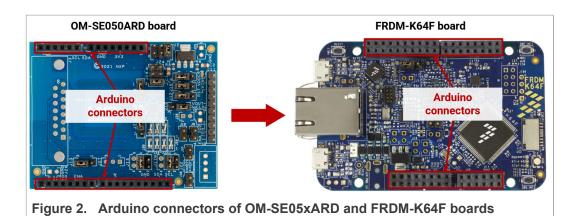

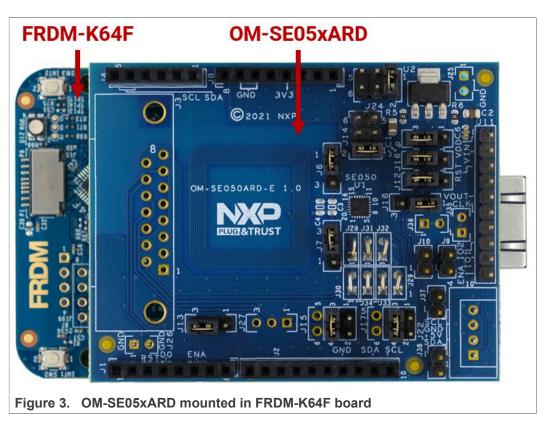

#### 3.2 OM-SE05xARD and FRDM-K64F board connection

The OM-SE05xARD boards and FRDM-K64F board can be directly connected using the Arduino connectors. The OM-SE05xARD boards come with male connectors while the FRDM-K64F board comes with female headers.

Mount any OM-SE05xARD board on top of the FRDM-K64F as shown in Figure 2:

EdgeLock SE05x Quick start guide with Visual Studio project examples

Double check that the two boards are connected as shown in Figure 3:

**Note:** Refer to Figure 1 for OM-SE05xARD jumper configuration.

#### 3.3 Flash FRDM-K64F with VCOM software

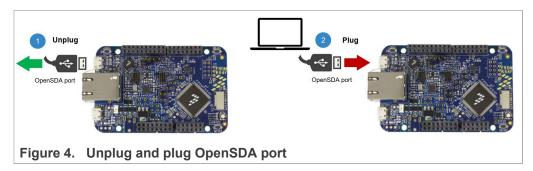

The VCOM software allows the FRDM-K64F board to be used as a bridge between the Windows machine and the EdgeLock SE05x and enables the execution of the EdgeLock SE05x ssscli tool and other utilities from the laptop. To flash the VCOM software into the FRDM-K64F, follow these steps:

#### EdgeLock SE05x Quick start guide with Visual Studio project examples

1. Unplug and plug again the USB cable to the openSDA USB port as shown in Figure 4:

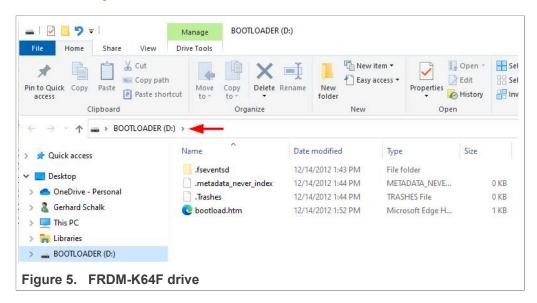

2. When you plug the board, your laptop should recognize the board as an external drive as shown in Figure 5:

#### EdgeLock SE05x Quick start guide with Visual Studio project examples

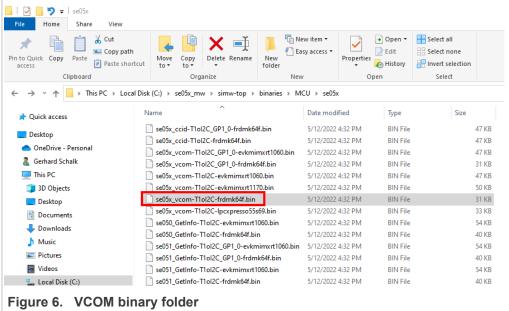

3. Flash the VCOM software to FRDM-K64F. The VCOM software binary can be found in the Plug & Trust middleware package, inside the simw-top\binaries folder as shown in Figure 6:

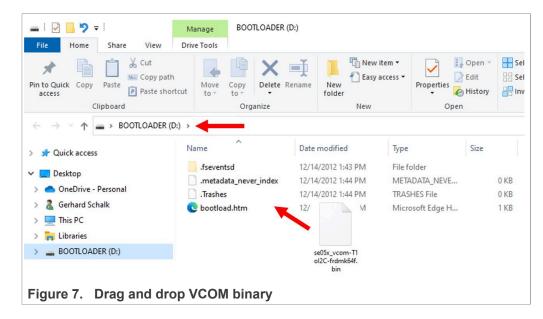

4. Drag and drop or copy and paste the a7x vcom-T1oI2C-frdmk64f-SE050x.bin file into the FRDM-K64F drive from your computer file explorer as shown in Figure 7:

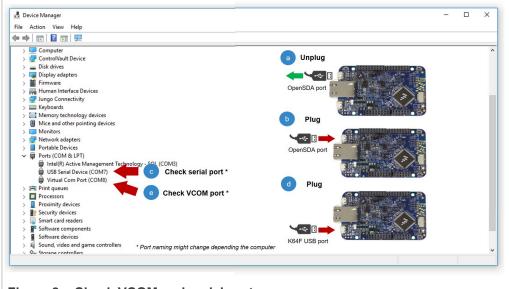

- 5. The serial and VCOM ports should be recognized by your Device Manager. To check that the ports are recognized, follow the steps indicated in Figure 8:

- a. Unplug the USB cable from the OpenSDA USB port.

- b. Plug the USB cable to the OpenSDA USB port.

- c. Check that the serial port is recognized in the category Ports (COM & LTP). In this document, it is recognized as USB Serial Device (COM7) but this naming

AN12398

#### EdgeLock SE05x Quick start guide with Visual Studio project examples

- might change depending on your computer. Therefore, it is important that you identify which device is recognized at the moment you plug the SDA USB port to the computer.

- d. Plug the USB cable to the K64F USB port.

- e. Check that the VCOM port is recognized in the category **Ports** (**COM & LTP**). In this document, it is recognized as *Virtual Com Port* (**COM8**) but this naming might change depending on your computer (e.g. It could also appear named as *USB Serial Device*). Therefore, it is important that you identify which device is recognized at the moment you plug the K64F USB port to the computer.

Figure 8. Check VCOM and serial ports

EdgeLock SE05x Quick start guide with Visual Studio project examples

#### Run Plug & Trust middleware Visual Studio project examples 4

This section explains how to run Plug & Trust middleware Visual Studio project examples using the CMake-based build system.

#### 4.1 Prerequisites

The following tools are required to run the Plug & Trust middleware Visual Studio projects:

- 1. Install Visual Studio ≥ 2017 version, or higher, in your laptop. For reference, Section 7 illustrates how Visual Studio 2022 version can be installed, but the same procedure can be applied for more recent versions.

- 2. Install CMake. For reference, Section 8 illustrates the detailed installation instructions.

- 3. Install Python Python ≥ 3.7.x and ≤ 3.9.x 32-bit version, in your laptop. For reference, Section 9 illustrates how Python 3.7.x 32-bit version can be installed, but the same procedure can be applied for more recent versions.

#### 4.2 Download Plug & Trust middleware

Follow these steps to download the Plug & Trust middleware in your local machine:

- 1. Download Plug & Trust middleware from the NXP website.

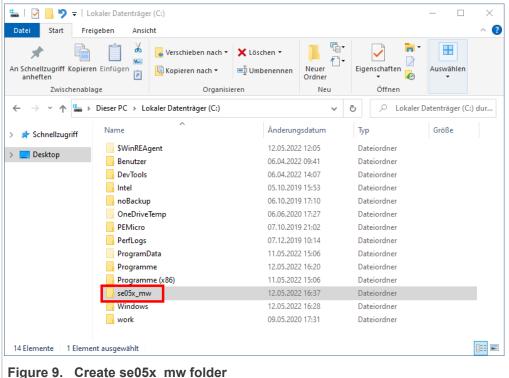

- 2. Create a folder called **se05x mw** in C: directory as shown in Figure 9:

#### EdgeLock SE05x Quick start guide with Visual Studio project examples

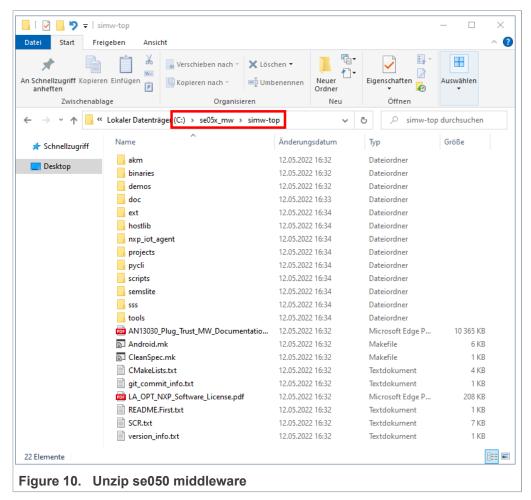

3. Unzip the Plug & Trust middleware inside the *se05x\_mw* folder. After unzipping, you will see a folder called *simw-top* created. The contents of the *simw-top* directory should look as shown in Figure 10:

**Note:** It is recommended to keep  $se05x\_mw$  with the **shortest** path possible and **without spaces** in it. This avoids some issues that could appear when building the middleware if the path contains spaces.

#### 4.3 Build Plug & Trust middleware project examples

The Plug & Trust middleware uses CMake for building the project examples into your local machine. To build Plug & Trust middleware, open a Command Prompt and use the following steps as shown in <u>Figure 12</u>:

- 1. Go to folder with the unzipped SE050 middleware:

- (1) Send >> cd C:\se05x\_mw\simw-top\scripts

#### EdgeLock SE05x Quick start guide with Visual Studio project examples

- 2. Define the environment:

- (2) Send >> env setup.bat

Figure 11. Generate Plug & Trust middleware define the environment

Depending on your PC installation you may need to update the application file locations within the <code>env setup.bat</code> file.

- 3. Generate the Plug & Trust middleware project examples:

- (3) Send >> python create cmake projects.py

**Note**: This command may take a few seconds to complete.

```

C:\se05x_mw\simw-top\scripts:python create_cmake_projects.py

Could not find '"C:\Program Files\CMake\bin'\cmake.exe'. Assuming 'cmake.exe' is in path and running.

INFO:_main__:Preprocessing C:\se05x_mw\simw-top\scripts241/tools/schema/Opc.Ua.NodeSet2.Minimal.xml

INFO:_main__:Preprocessing C:\se05x_mw\simw-top\scripts241

INFO:_main__:Generating Code for Backend: open62541

INFO:_main__:NodeSet generation code successfully printed

### Connect to Secure Element from PC

### Connect from PC

### Connect

```

Figure 12. Generate Plug & Trust middleware project examples

#### EdgeLock SE05x Quick start guide with Visual Studio project examples

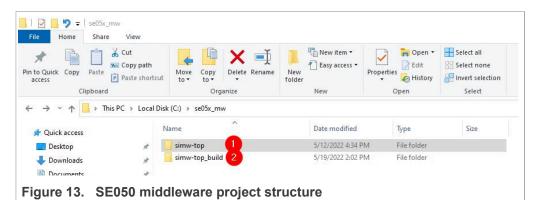

4. Your project directory should now contain two folders: a (1) simw-top folder and a (2) simw-top build folder as shown in Figure 13:

## 4.4 Execute EdgeLock SE05x Visual Studio project examples

This section explains how to run the Plug & Trust middleware project example called  $se05x\_minimal$ . The  $se05x\_minimal$  project outputs the memory left in EdgeLock SE05x security IC.

**Note:** The execution of the  $se05x\_minimal$  project is shown as an example. The steps detailed in this section can be replicated to run any other project example included as part of the Plug & Trust middleware.

To execute the se05x minimal test example, follow these steps:

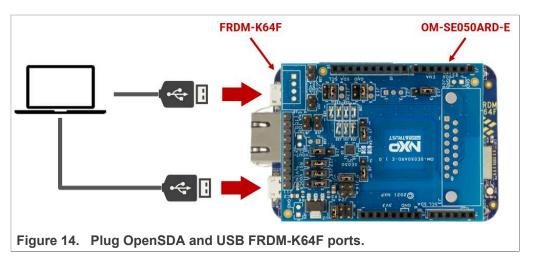

Connect the FRDM-K64F board to your laptop as shown in <u>Figure 14</u>. Check that your Windows Device Manager recognizes FRDM-K64F board as shown in <u>Figure 8</u>. Refer to <u>Figure 1</u> for OM-SE05xARD jumper configuration.

#### EdgeLock SE05x Quick start guide with Visual Studio project examples

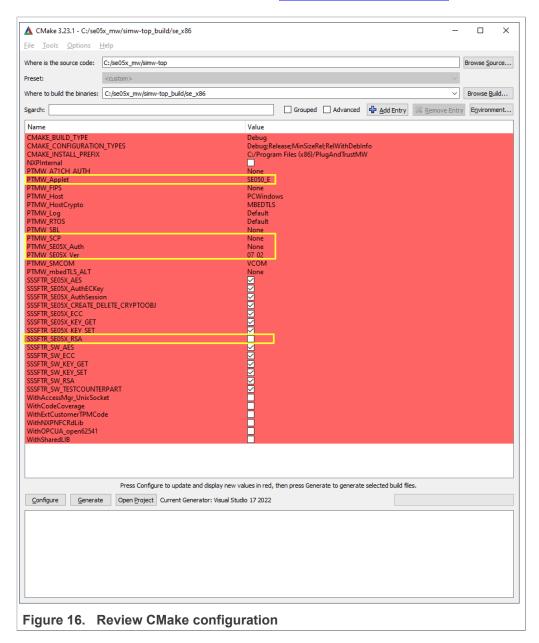

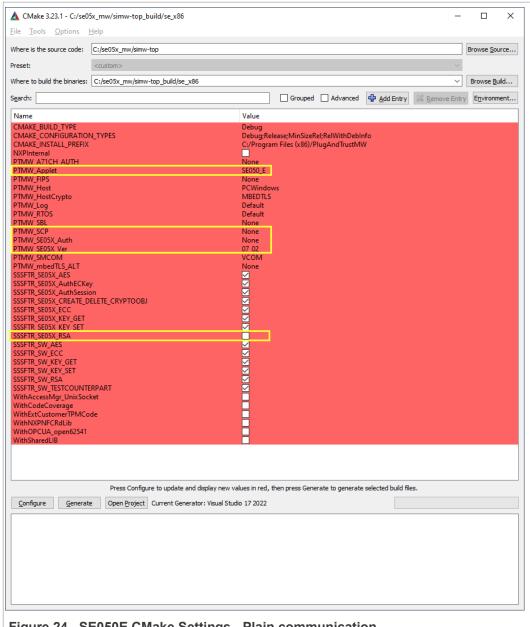

- 2. Open the CMake configuration menu as shown in <u>Figure 15</u> and ensure that all the flags are set properly for your use case.

- a. Open a command prompt and go to the directory where the Plug & Trust middleware is built.

Send: cd C\se05x mw\simw-top build\se x86

b. Open the cmake configuration interface.

Send: cmake-gui .

#### EdgeLock SE05x Quick start guide with Visual Studio project examples

development board or a different secure element product IC. The settings are described in <u>Section 5</u>. The default SE050E settings are shown in <u>Figure 16</u>. In this example we use plain communication. Plain communication for the example execution is enabled by selecting the following options:

- Select None for the CMake option PTMW SE05X Auth.

- Select None for the CMake option PTMW SCP.

How to enable Platform SCP is described in How to enable Platform SCP.

If you have edited any of the parameters in the menu, before exiting press the buttons **Configure** and **Generate** to apply the changes.

For more information about the CMake options please refer the CMake section of Plug & Trust middleware documentation: simw-top/doc/scripts/cmake options.html

AN12398

#### EdgeLock SE05x Quick start guide with Visual Studio project examples

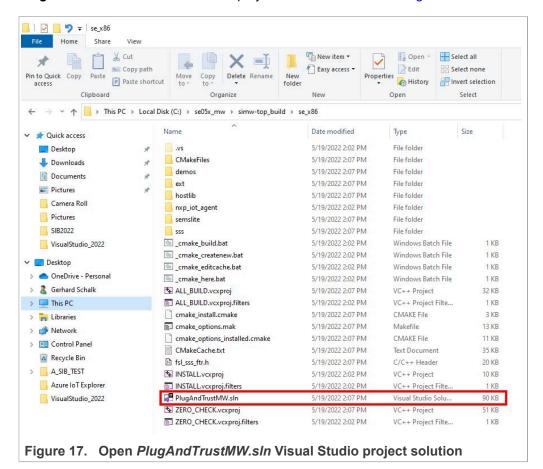

3. Go to the C:\se05x\_mw\simw-top\_build\se\_x86 directory. Double click the *PlugAndTrustMW.sIn* Visual Studio project solution as shown in <u>Figure 17</u>:

#### EdgeLock SE05x Quick start guide with Visual Studio project examples

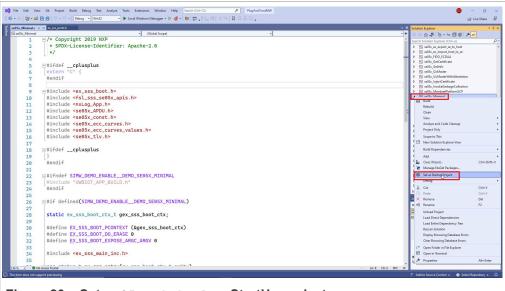

4. The Visual Studio IDE will open with the Plug & Trust middleware project examples included in the workspace as can be seen in <a href="Figure 18">Figure 18</a>:

Figure 18. PlugAndTrustMW.sln Visual Studio project workspace

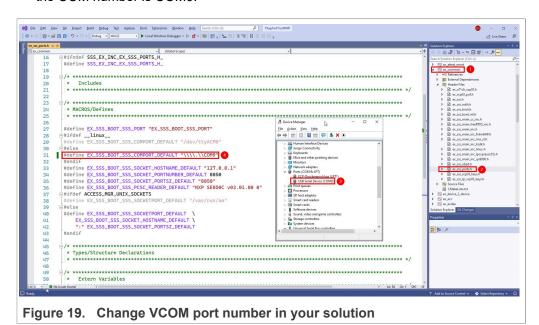

- 5. Change the VCOM port number in the Plug & Trust middleware project. To do so, follow the instructions shown in Figure 19:

- a. Go to the <code>ex\_common</code> project and open the <code>ex\_sss\_ports.h</code> file inside the headers directory.

- b. Change #define EX\_SSS\_BOOT\_SSS\_COMPORT\_DEFAULT "\\\.\\COMx" with the port COM number your laptop assigned to your FRDM-K64F. In this setup, the COM number is COM9.

AN12398

#### EdgeLock SE05x Quick start guide with Visual Studio project examples

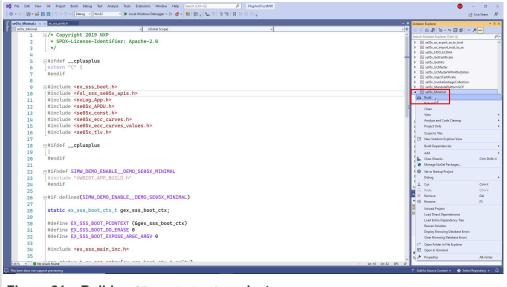

6. Select the se05x\_minimal project from the Solution Explorer window located on the right-hand side of the Visual Studio IDE. Do right-click on the project and click on **Set** as **StartUp project** as shown in Figure 20:

Figure 20. Set se05x minimal as StartUp project

7. Right click on the se05x\_minimal project and build it by clicking the build option as shown in Figure 21.

Figure 21. Build se05x\_minimal project

#### EdgeLock SE05x Quick start guide with Visual Studio project examples

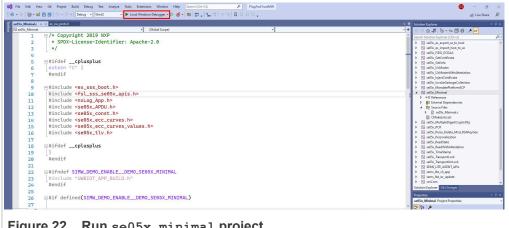

8. Click on Local Windows Debugger button in the top menu to run se05x minimal project as shown in Figure 22. The project will be executed after the project building process has finished.

Figure 22. Run se05x minimal project

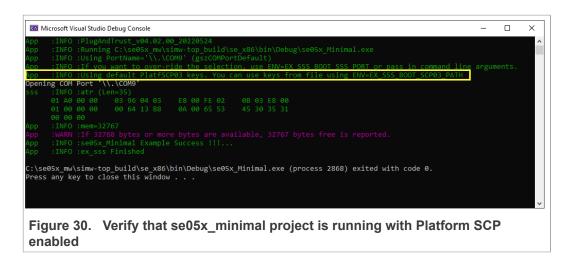

9. If the se05x minimal project runs successfully, a Console window will be opened. The logs in this Console window indicate the available memory in EdgeLock SE05x security IC (in this case, 592) as can be seen in Figure 23:

```

Microsoft Visual Studio Debug Console

×

:\se05x_mw\simw-top_build\se_x86\bin\Debug\se05x_Minimal.exe (process 4768) exited with code 0.

ress any key to close this window . . .

Figure 23. Verify that se05x minimal project is running

```

10. The same operation can be repeated with any of the other Plug & Trust middleware project examples.

EdgeLock SE05x Quick start guide with Visual Studio project examples

## 5 Product specific CMake build settings

The NXP Plug & Trust middleware supports the SE05x Secure Elements, the A5000 Secure Authenticator, and the legacy A71CH products.

The EdgeLock Plug & Trust middleware is delivered with CMake files that include the set of directives and instructions describing the project's source files and the build targets. The CMake files are used to select a dedicated EdgeLock product IC and the corresponding IoT applet or Authenticator application.

The SE050 product identification can be obtained as described in <u>AN12436</u> chapter 1 *Product Information*. <u>AN12973</u> describes the same procedure for the SE051 product family.

The following tables show the required PTMW CMake options to build a dedicated product variant. The SSSFTR\_ SE05X\_RSA CMake option is used to optimize the memory footprint for product variants that do not support RSA.

Table 3. CMake Settings for SE050E product variants

| Variant                            | OEF<br>ID | PTMW_<br>Applet | PTMW_<br>FIPS | PTMW_<br>SE05X_<br>Ver | PTMW_SE05X_Auth | PTMW_<br>SCP  | SSSFTR_<br>SE05X_<br>RSA |

|------------------------------------|-----------|-----------------|---------------|------------------------|-----------------|---------------|--------------------------|

| SE050E Dev. Board<br>OM-SE050ARD-E | A921      | SE050_E         | None          | 07_02                  | any<br>option   | None<br>or    | disabled                 |

| SE050E2                            | A921      |                 |               |                        |                 | SCP03_<br>SSS |                          |

Table 4. CMake Settings for SE050F product variants

| Variant                           | OEF<br>ID | PTMW_<br>Applet | PTMW_<br>FIPS | PTMW_<br>SE05X_<br>Ver | PTMW_SE05X_Auth                                                | PTMW_<br>SCP  | SSSFTR_<br>SE05X_<br>RSA |

|-----------------------------------|-----------|-----------------|---------------|------------------------|----------------------------------------------------------------|---------------|--------------------------|

| SE050F Dev.Board<br>OM-SE050ARD-F | A92A      | SE05X_C         | SE050         | 03_XX                  | PlatfSCP03<br>or                                               | SCP03_<br>SSS | enabled                  |

| SE050F2                           | A92A      |                 |               |                        | UserID_PlatfSCP03  or  AESKey_PlatfSCP03  or  ECKey_PlatfSCP03 |               |                          |

Table 5. CMake Settings for SE050 Previous Generation product variants

| Variant | OEF<br>ID | PTMW_<br>Applet | PTMW_<br>FIPS | PTMW_<br>SE05X_<br>Ver | PTMW_SE05X_Auth | PTMW_<br>SCP        | SSSFTR_<br>SE05X_<br>RSA |

|---------|-----------|-----------------|---------------|------------------------|-----------------|---------------------|--------------------------|

| SE050A1 | A204      | SE05X_A         | None          | 03_XX                  | any             | None                | disabled                 |

| SE050A2 | A205      |                 |               |                        | option          | or<br>SCP03_<br>SSS |                          |

| SE050B1 | A202      | SE05X_B         | None          | 03_XX                  | any             | None                | enabled                  |

| SE050B2 | A203      |                 |               |                        | option          | or<br>SCP03_<br>SSS |                          |

AN12398

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2022. All rights reserved.

#### EdgeLock SE05x Quick start guide with Visual Studio project examples

Table 5. CMake Settings for SE050 Previous Generation product variants...continued

| Variant                        | OEF                 | PTMW_<br>Applet | PTMW_<br>FIPS | PTMW_<br>SE05X_<br>Ver | PTMW_SE05X_Auth                                                          | PTMW_<br>SCP  | SSSFTR_<br>SE05X_<br>RSA |

|--------------------------------|---------------------|-----------------|---------------|------------------------|--------------------------------------------------------------------------|---------------|--------------------------|

| SE050C1                        | A200                | SE05X_C         | None          | 03_XX                  | any                                                                      | None          | enabled                  |

| SE050C2                        | A201                |                 |               |                        | option                                                                   | or            |                          |

| SE050 Dev Board<br>OM-SE050ARD | A1F4                |                 |               |                        |                                                                          | SCP03_<br>SSS |                          |

| SE050F2                        | A77E <sup>[1]</sup> | SE05X_C         | SE050         | 03_xx                  | PlatfSCP03 or UserID_PlatfSCP03 or AESKey_PlatfSCP03 or ECKey PlatfSCP03 | SCP03_<br>SSS | enabled                  |

<sup>[1]</sup> All SE050F2 with variant A77E have date code in year 2021. All the SE050F2 with date code in the year 2022 have the variant identifier A92A.

Table 6. CMake Settings for SE051 product variants

| Variant | OEF  | PTMW_   | PTMW_ | PTMW_         | PTMW_SE05X_Auth | PTMW_                            | SSSFTR_       |

|---------|------|---------|-------|---------------|-----------------|----------------------------------|---------------|

|         | ID   | Applet  | FIPS  | SE05X_<br>Ver |                 | SCP                              | SE05X_<br>RSA |

| SE051A2 | A920 | SE05X_A | None  | 07_02         | any<br>option   | None<br>or<br>SCP03_<br>SSS      | disabled      |

| SE051C2 | A8FA | SE05X_C | None  | 07_02         | any<br>option   | None<br>or<br>SCP03_<br>SSS      | enabled       |

| SE051W2 | A739 | SE05X_C | None  | 07_02         | any<br>option   | None or SCP03_ SSS or SCP03_ SSS | enabled       |

| SE051A2 | A565 | SE05X_A | None  | 06_00         | any<br>option   | None or SCP03_ SSS               | disabled      |

| SE051C2 | A564 | SE05X_C | None  | 06_00         | any<br>option   | None<br>or<br>SCP03_<br>SSS      | enabled       |

#### EdgeLock SE05x Quick start guide with Visual Studio project examples

Table 7. CMake Settings for A5000 product variants

| Variant     | OEF<br>ID | PTMW_<br>Applet | PTMW_<br>FIPS | PTMW_<br>SE05X_<br>Ver | PTMW_SE05X_Auth | PTMW_<br>SCP  | SSSFTR_<br>SE05X_<br>RSA |

|-------------|-----------|-----------------|---------------|------------------------|-----------------|---------------|--------------------------|

| OM-A5000ARD | A736      | AUTH            | None          | 07_02                  | any             | None          | disabled                 |

| A5000       | A736      |                 |               |                        | option          | or            |                          |

|             |           |                 |               |                        |                 | SCP03_<br>SSS |                          |

#### 5.1 Example: SE050E CMake build settings

The following images show the configuration for the SE050E development board OM-SE05ARD-E.

- Select SE05X E for the CMake option PTWM Applet.

- Select None for the CMake option PTWM FIPS.

- Select 07 02 for the CMake option PTWM SE05X Ver.

- Disable the CMake option SSSFTR SE05X RSA.

In this example we use plain communication. Plain communication for the example execution is enabled by selecting the following options:

- Select None for the CMake option PTMW SE05X Auth.

- Select None for the CMake option PTMW SCP.

How to enable Platform SCP is described in How to enable Platform SCP.

#### EdgeLock SE05x Quick start guide with Visual Studio project examples

Figure 24. SE050E CMake Settings - Plain communication

EdgeLock SE05x Quick start guide with Visual Studio project examples

## 6 Binding EdgeLock SE05x to a host using Platform SCP

Binding is a process to establish a pairing between the IoT device host MPU/MCU and EdgeLock SE05x, so that only the paired MPU/MCU is able to use the services offered by the corresponding EdgeLock SE05x and vice versa.

A mutually authenticated, encrypted channel will ensure that both parties are indeed communicating with the intended recipients and that local communication is protected against local attacks, including man-in-the-middle attacks aimed at intercepting the communication between the MPU/MCU and the EdgeLock SE05x and physical tampering attacks aimed at replacing the host MPU/MCU or EdgeLock SE05x .

EdgeLock SE05x natively supports Global Platform Secure Channel Protocol 03 (SCP03) for this purpose. PlatformSCP uses SCP03 and can be enabled to be mandatory.

This chapter describes the required steps to enable Platform SCP in the middleware for EdgeLock SE05x.

The following topics are discussed:

- Section 6.1 Introduction to the Global Platform Secure Channel Protocol 03 (SCP03)

- Section 6.2 How to configure the Platform SCP keys

- Section 6.3 How to enable Platform SCP

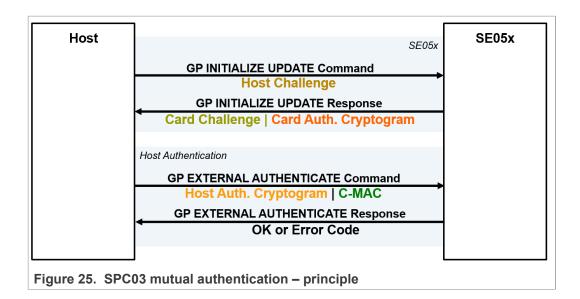

## 6.1 Introduction to the Global Platform Secure Channel Protocol 03 (SCP03)

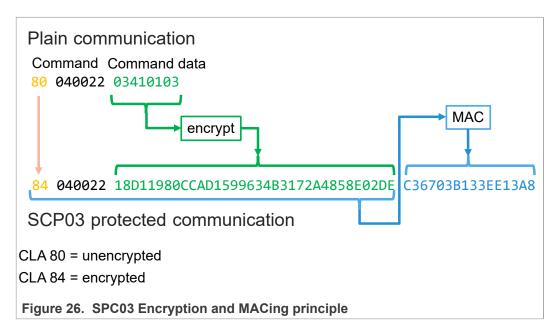

The Secure Channel Protocol SCP03 authenticates and protects locally the bidirectional communication between host and EdgeLock SE05x against eavesdropping on the physical I2C interface.

EdgeLock SE05x can be bound to the host by injecting in both the host and EdgeLock SE05x the same unique SCP03 AES key-set and by enabling the Platform SCP feature in the Plug & Trust middleware. The <a href="AN12662">AN12662</a> Binding a host device to EdgeLock SE05x describes in detail the concept of secure binding.

SCP03 is defined in Global Platform Secure Channel Protocol '03' - Amendment D v1.2 specification.

SCP03 can provide the following three security goals:

#### Mutual authentication (MA)

Mutual authentication is achieved through the process of initiating a Secure Channel and provides assurance to both the host and the EdgeLock SE05x entity that they are communicating with an authenticated entity.

#### Message Integrity

The Command- and Response-MAC are generated by applying the CMAC according NIST SP 800-38B.

#### Confidentiality

The message data field is encrypted across the entire data field of the command message to be transmitted to the EdgeLock SE05x, and across the response transmitted from the EdgeLock SE05x.

The SCP03 secure channel is set up via the EdgeLock SE05x Java Card OS Manager using the standard ISO7816-4 secure channel APDUs.

AN12398

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2022. All rights reserved.

#### EdgeLock SE05x Quick start guide with Visual Studio project examples

The establishment of an SCP03 channel requires three static 128-bit AES keys shared between the two communicating parties: Key-ENC, Key-MAC and Key-DEK. These keys are stored in the Java Card Secondary Security Domain (SSD) and not in the secure authenticator applet.

${\tt Key-ENC}$  and  ${\tt Key-MAC}$  keys are used during the SCP03 channel establishment to generate the session keys. Session Keys are generated to ensure that a different set of keys are used for each Secure Channel Session to prevent replay attacks.

<code>Key-ENC</code> is used to derive the session key <code>S-ENC</code>. The <code>S-ENC</code> key is used for encryption/decryption of the exchanged data. The session keys <code>S-MAC</code> and <code>R-MAC</code> are derived from <code>Key-MAC</code> and used to generate/verify the integrity of the exchanged data (C-APDU and R-APDU).

Key-DEK key is used to encrypt new SCP03 keys in case they get updated.

Table 8. Static SCP03 keys

| Key     | Description                                                 | Usage                                                                                                       | Key<br>Type |

|---------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------|

| Key-ENC | Static Secure Channel Encryption Key                        | Generate session key for Decryption/<br>Encryption (AES)                                                    | AES<br>128  |

| Key-MAC | Static Secure Channel<br>Message Authentication<br>Code Key | Generate session key for Secure Channel authentication and Secure Channel MAC Verification/Generation (AES) | AES<br>128  |

| Key-DEK | Data Encryption Key                                         | Sensitive Data Decryption (AES)                                                                             | AES<br>128  |

The session key generation is performed by the Plug & Trust middleware host crypto.

Table 9. SCP03 session keys

| Key    | Description                                                       | Usage                                | Key<br>Type |

|--------|-------------------------------------------------------------------|--------------------------------------|-------------|

| S-ENC  | Session Secure Channel Encryption Key                             | Used for data confidentiality        | AES<br>128  |

| S-MAC  | Secure Channel Message<br>Authentication Code Key for<br>Command  | Used for data and protocol integrity | AES<br>128  |

| S-RMAC | Secure Channel Message<br>Authentication Code Key for<br>Response | User for data and protocol integrity | AES<br>128  |

**Note:** For further details please refer to Global Platform Secure Channel Protocol '03' - Amendment D v1.2.

#### EdgeLock SE05x Quick start guide with Visual Studio project examples

#### 6.2 How to configure the product specific default Platform SCP keys

The default Platform SCP key values are described for the EdgeLock SE05x product variants in <u>AN12436</u> and for the EdgeLock SE051 variants in <u>AN12973</u>.

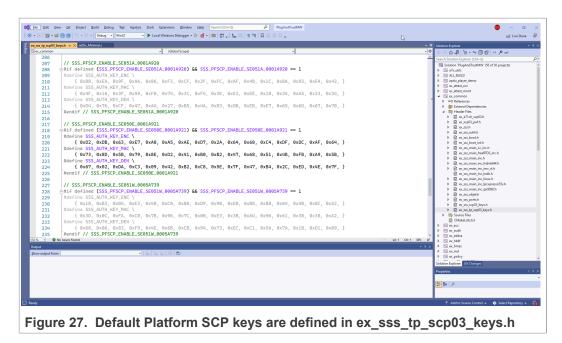

The Platform SCP keys can be defined in the Plug & Trust middleware source code.

The Plug & Trust middleware header file  $ex\_sss\_tp\_scp03\_keys.h$  contains the default values of all EdgeLock SE05x, EdgeLock SE051, A5000 and A71CH product variants.

The <code>ex\_sss\_tp\_scp03\_keys.h</code> header file can be found in the following location: C:  $\se05x \ mw\simeq top\ss<ex\le$

#### EdgeLock SE05x Quick start guide with Visual Studio project examples

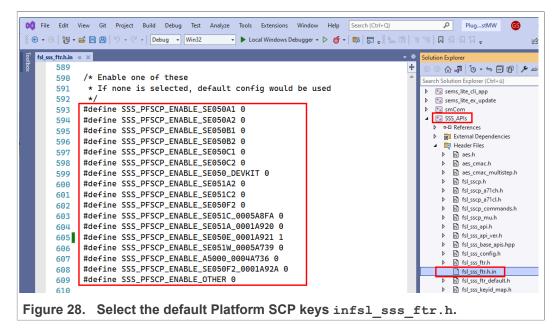

The  $fsl_sss_ftr.h.in$  file includes options to select one of the predefined default Platform SCP keys. This file is located in:  $C:\se05x mw\simw-top\sss\inc$

Select the desired value of the compilation option by setting exclusively the corresponding C-preprocessor define  $SSS\_PFSCP\_ENABLE\_xx$  to 1 (enable). All other values for the same option (represented by C-preprocessor defines  $SSS\_PFSCP\_ENABLE\_xx$ ) must be set to 0.

The Plug & Trust Middleware uses a feature file to select/detect used/enabled features within the middleware stack. The file  $fsl\_sss\_ftr.h$  is automatically generated into the used build directory. CMake is overwritting the  $fsl\_sss\_ftr.h$  file every time CMake is invoked. CMake is using the SCP key settings of the  $fsl\_sss\_ftr.h.in$  file as input to generate the the  $fsl\_sss\_ftr.h$  file. You do not have to manually edit

#### EdgeLock SE05x Quick start guide with Visual Studio project examples

the fsl\_sss\_ftr.h feature file. Selections from CMake edit cache would automatically make relevant updates into the generated feature file.

**Note:** The Platform SCP key selection in the fsl\_sss\_ftr.h.in CMake input file is persistent.

The location of the generated fsl\_sss\_ftr.h feature header file is:  $C: \se05x_mw\simw-top\_build\se\_x86$

The following tables contains the the Platform SCP key header file define to be set to 1 (enable) for the different secure element and secure authenticator product variants.

Table 10. Platform SCP key define prefix for SE050E product variants

| Variant                            | OEF ID | Platform SCP key define to be set to '1' |

|------------------------------------|--------|------------------------------------------|

| SE050E Dev. Board<br>OM-SE050ARD-E | A921   | SSS_PFSCP_ENABLE_SE050E_0001A921         |

| SE050E2                            | A921   | SSS_PFSCP_ENABLE_SE050E_0001A921         |

Table 11. Platform SCP key define prefix for SE050F product variants

| Variant          | OEF ID | Platform SCP key define to be set to '1' |

|------------------|--------|------------------------------------------|

| SE050F Dev.Board | A92A   | SSS_PFSCP_ENABLE_SE050F2_0001A92A        |

| OM-SE050ARD-F    |        |                                          |

| SE050F2          | A92A   | SSS_PFSCP_ENABLE_SE050F2_0001A92A        |

Table 12. Platform SCP key define prefix for SE050 Previous Generation product variants

| Variant         | OEF ID              | Platform SCP key define to be set to '1' |

|-----------------|---------------------|------------------------------------------|

| SE050A1         | A204                | SSS_PFSCP_ENABLE_SE050A1                 |

| SE050A2         | A205                | SSS_PFSCP_ENABLE_SE050A2                 |

| SE050B1         | A202                | SSS_PFSCP_ENABLE_SE050B1                 |

| SE050B2         | A203                | SSS_PFSCP_ENABLE_SE050B2                 |

| SE050C1         | A200                | SSS_PFSCP_ENABLE_SE050C1                 |

| SE050C2         | A201                | SSS_PFSCP_ENABLE_SE050C2                 |

| SE050 Dev Board | A1F4                | SSS_PFSCP_ENABLE_SE050_DEVKIT            |

| OM-SE050ARD     |                     |                                          |

| SE050F2         | A77E <sup>[1]</sup> | SSS_PFSCP_ENABLE_SE050F2                 |

<sup>[1]</sup> All SE050F2 with variant A77E have date code in year 2021. All the SE050F2 with date code in the year 2022 have the variant identifier A92A.

Table 13. Platform SCP key define prefix for SE051 product variants

| Variant | OEF ID | Platform SCP key define to be set to '1' |

|---------|--------|------------------------------------------|

| SE051A2 | A920   | SSS_PFSCP_ENABLE_SE051A_0001A920         |

| SE051C2 | A8FA   | SSS_PFSCP_ENABLE_SE051C_0005A8FA         |

| SE051W2 | A739   | SSS_PFSCP_ENABLE_SE051W_0005A739         |

| SE051A2 | A565   | SSS_PFSCP_ENABLE_SE051A2                 |

| SE051C2 | A564   | SSS_PFSCP_ENABLE_SE051C2                 |

#### EdgeLock SE05x Quick start guide with Visual Studio project examples

Table 14. Platform SCP key define prefix for A5000 product variants

| Variant                         | OEF ID | Platform SCP key define to be set to '1' |

|---------------------------------|--------|------------------------------------------|

| A5000 Dev. Board<br>OM-A5000ARD | A736   | SSS_PFSCP_ENABLE_A5000_0004A736          |

| A5000                           | A736   | SSS_PFSCP_ENABLE_A5000_0004A736          |

#### 6.3 How to enable Platform SCP

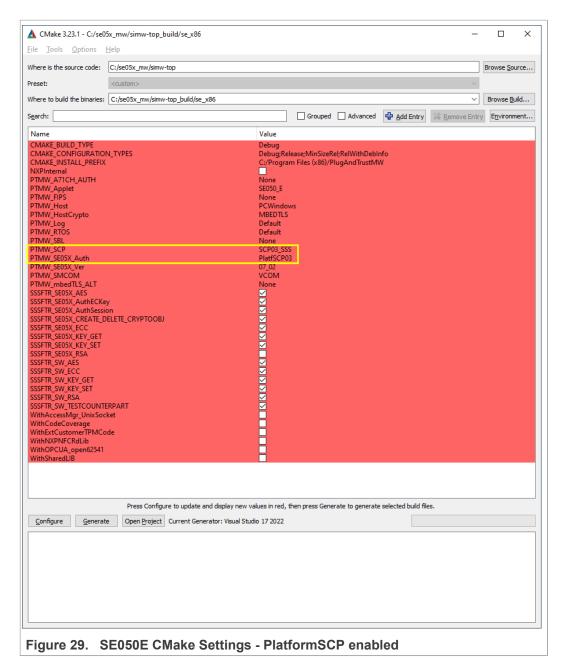

To enable Platform SCP is required to rebuild the SDK with the following CMake options:

- Select SCP03 SSS for the CMake option PTMW SCP.

- Select PlatfSCP03 for the CMake option PTMW SE05X Auth.

The following images show the configuration for the SE050E development board OM-SE05ARD-E.

1. Open a command prompt and go to the directory where the Plug & Trust middleware is built.

Send: cd C:\se05x\_mw\simw-top\_build\se\_x86

2. Open the cmake configuration interface.

Send: cmake-qui .

#### EdgeLock SE05x Quick start guide with Visual Studio project examples

If you have edited any of the parameters in the menu, before exiting press the buttons **Configure** and **Generate** to apply the changes. In the next step we need to rebuild the Visual Studio solution. Finally, we can verify if we successfully enabled Platform SCP. For this purpose we run again the se05x minimal example as described in Section 4.4.

#### EdgeLock SE05x Quick start guide with Visual Studio project examples

The Plug & Trust Middleware provides the following additional examples to rotate the PlatformSCP Keys and to mandate Platform SCP.

- SE05X Rotate PlatformSCP Keys example: Showcases authentication with default Platform SCP03 keys and the rotation (update) of those keys with user defined keys. The example documentation is available in the EdgeLock SE05x Plug & Trust Middleware documentation (C:\se05x\_mw\simw-top\doc\demos\se05x\se05x\_RotatePlatformSCP03Keys\Readme.html). The example source code is available at C:\se05x\_mw\simw-top\demos\se05x\se05x RotatePlatformSCP03Keys.

- SE05X Mandate SCP example: Showcases how to make Platform SCP03 authentication mandatory in EdgeLock SE05x. The example documentation is available in the EdgeLock SE05x Plug & Trust Middleware documentation (C:\se05x\_mw\simw-top\doc\demos\se05x\se05x\_MandatePlatformSCP\Readme.html). The example source code is available at C:\se05x\_mw\simw-top\demos\se05x\se05x\se05x\_MandatePlatformSCP.

- SE05x AllowWithout PlatformSCP example: This project demonstrates how to configure SE05X to allow without platform SCP. The example documentation is available in the EdgeLock SE05x Plug & Trust Middleware documentation (~/se\_mw/simwtop/doc/demos/se05x/se05x\_AllowWithoutPlatformSCP/Readme.html). The example source code is available at ~/se\_mw/simw-top/demos/se05x/se05x AllowWithoutPlatformSCP.

EdgeLock SE05x Quick start guide with Visual Studio project examples

## 7 Appendix A: Install Visual Studio 2022

Visual Studio is Microsoft's fully-featured IDE for Android, iOS, Windows, web, and cloud. Visual Studio 2022 introduces rich support for CMake, including cross-platform CMake projects.

This section explains how to install Visual Studio 2022 version, but the same procedure can be applied for more recent versions.

- 1. Go to Visual Studio site.

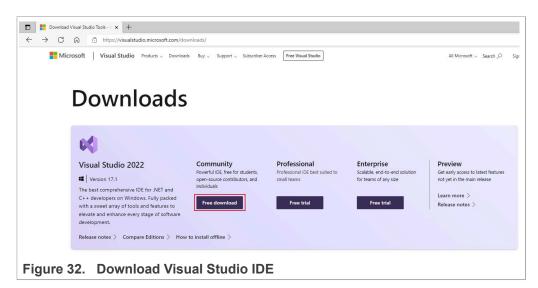

- 2. Select (1) **Download** and click on **Community 2022** in the **Download Visual Studio** button as shown in <u>Figure 31</u> and <u>Figure 32</u>:

#### EdgeLock SE05x Quick start guide with Visual Studio project examples

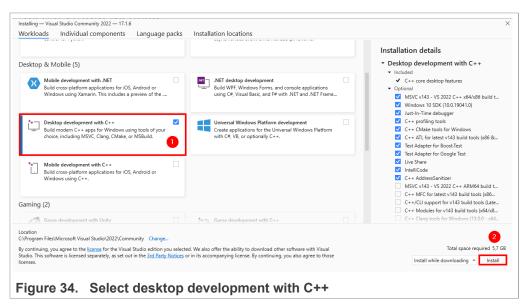

3. An \*.exe installer will download to your laptop. Double click on the installer file and follow the setup wizard until the installation is completed. This process might take a few minutes. Figure 33 shows Visual Studio installation wizard as an example:

As part of the Visual Studio setup, it is mandatory that you enable the installation of Desktop development with C++. Select (1) Desktop development with C++ and (2) click install as shown in Figure 34:

#### EdgeLock SE05x Quick start guide with Visual Studio project examples

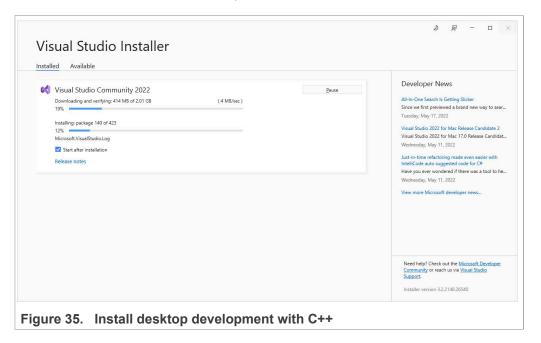

5. Visual C++ Tools for CMake is installed by default as part of the Desktop development with C++ workload. This process might take several minutes. Figure 35 shows Visual Studio installation wizard as an example:

6. After the installation is completed, you might be asked to reboot your system.

EdgeLock SE05x Quick start guide with Visual Studio project examples

## 8 Appendix B: Install CMake

CMake is an open-source, cross-platform family of tools that helps you build C/C++ projects on multiple platforms using a compiler-independent method. It has minimal dependencies, requiring only a C++ compiler on its own build system. SE05x middleware leverages on CMake to generate native makefiles and workspaces that can be used in the compiler environment of your choice.

#### To install CMake:

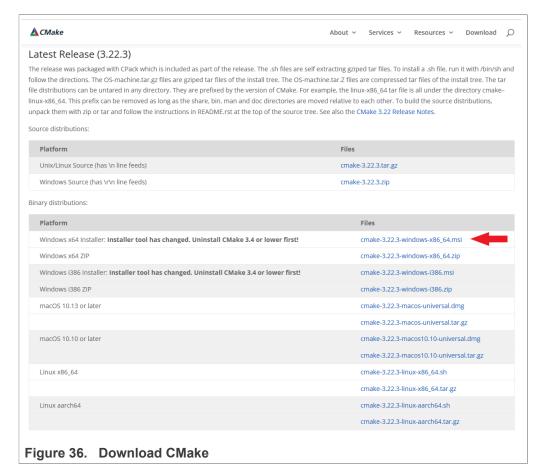

- 1. Go to CMake downloads page: <a href="https://cmake.org/download/">https://cmake.org/download/</a>

- 2. Scroll down and select your binary distribution. For this guide, the binary distribution is Windows as shown in Figure 36:

### EdgeLock SE05x Quick start guide with Visual Studio project examples

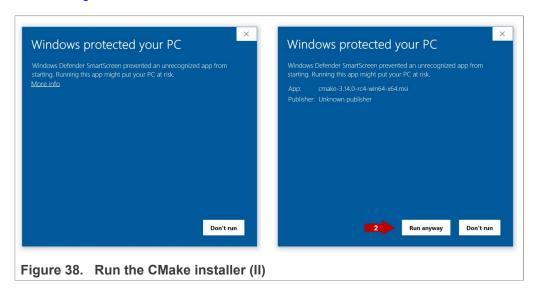

3. Double click on the downloaded installer file. Windows Defender SmartScreen might pop-up the wizard shown in Figure 37:

4. If this is your case: Click (1) on *More info* and then (2) click on *Run anyway* as shown in Figure 38:

## EdgeLock SE05x Quick start guide with Visual Studio project examples

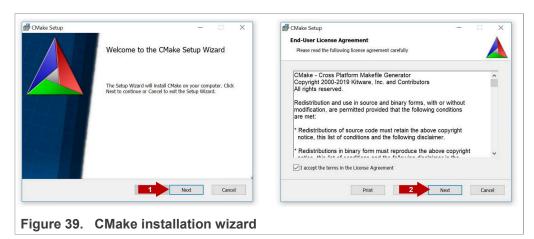

5. The CMake installation wizard will open. Click (1) **Next** and (2) **accept** the End-User License Agreement as shown in Figure 39:

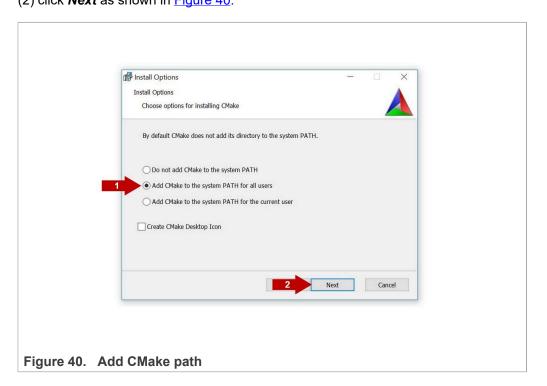

6. As part of the CMake setup, (1) **Add Cmake to the system PATH for all users** and (2) click **Next** as shown in Figure 40:

### EdgeLock SE05x Quick start guide with Visual Studio project examples

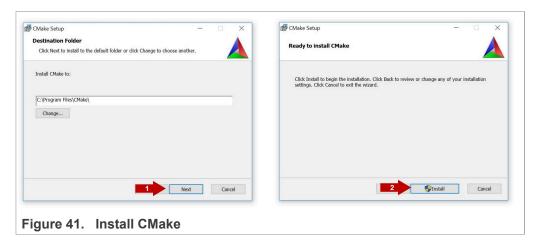

7. Select a destination folder, (1) click **Next** and then (2) click **Install** as shown in Figure 41:

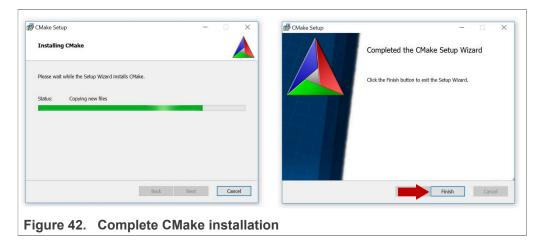

8. Wait a few seconds until the installation is completed and click *Finish* as shown in Figure 42:

EdgeLock SE05x Quick start guide with Visual Studio project examples

## 9 Appendix C: Install Python

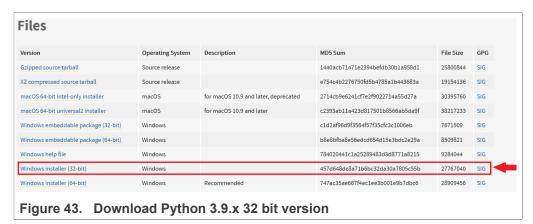

This section explains how to install Python  $\geq 3.7.x$  and  $\leq 3.9.x$  32-bit version, but the same procedure can be applied for more recent versions. Follow these steps to install Python in your local machine:

Go to <a href="https://www.python.org/downloads">https://www.python.org/downloads</a> and download Python ≥ 3.7.x and ≤ 3.9 32-bit version. Make sure you download the Python 32 bit version.

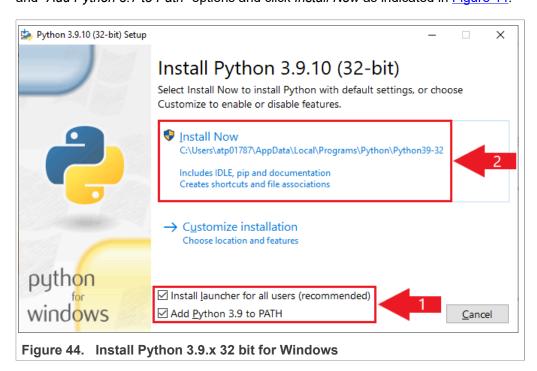

2. Double click on the downloaded installer file. Select the "Install launcher for all users" and "Add Python 3.7 to Path" options and click Install Now as indicated in Figure 44:

### EdgeLock SE05x Quick start guide with Visual Studio project examples

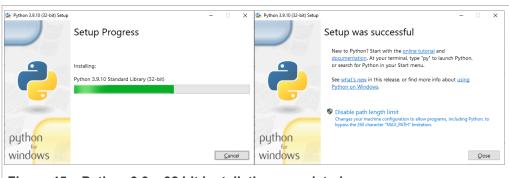

3. Wait a few seconds until the installation is completed as indicated in Figure 45

Figure 45. Python 3.9.x 32 bit installation completed

EdgeLock SE05x Quick start guide with Visual Studio project examples

# 10 Appendix D: Update FRDM-K64F board with DAPLink firmware

Arm Mbed DAPLink is an open-source software project that enables programming and debugging application software running on Arm Cortex CPUs. DAPLink runs an open-source bootloader and enables developers with drag-and-drop programming, a serial port and CMSIS-DAP based debugging.

**Note:** To debug MCUXpresso project examples, we need to flash FRDM-K64F with DAPLink firmware. **If your FRDM-K64F board already includes DAPLink firmware, you can skip these steps**.

To flash DAPLink firmware, follow these steps:

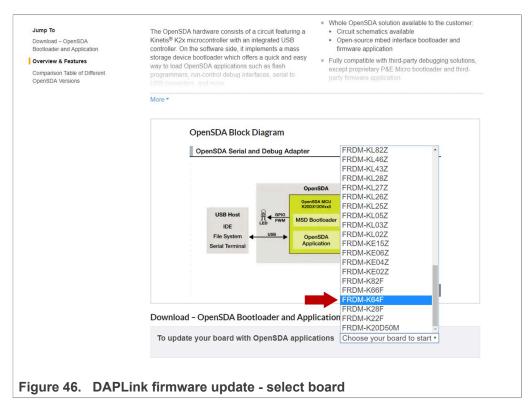

- 1. Go to NXP OpenSDA site

- Scroll down and select FRDM-K64F board from the *Download OpenSDA bootloader and application* drop down list as indicated in <u>Figure 46</u>:

#### EdgeLock SE05x Quick start guide with Visual Studio project examples

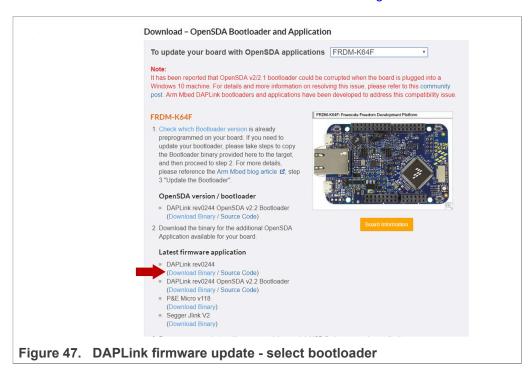

3. Download the latest DAPLink firmware version as shown in Figure 47:

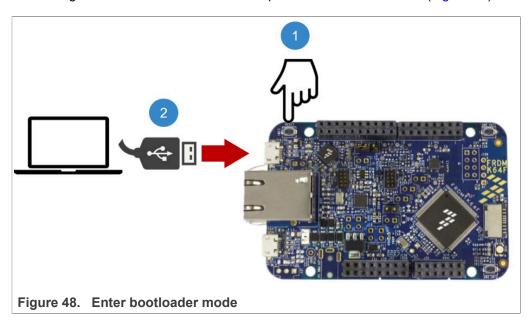

4. Start the board's bootloader mode. To do so, (1) keep reset button pressed while (2) connecting the USB cable to the SDA USB port and release it after 1s (Figure 48):

#### EdgeLock SE05x Quick start guide with Visual Studio project examples

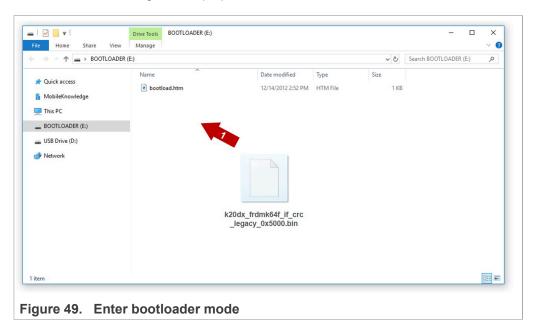

5. Drag and drop or copy and paste the binary file into the BOOTLOADER drive from your computer file explorer as shown in <u>Figure 49</u>. The FRDM-K64F will automatically un-mount after the drag and drop operation.

- 6. Un-plug and re-plug the USB cable from the SDA USB port *without* keeping reset button pressed.

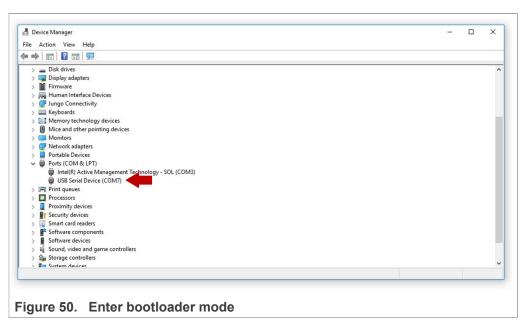

- Check the category Ports (COM & LPT) from your computer Device Manager to ensure that new devices have been properly detected and their driver correctly installed by your computer OS.

**Note:** In case the device does not show up in your Device Manager, please download the latest bootloader version, as shown in Figure 47, or check / exchange the USB cables used.

#### EdgeLock SE05x Quick start guide with Visual Studio project examples

### 11 Legal information

#### 11.1 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

#### 11.2 Disclaimers

Limited warranty and liability - Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors. In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based

on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Evaluation products — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer. In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages. Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified or documented vulnerabilities. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. NXP has a Product Security Incident Response Team (PSIRT) (reachable at PSIRT@nxp.com) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

#### 11.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

## EdgeLock SE05x Quick start guide with Visual Studio project examples

## **Tables**

| Tab. 1. | EdgeLock SE05x development boards 4          | Tab. 9.  | SCP03 session keys                        | 26 |

|---------|----------------------------------------------|----------|-------------------------------------------|----|

| Tab. 2. | FRDM-K64F details5                           | Tab. 10. | Platform SCP key define prefix for SE050E |    |

| Tab. 3. | CMake Settings for SE050E product            |          | product variants                          | 29 |

|         | variants21                                   | Tab. 11. | Platform SCP key define prefix for SE050F |    |

| Tab. 4. | CMake Settings for SE050F product            |          | product variants                          | 29 |

|         | variants21                                   | Tab. 12. | Platform SCP key define prefix for SE050  |    |

| Tab. 5. | CMake Settings for SE050 Previous            |          | Previous Generation product variants      | 29 |

|         | Generation product variants21                | Tab. 13. | Platform SCP key define prefix for SE051  |    |

| Tab. 6. | CMake Settings for SE051 product variants22  |          | product variants                          | 29 |

| Tab. 7. | CMake Settings for A5000 product variants 23 | Tab. 14. | Platform SCP key define prefix for A5000  |    |

| Tab. 8. | Static SCP03 keys26                          |          | product variants                          | 30 |

|         | · · · · · · · · · · · · · · · · · · ·        |          | ·                                         |    |

## EdgeLock SE05x Quick start guide with Visual Studio project examples

# **Figures**

| Fig. 1.  | Jumper configuration for FRDM-K64F           | 6  | Fig. 25. | SPC03 mutual authentication – principle      | 27 |

|----------|----------------------------------------------|----|----------|----------------------------------------------|----|

| Fig. 2.  | Arduino connectors of OM-SE05xARD and        |    | Fig. 26. | SPC03 Encryption and MACing principle        | 27 |

|          | FRDM-K64F boards                             | 7  | Fig. 27. | Default Platform SCP keys are defined in     |    |

| Fig. 3.  | OM-SE05xARD mounted in FRDM-K64F             |    |          | ex_sss_tp_scp03_keys.h                       | 28 |

|          | board                                        | 7  | Fig. 28. | Select the default Platform SCP keys infsl_  |    |

| Fig. 4.  | Unplug and plug OpenSDA port                 | 8  |          | sss_ftr.h                                    | 28 |

| Fig. 5.  | FRDM-K64F drive                              |    | Fig. 29. | SE050E CMake Settings - PlatformSCP          |    |

| Fig. 6.  | VCOM binary folder                           | 9  |          | enabled                                      | 31 |

| Fig. 7.  | Drag and drop VCOM binary                    | 9  | Fig. 30. | Verify that se05x_minimal project is running |    |

| Fig. 8.  | Check VCOM and serial ports                  | 10 |          | with Platform SCP enabled                    | 32 |

| Fig. 9.  | Create se05x_mw folder                       | 11 | Fig. 31. | Visual Studio side                           | 33 |

| Fig. 10. | Unzip se050 middleware                       | 12 | Fig. 32. | Download Visual Studio IDE                   | 33 |

| Fig. 11. | Generate Plug & Trust middleware define      |    | Fig. 33. | Visual Studio IDE installation wizard        | 34 |

| _        | the environment                              | 13 | Fig. 34. | Select desktop development with C++          | 34 |

| Fig. 12. | Generate Plug & Trust middleware project     |    | Fig. 35. | Install desktop development with C++         | 35 |

| _        | examples                                     | 13 | Fig. 36. | Download CMake                               |    |

| Fig. 13. | SE050 middleware project structure           |    | Fig. 37. | Execute CMake installer                      | 37 |

| Fig. 14. | Plug OpenSDA and USB FRDM-K64F               |    | Fig. 38. | Run the CMake installer (II)                 | 37 |

| Ü        | ports.                                       | 14 | Fig. 39. | CMake installation wizard                    |    |

| Fig. 15. | Open the CMake configuration interface       | 15 | Fig. 40. | Add CMake path                               | 38 |

| Fig. 16. | Review CMake configuration                   | 16 | Fig. 41. | Install CMake                                |    |

| Fig. 17. | Open PlugAndTrustMW.sln Visual Studio        |    | Fig. 42. | Complete CMake installation                  | 39 |

| Ū        | project solution                             | 17 | Fig. 43. | Download Python 3.9.x 32 bit version         |    |

| Fig. 18. | PlugAndTrustMW.sln Visual Studio project     |    | Fig. 44. | Install Python 3.9.x 32 bit for Windows      | 40 |

| Ū        | workspace                                    | 18 | Fig. 45. | Python 3.9.x 32 bit installation completed   | 41 |

| Fig. 19. | Change VCOM port number in your              |    | Fig. 46. | DAPLink firmware update - select board       |    |

| Ū        | solution                                     | 18 | Fig. 47. | DAPLink firmware update - select             |    |

| Fig. 20. | Set se05x_minimal as StartUp project         | 19 | Ü        | bootloader                                   | 43 |

| Fig. 21. | Build se05x minimal project                  |    | Fig. 48. | Enter bootloader mode                        | 43 |

| Fig. 22. | Run se05x_minimal project                    |    | Fig. 49. | Enter bootloader mode                        |    |

| Fig. 23. | Verify that se05x_minimal project is running |    | Fig. 50. | Enter bootloader mode                        | 44 |

| Fig. 24. | SE050E CMake Settings - Plain                |    | <b>J</b> |                                              |    |

| •        | communication                                | 24 |          |                                              |    |

|          |                                              |    |          |                                              |    |

### EdgeLock SE05x Quick start guide with Visual Studio project examples

### **Contents**

| 1   | How to use this document                   | 3  |

|-----|--------------------------------------------|----|

| 2   | Hardware required                          | 4  |

| 3   | Boards setup                               |    |

| 3.1 | OM-SE05xARD jumper configuration           | 6  |

| 3.2 | OM-SE05xARD and FRDM-K64F board            |    |

|     | connection                                 | 6  |

| 3.3 | Flash FRDM-K64F with VCOM software         | 7  |

| 4   | Run Plug & Trust middleware Visual         |    |

|     | Studio project examples                    | 11 |

| 4.1 | Prerequisites                              |    |

| 4.2 | Download Plug & Trust middleware           |    |

| 4.3 | Build Plug & Trust middleware project      |    |

|     | examples                                   | 12 |

| 4.4 | Execute EdgeLock SE05x Visual Studio       |    |

|     | project examples                           | 14 |

| 5   | Product specific CMake build settings      | 21 |

| 5.1 | Example: SE050E CMake build settings       | 23 |

| 6   | Binding EdgeLock SE05x to a host using     |    |

|     | Platform SCP                               | 25 |

| 6.1 | Introduction to the Global Platform Secure |    |

|     | Channel Protocol 03 (SCP03)                | 25 |

| 6.2 | How to configure the product specific      |    |

|     | default Platform SCP keys                  | 27 |

| 6.3 | How to enable Platform SCP                 |    |

| 7   | Appendix A: Install Visual Studio 2022     | 33 |

| 8   | Appendix B: Install CMake                  | 36 |

| 9   | Appendix C: Install Python                 | 40 |

| 10  | Appendix D: Update FRDM-K64F board         |    |

|     | with DAPLink firmware                      | 42 |

| 11  | Legal information                          | 45 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.