# AN12377 Tuning I2C Timing In Slave Mode

Rev. 1 — April 2019

#### **Application Note**

### **1** Introduction

The  $l^2C$  module is popular in most applications. Kinetis MCUs provide strong features on the  $l^2C$  module, which is compatible with the  $l^2C$ -bus specification and easy to interface with other devices. However, incorrect configuration may cause potential timing issues. This document shows how to configure the  $l^2C$  timing of a slave device to meet application needs which apply to Kinetis parts that contain I2C IP instead of LPI2C.

### 2 Overview

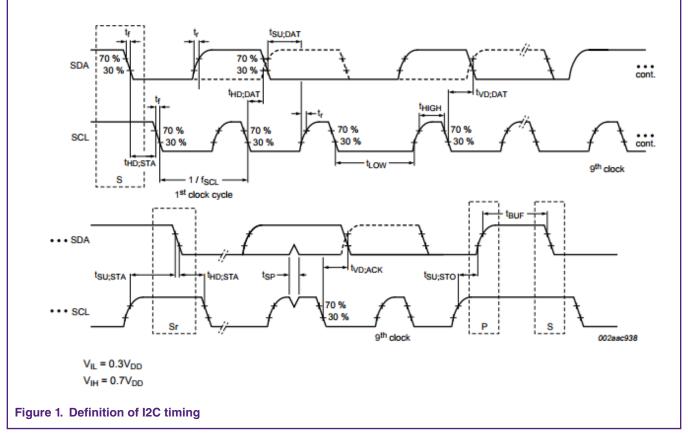

The I<sup>2</sup>C specification defines detailed timing specifications to enable the I<sup>2</sup>C device to follow the same standard and make different devices working together. Figure 1. on page 1 shows the timing definition for tSU:DAT.

### Contents

| 1 Introduction                                  | 1 |

|-------------------------------------------------|---|

| 2 Overview                                      | 1 |

| 3 Timing issues caused by<br>incorrect settings | 2 |

| 4 Tuning the timing using register<br>I2Cx_F    | 3 |

| 5 Conclusion                                    | 5 |

| 6 References                                    | 5 |

| 7 Revision history                              | 5 |

The Kinetis IP provides register I2Cx\_F to tune the timing. The reference manual provides the reference table on how to impact the I<sup>2</sup>C baud rate and data hold time. For the slave mode, this register also heavily impacts the timing and incorrect settings may

cause timing issues. There might not be a clear explanation in the reference manual, but it must be consulted to get a correct configuration.

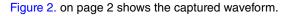

## 3 Timing issues caused by incorrect settings

When configuring the I<sup>2</sup>C for a master device, most users know how to configure the I2Cx\_F register to get the expected baud rate. However, when enabling it in the slave mode, users are not aware of the I2Cx\_F function during the timing tuning and do nothing with the I2Cx\_F register. In most customer applications, this possibly causes a timing issue. For example, when it works in the slave mode after events (interrupt of receiving new data or transmitting complete) occur, the slave device drives the SCL low by clock stretching and waits to handle I<sup>2</sup>C events. It releases the SCL together with the SDA after writing/reading the I<sup>2</sup>C data register when the I2Cx\_F is set to 0. This causes the master to detect a wrong signal and fail to meet the SDA setup time requirement.

Figure 3. on page 3 shows the clock stretching timing.

Figure 3. on page 3 shows the SDA and SCL release at almost the same time. For the I<sup>2</sup>C timing definition to match the values in Figure 4. on page 3, the tSU:DAT minimum value must be around 100 ns in the fast mode and 250 ns in the standard mode. Therefore, the above timing violates the specification.

The tSU:DAT timing and the I<sup>2</sup>C specification give the characteristic parameters shown in Figure 4. on page 3.

|         | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Standard-mode |     | Fast-mode |     | Fast-mode Plus |     | 11   |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----|-----------|-----|----------------|-----|------|

| Symbol  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Min           | Max | Min       | Max | Min            | Max | Unit |

| tSU:DAT | data set-up time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 250           | -   | 100       | -   | 50             | -   | ns   |

| Note    | A Fast-mode I2C-bus device can be used in a Standard-mode I2C-bus system, but the requirement tSU;DAT 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line tr(max) + tSU;DAT = 1000 + 250 = 1250 ns (according to the Standard-mode I2C-bus specification) before the SCL line is released. Also the acknowledge timing must meet this set-up time. |               |     |           |     |                |     |      |

Figure 4. Characteristics of tSU:DAT

### 4 Tuning the timing using register I2Cx\_F

Configure the I2Cx\_F register to fix the timing issue and get the tSU:DAT using this formula:

SDA setup time = I2C module clock period (s) x mul x SDA setup value

Note to keep the SBRC bit field to be 0 in the I2Cx\_C2 register when using this solution. Get the SDA setup value from Table 1. I2C setup value on page 4.

| ICR<br>(hex)                                   | SDA Setup<br>Value                             | ICR<br>(hex) | SDA Setup<br>Value | ICR<br>(hex) | SDA Setup<br>Value | ICR<br>(hex) | SDA Setup<br>Value |

|------------------------------------------------|------------------------------------------------|--------------|--------------------|--------------|--------------------|--------------|--------------------|

| 0                                              | 2                                              | 10           | 16                 | 20           | 64                 | 30           | 256                |

| 1                                              | 3                                              | 11           | 20                 | 21           | 80                 | 31           | 320                |

| 2                                              | 3                                              | 12           | 20                 | 22           | 80                 | 32           | 320                |

| 3                                              | 4                                              | 13           | 24                 | 23           | 96                 | 33           | 384                |

| 4                                              | 4                                              | 14           | 24                 | 24           | 96                 | 34           | 384                |

| 5                                              | 5                                              | 15           | 28                 | 25           | 112                | 35           | 448                |

| 6                                              | 6                                              | 16           | 32                 | 26           | 128                | 36           | 512                |

| 7                                              | 9                                              | 17           | 44                 | 27           | 176                | 37           | 704                |

| 8                                              | 6                                              | 18           | 32                 | 28           | 128                | 38           | 512                |

| 9                                              | 8                                              | 19           | 40                 | 29           | 160                | 39           | 640                |

| 0A                                             | 10                                             | 1A           | 40                 | 2A           | 160                | 3A           | 640                |

| 0B                                             | 12                                             | 1B           | 48                 | 2B           | 192                | 3B           | 768                |

| 0C                                             | 12                                             | 1C           | 48                 | 2C           | 192                | 3C           | 768                |

| 0D                                             | 14                                             | 1D           | 56                 | 2D           | 224                | 3D           | 896                |

| 0E                                             | 16                                             | 1E           | 64                 | 2E           | 256                | 3E           | 1024               |

| 0F                                             | 22                                             | 1F           | 88                 | 2F           | 352                | 3F           | 1408               |

| ICR : register                                 | ICR : register value of bit field ICR of I2C_F |              |                    |              |                    |              |                    |

| SDA Setup Value : number of I2C function clock |                                                |              |                    |              |                    |              |                    |

#### Table 1. I2C setup value

#### NOTE

Table 1. I2C setup value on page 4 is just for reference. Set the I2Cx\_F to have a sufficient margin to meet the I<sup>2</sup>C timing.

For example, when the I2CxF is set to 0x02 and the I<sup>2</sup>C module clock frequency is 48 MHz, the setup time is calculated as:

#### Setup time = 1/48 MHz \* 1 \* 3 = 62.5 ns

When the I2Cx\_F value and the setup time value are bigger, they can get a longer margin by setting the big value to I2Cx\_F. However, this causes the I<sup>2</sup>C bus to drop due to clock stretching. Clock stretching happens in the below condition. At the start of a single-bit communication, the master sends the first SCL clock on the bus and the slave samples this pulse and compares it with its own I2Cx\_F configuration. If the slave's baud rate is lower than the master's baud rate, I<sup>2</sup>C IP begins to stretch the bus. For example, if the master's baud rate is 400 kHz and the slave's baud rate is configured to be 100 kHz by the I2Cx\_F register, the final I<sup>2</sup>C SCL bus period is composed by the slave's 100-kHz SCL low period time and master's 400-kHz SCL high period time. The bus period is 0.5 \* (1 / 100 K + 1 / 400 K) seconds, so the SCL bus is about 160 kHz.

It is recommended to set the slave's baud rate higher than the master baud rate and give a sufficient margin to meet the I<sup>2</sup>C timing.

This document introduces a way to tune the  $I^2C$  timing and meet the specifications by setting I2CxF correctly, which helps customers to solve  $I^2C$  timing issues.

### 6 References

- I<sup>2</sup>C-bus Specification, Version 6.0, 4th of April 2014

- KL16 Sub-Family Reference Manual with Addendum (document KL16P80M48SF4RM)

- Kinetis KL03 reference manual (document KL03P24M48SF0RM)

## 7 Revision history

Table 2. Revision history on page 5 summarizes the changes done to this document since the initial release.

### Table 2. Revision history

| Revision number | Date    | Substantive changes                                           |

|-----------------|---------|---------------------------------------------------------------|

| 0               | 03/2019 | Initial release                                               |

| 1               |         | Updated Tuning the timing using register<br>I2Cx_F on page 3. |

#### How To Reach Us

Home Page:

nxp.com

Web Support:

nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/

While NXP has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities on customer's applications and products, and NXP accepts no liability for any vulnerability that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, QorIQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamIQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, µVision, Versatile are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© NXP B.V. 2019.

#### All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

> Date of release: April 2019 Document identifier: AN12377

# arm