How to use i.MX RT Low Power Feature Rev. 2 — 10 January 2023

**Application note**

#### **Document information**

| Information | Content                                                                                                                          |

|-------------|----------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | i.MX RT Low Power Feature                                                                                                        |

| Abstract    | This document describes the low-power application design points on i.MX RT series. Low power is an important feature on i.MX RT. |

## 1 Introduction

This document describes the low-power application design points on i.MX RT series. Low power is an important feature on i.MX RT.

This application note uses RT1050 as an example and it can be a reference for RT1010, RT1024, RT1040, RT1050, RT1060, RT1064, and RT1060X.

## 2 Chip overview

This section provides main features of i.MX RT chips.

### 2.1 i.MX RT chip overview

The i.MX RT is a Cortex-M7 based chip that operates at speeds up to 600 MHz to provide a high CPU performance and the best real- time response.

- · Cortex-M7 based processor which can operates at speed up to 600 MHz.

- Advanced power management module with internal DCDC and LDO to reduce complexity of external power supply and simplifies power sequencing.

- Various memory interfaces, including SDRAM, Raw NAND FLASH, NOR flash, SD/ eMMC.

- A wide range of other interfaces for connecting peripherals, such as, WLAN, Bluetooth, GPS, displays, and camera sensors.

- Rich audio and video features, including LCD display, basic 2D graphics, camera interface, S/PDIF and I2S audio interface.

- Provide rich peripheral modules, such as SPI, I2C, CAN, Ethernet, Flex-Timers, ADC, and so on.

- Target at Industrial HMI, Motor Control and Home Appliance areas.

## 3 Low-power overview

The following section describes the power supply, run mode, and low-power mode.

### 3.1 Power supply

Table 1 lists the external power supply rails of i.MX RT.

| Power Rail                      | Description                               |

|---------------------------------|-------------------------------------------|

| DCDC_IN                         | Power for DCDC                            |

| VDD_HIGH_IN                     | Power for Analog                          |

| VDD_SNVS_IN                     | Power for SNVS and RTC                    |

| USB_OTG1_VBUS USB_OTG2_<br>VBUS | Power for USB VBUS                        |

| VDDA_ADC                        | Power for 12-bit ADC                      |

| VDDA_IN                         | Power for LDO 2P5 and LDO 1P1             |

| NVCC_SD0                        | Power for GPIO in SDIO1 bank (3.3 V mode) |

Table 1. External power supply rails...continued

| Power Rail                                                 | Description                               |

|------------------------------------------------------------|-------------------------------------------|

|                                                            | Power for GPIO in SDIO1 bank (1.8 V mode) |

| NVCC_SD1         Power for GPIO in SDIO2 bank (3.3 V mode) |                                           |

|                                                            | Power for GPIO in SDIO2 bank (1.8 V mode) |

| NVCC_GPIO                                                  | IO Power for GPIO in GPIO bank            |

| NVCC_EMC                                                   | IO Power for GPIO in EMC bank             |

## 3.2 Run mode definition

<u>Table 2</u> lists the run mode definitions.

| Run Mode       | Definition                                                                                                                                                                                                                     |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Overdrive run  | <ul> <li>CPU runs at 600 MHz, overdrive voltage to 1.275 V</li> <li>Bus frequency at 150 MHz</li> <li>All the peripheral are enabled and runs at target frequency</li> </ul>                                                   |

| Full speed run | <ul> <li>CPU runs at 528 MHz, full loading, lower voltage to 1.15 V</li> <li>Bus frequency at 132 MHz</li> <li>All peripheral are enabled and runs at target frequency</li> </ul>                                              |

| Low speed run  | <ul> <li>CPU runs at 132 MHz, lower voltage to 1.15 V</li> <li>Bus frequency at 66 MHz</li> <li>Some PLL are powered down</li> <li>20 % peripheral are active, others are in low power mode</li> </ul>                         |

| Low power run  | <ul> <li>CPU runs at 24 MHz, lower voltage to 0.95 V</li> <li>Bus frequency at 12 MHz</li> <li>All PLL are powered down, XTAL 24 M powered down, OSC RC 24 M enabled</li> <li>High-speed peripherals are power down</li> </ul> |

## Table 2. Run mode definition

## 3.3 Run mode configuration

Table 3 describes the run mode configuration.

|                 | Overdrive Run | Full Speed Run | Low Speed Run | Low Power Run |

|-----------------|---------------|----------------|---------------|---------------|

| CCM LPM Mode    | RUN           | RUN            | RUN           | RUN           |

| CPU Core        | 600 MHz       | 528 MHz        | 132 MHz       | 24 MHz        |

| L1 Cache        | ON            | ON             | ON            | ON            |

| FlexRAM         | ON            | ON             | ON            | ON            |

| SOC Voltage     | 1.275 V       | 1.15 V         | 1.15 V        | 0.95 V        |

| Analog LDO      | ON            | ON             | ON            | In Weak Mode  |

| 24 MHz XTAL OSC | ON            | ON             | ON            | OFF           |

| 24 MHz RC OSC   | OFF           | OFF            | OFF           | ON            |

| System PLL      | ON            | ON             | ON            | OFF           |

## How to use i.MX RT Low Power Feature

Table 3. Run mode configuration...continued

|              | Overdrive Run | Full Speed Run | Low Speed Run | Low Power Run        |

|--------------|---------------|----------------|---------------|----------------------|

| Other PLLs   | ON            | ON             | On as needed  | On as needed         |

| Module Clock | ON            | ON             | On as needed  | Peripheral clock off |

| RTC32K       | ON            | ON             | ON            | ON                   |

## 3.4 Low-power mode definition

Table 4 lists the low-power mode definition.

| Table 4. | Low-power | mode | definition |

|----------|-----------|------|------------|

|----------|-----------|------|------------|

| Low Power Mode | Definition                                                                                                                                                                                                                                                               |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Idle    | <ul> <li>CPU can automatically enter this mode when no thread running</li> <li>All the peripheral can remain active</li> <li>CPU only enter WFI mode, it will have its state retained so the interrupt response can be very short</li> </ul>                             |

| Low Power Idle | <ul> <li>Much lower power than System Idle mode, with longer exit time</li> <li>All PLL are shut off, analog modules running in low power mode</li> <li>All high-speed peripherals are power gated, low speed peripherals can remain running at low frequency</li> </ul> |

| Suspend        | <ul> <li>The most power saving mode with longest exit time</li> <li>All PLLs are shut off, XTAL are off, all clocks are shut off except 32 K clock</li> <li>All high-speed peripherals are power gated, low speed peripherals are clock gated</li> </ul>                 |

| SNVS           | <ul> <li>All SOC digital logic, analog modules are shut off only except SNVS domain</li> <li>32 KHz RTC is alive</li> </ul>                                                                                                                                              |

## 3.5 Low power mode configuration

Table 5 describes the low-power mode configuration.

|                    | System Idle | Low Power Idle | Suspend    | SNVS |

|--------------------|-------------|----------------|------------|------|

| CCM LPM Mode       | WAIT        | WAIT           | STOP       | _    |

| Arm Core (PDM7)    | WFI         | WFI            | Power Down | OFF  |

| L1 Cache           | ON          | ON             | Power Down | OFF  |

| FlexRAM (PDRET)    | ON          | ON             | ON         | OFF  |

| FlexRAM (PDRAM0)   | ON          | ON             | Power Down | OFF  |

| FlexRAM (PDRAM1)   | ON/OFF      | ON/OFF         | Power Down | OFF  |

| VDD_SOC_IN Voltage | 1.15 V      | 0.95 V         | 0.925 V    | OFF  |

| SYS PLL            | ON          | Power Down     | Power Down | OFF  |

| Other PLL          | Power Down  | Power Down     | Power Down | OFF  |

| 24 MHz XTAL OSC    | ON          | OFF            | OFF        | OFF  |

| 24 MHz RC OSC      | OFF         | ON             | OFF        | OFF  |

### How to use i.MX RT Low Power Feature

|                    | System Idle  | Low Power Idle | Suspend | SNVS |

|--------------------|--------------|----------------|---------|------|

| LDO 2P5            | ON           | OFF            | OFF     | OFF  |

| LDO 1P1            | ON           | OFF            | OFF     | OFF  |

| WEAK 2P5           | OFF          | ON             | OFF     | OFF  |

| WEAK 1P1           | OFF          | ON             | OFF     | OFF  |

| Band gap           | ON           | OFF            | OFF     | OFF  |

| Low-Power Band gap | ON           | ON             | ON      | OFF  |

| AHB Clock          | 33 MHz       | 12 MHz         | OFF     | OFF  |

| IPG Clock          | 33 MHz       | 12 MHz         | OFF     | OFF  |

| PER Clock          | 33 MHz       | 12 MHz         | OFF     | OFF  |

| Module Clocks      | ON as needed | ON as needed   | OFF     | OFF  |

| RTC 32 K           | ON           | ON             | ON      | ON   |

Table 5. Low-power mode configuration...continued

**Note:** Before entering low power mode, each module is enabled or disabled as described in the configuration table. However, for wake-up ensure to restore the settings.

#### 3.5.1 Wake-up source

Table 6 describes the wake-up source.

|                       | System Idle | Low Power Idle | Suspend           | SNVS               |

|-----------------------|-------------|----------------|-------------------|--------------------|

| GPIO wake-up          | YES         | YES            | YES               | - YES (1 PIN only) |

| RTC wake-up           | YES         | YES            | YES               | YES                |

| USB remote wake-up    | YES         | YES            | YES               | NO                 |

| Others wake-up source | YES         | YES            | ON <sup>[1]</sup> | NO                 |

Table 6. Wake-up source

[1] The peripherals, which can use RTC as the clock source, can be a wake-up source for the system. Such as: GPT,etc.

#### Note:

No matter whether the mode is System Idle, Low Power Idle, or Suspend, user has to enable the wake-up interrupt in GPC module else the wake-up fails.

The only pin that can wake-up the system in SNVS is GPIO5\_IO00. USB remote wakeup is not described in this document.

## 4 Power mode switch example

This section provides the application description, power mode switch menu

The power mode switch example is designed to simulate a customer low power application case.

Features:

- FreeRTOS and tickless feature support.

- Support all RUN and low power modes switch.

- Support run after WFI instruction and reset in suspend reset (controlled by chip).

- Simulate two running tasks and show task status in power mode switch.

### 4.1 Power mode switch menu

| 🛃 CON         | 158 - PuTTY                                                                           |

|---------------|---------------------------------------------------------------------------------------|

|               |                                                                                       |

| CPU wa        | tkeup source 0x1                                                                      |

| *****         | ********************                                                                  |

|               | Power Mode Switch Demo for iMXRT1050                                                  |

| *****         | *******************************                                                       |

| *****         | *************************                                                             |

| CPU:          | 600000000 Hz                                                                          |

| AHB:          | 600000000 Hz                                                                          |

| SEMC:         |                                                                                       |

| IPG:          | 150000000 Hz                                                                          |

| OSC:          | 2400000 Hz                                                                            |

| RTC:          | 32768 Hz                                                                              |

| ARMPLI        | .: 120000000 Hz                                                                       |

|               |                                                                                       |

| Task 2        | is working now                                                                        |

| Task 1        | is working now                                                                        |

| *****         | ##### Power Mode Switch Demo (build Oct 17 2017) #################################### |

| Co            | pre Clock = 60000000Hz                                                                |

| Pc            | wer mode: Over RUN                                                                    |

|               |                                                                                       |

|               | ***********************                                                               |

| CPU:<br>AHB:  | 60000000 Hz                                                                           |

| AHB:<br>SEMC: | 600000000 Hz<br>100000000 Hz                                                          |

| IPG:          | 150000000 Hz                                                                          |

| OSC:          | 24000000 Hz                                                                           |

| RTC:          | 32768 Hz                                                                              |

| ARMPLI        |                                                                                       |

| *****         | ************************                                                              |

|               |                                                                                       |

| Select        | ; the desired operation                                                               |

| Derect        | , the desired operation                                                               |

|               | A for enter: Over RUN - System Over Run mode (600MHz)                                 |

|               | B for enter: Full RUN - System Full Run mode (528MHz)                                 |

|               | C for enter: Low Speed RUN - System Low Speed Run mode (132MHz)                       |

|               | D for enter: Low Power RUN - System Low Power Run mode (24MHz)                        |

|               | E for enter: System Idle - System Wait mode                                           |

|               | F for enter: Low Power Idle - Low Power Idle mode                                     |

|               | G for enter: Suspend - Suspend mode                                                   |

| FIESS         | H for enter: SNVS - Shutdown the system                                               |

| Waitin        | ng for power mode select                                                              |

In this menu, user can switch power modes and wake-up from idle, suspend modes.

### 4.2 Task status show

When user select to transfer to a new power mode. The task status is shown.

1. Start working

| Task | 2 | is | working | now |

|------|---|----|---------|-----|

| Task | 1 | is | working | now |

Power mode transition For example, Overrun => System Idle

How to use i.MX RT Low Power Feature

```

Waiting for power mode select..

WorkingTask 2: Transfer from Over RUN to System Idle

WorkingTask 1: Transfer from Over RUN to System Idle

```

3. Wake-up transfer back to Overrun

```

Waiting for key press..

Switch SW8 from off to on to wake up.

WorkingTask 2: Transfer from System Idle to Over RUN

WorkingTask 1: Transfer from System Idle to Over RUN

Next loop

```

### 4.3 Wake-up source

Two wake-up sources can be selected for System Idle, Low Power Idle and Suspend mode, SW8 key (on EVK board) and GPT timer.

```

Waiting for power mode select..

WorkingTask 2: Transfer from Over RUN to System Idle

WorkingTask 1: Transfer from Over RUN to System Idle

Select the wake up source:

Press T for GPT - GPT Timer

Press S for switch/button SW8.

```

- SW8 user key wake-up.

- GPT timer wake-up.

When choose GPT timer as wake-up source, another menu will ask user to input a duration from 1s to 9s to wake up.

```

Select the wake up timeout in seconds.

The allowed range is 1s ~ 9s.

Eg. enter 5 to wake up in 5 seconds.

Waiting for input timeout value...

3

Will wakeup in 3 seconds.

WorkingTask 2: Transfer from Low Power Idle to Over RUN

WorkingTask 1: Transfer from Low Power Idle to Over RUN

```

## 5 Low power application design

This chapter will give some guides in designing a low power application. Also, we'll give some code examples about low power module enable and disable.

## 5.1 General description

Enter a low power mode is a set of enable/disable modules operations. The low power mode configuration should be paid attention.

|                    | System Idle  | Low Power Idle | Suspend    | SNVS |

|--------------------|--------------|----------------|------------|------|

| CCM LPM Mode       | WAIT         | WAIT           | STOP       | _    |

| Arm Core (PDM7)    | WFI          | WFI            | Power Down | OFF  |

| L1 Cache           | ON           | ON             | Power Down | OFF  |

| FlexRAM (PDRET)    | ON           | ON             | ON         | OFF  |

| FlexRAM (PDRAM0)   | ON           | ON             | Power Down | OFF  |

| FlexRAM (PDRAM1)   | ON/OFF       | ON/OFF         | Power Down | OFF  |

| VDD_SOC_IN Voltage | 1.15 V       | 0.95 V         | 0.925 V    | OFF  |

| SYS PLL            | ON           | Power Down     | Power Down | OFF  |

| Other PLL          | Power Down   | Power Down     | Power Down | OFF  |

| 24 MHz XTAL OSC    | ON           | OFF            | OFF        | OFF  |

| 24 MHz RC OSC      | OFF          | ON             | OFF        | OFF  |

| LDO 2P5            | ON           | OFF            | OFF        | OFF  |

| LDO 1P1            | ON           | OFF            | OFF        | OFF  |

| WEAK 2P5           | OFF          | ON             | OFF        | OFF  |

| WEAK 1P1           | OFF          | ON             | OFF        | OFF  |

| Band gap           | ON           | OFF            | OFF        | OFF  |

| Low Power Band gap | ON           | ON             | ON         | OFF  |

| AHB Clock          | 33 MHz       | 12 MHz         | OFF        | OFF  |

| IPG Clock          | 33 MHz       | 12 MHz         | OFF        | OFF  |

| PER Clock          | 33 MHz       | 12 MHz         | OFF        | OFF  |

| Module Clocks      | ON as needed | ON as needed   | OFF        | OFF  |

| RTC32K             | ON           | ON             | ON         | ON   |

Table 7. Low power configuration

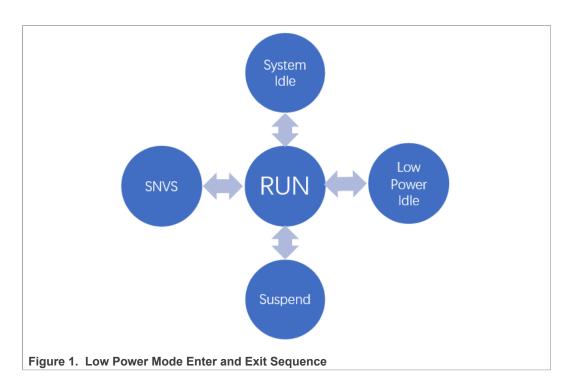

## 5.2 Low power mode enter and exit sequence

On i.MX RT, the chip can enter each low power mode and exit to rum mode.

AN12085 Application note

How to use i.MX RT Low Power Feature

### 5.2.1 Enter system idle mode

System Idle mode is a simple mode that the most modules' default settings do not need to be changed.

#### 5.2.1.1 How to enter

To enter system idle mode, the core frequency should be changed first and then unused PLLs should be powered down. Finally, the Core voltage also needs to be changed accordingly. Before executing WFI instruction, the used modules' DOZE bits need to be set.

Assume that the core voltage is reduced to 132 MHz. If the core frequency switches from 24 MHz to 132 MHz, the core voltage should be increased first.

#### 5.2.1.2 How to exit

To exit of System Idle mode is also simple. Adjust the core voltage first then enable PLLs.

### 5.2.2 Enter low power idle mode

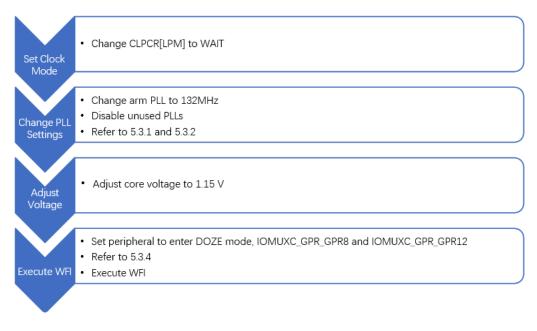

#### 5.2.2.1 How to enter

To enter Low Power Idle mode refer to the diagram below.

How to use i.MX RT Low Power Feature

5.2.2.2 How to exit

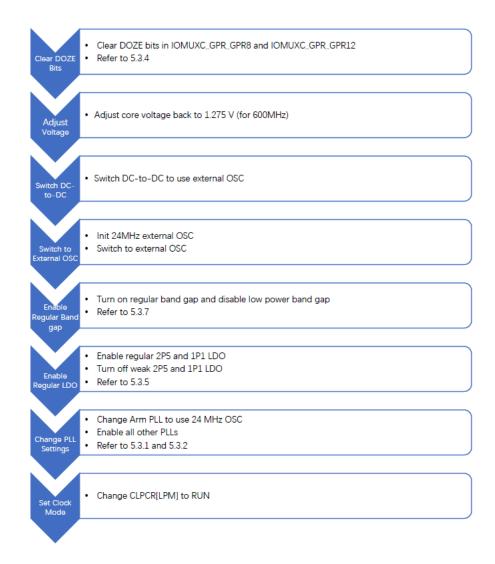

To exit Low Power Idle mode, refer to the diagram below.

How to use i.MX RT Low Power Feature

#### 5.2.3 Enter suspend mode

In suspend mode, as when set CLPCR[LPM] to STOP, the system will power down PLL don't need to adjust frequency.

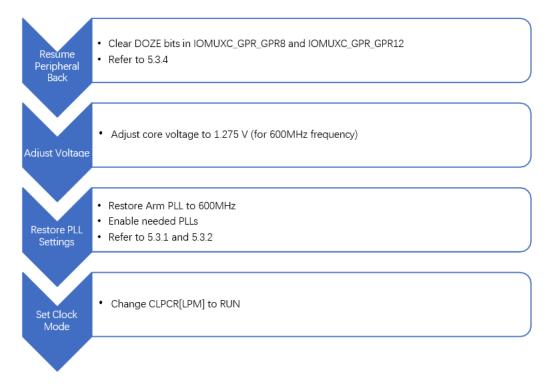

#### 5.2.3.1 How to enter

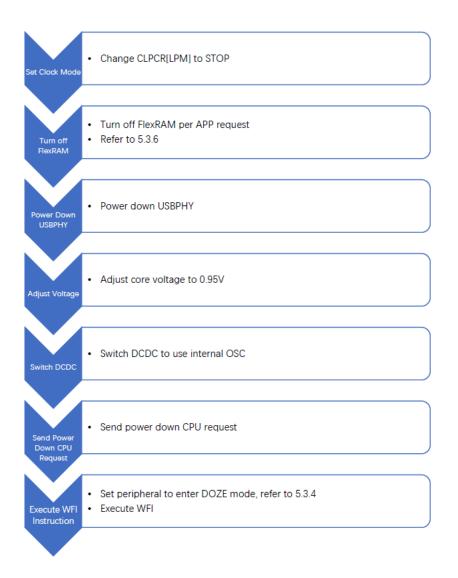

To enter Suspend mode refer to the diagram below.

How to use i.MX RT Low Power Feature

### 5.2.3.2 How to exit

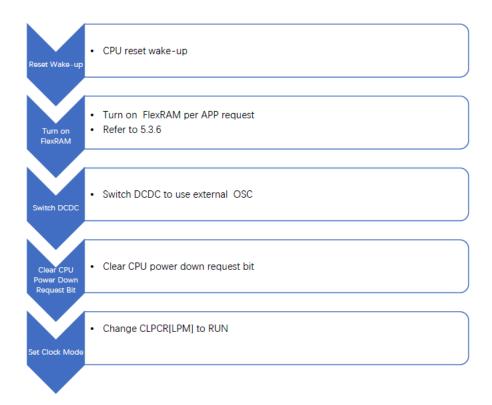

To exit Suspend mode, refer to the diagram below.

How to use i.MX RT Low Power Feature

### 5.2.4 SNVS mode

#### 5.2.4.1 How to enter

There are two methods to enter SNVS Mode. Software and Hardware. Software to enter SNVS mode, set SNVS\_LPCR[TOP] to 1.

Example code:

```

SNVS->LPCR |= SNVS_LPCR_TOP_MASK;

while (1) /* Shutdown */

{

}

```

Hardware to enter SNVS mode, long pressing ON/OFF button (SW2 on EVK Board)

#### 5.2.4.2 How to exit

Long pressing ON/OFF button (SW2 on EVK board) or using the wake-up pin.

This chip supports the use of a WAKEUP pin (GPIO5\_IO00 ALT5) to request main SoC power on to exit SNVS mode. To use it, follow the tips below:

- SNVS must be in Dumb PMIC mode (default, and must for on-chip DCDC)

- Configure IOMUXC\_SNVS to select WAKEUP pin ALT5 to mux it to GPIO5\_IO00

- Configure GPIO5 ICR to either low level or high level sensitive

- Set GPIO5 IMR bit0 to enable GPIO5\_IO00 interrupt

- Enter SNVS mode by SW or ON/OFF button, then on-chip DCDC will be off, and PMIC\_ON\_REQ pin will also go to low to notify outside

- Assert WAKEUP pin for at least two 32 kHz cycles (active high or low depends on GPIO5 ICR configuration), so that GPIO5 interrupt gets sampled by SNVS module

- SNVS will assert PMIC\_ON\_REQ pin high and on-chip DCDC begins to ramp on

- SoC power on procedure (except SNVS) begins (ROM boot, ...)

### 5.3 Low power design point

#### 5.3.1 How to change core frequency

When the frequency of Core needs to change the voltage of the Core also need to be change. There is a rule in changing core frequency and voltage.

- Increasing core frequency, voltage first, then frequency.

- Decreasing core frequency, frequency first, then voltage.

### 5.3.2 How to change PLL frequency

The sequence in changing PLL frequency is listed below:

- Set BYPASS and ENABLE bits to bypass clock.

- Set PLL clock divider.

- Clear PLL BYPASS bit.

- Wait for CCM operation finishes by testing CCM\_CDHIPR register

Example code:

```

/* Wait CCM operation finishes */

while (CCM->CDHIPR != 0)

{

}

}

```

**Note:** When the frequency of a PLL needs to be changed, BYPASS clock first, then change PLL frequency and at last switch PLL back.

#### 5.3.3 How to change clock source for SPI Flash and SDRAM

Usually under any RUN mode, if the SPI Flash or SDRAM are used to store code or data, changing the root clock's frequency is not recommended. It is dangerous to R/W SPI Flash or SDRAM while changing their clock source and frequency. If these operations have to do, the code should be run in On-Chip RAM.

#### 5.3.4 How to enable tickless low power feature in FreeRTOS

The FreeRTOS tickless idle mode stops the periodic tick interrupt during idle periods (periods when there are no application tasks that are able to execute), then makes a correcting adjustment to the RTOS tick count value when the tick interrupt is restarted.

Stopping the tick interrupt allows the microcontroller to remain in a deep power saving state until an interrupt occurs.

**Note:** MCU-SDK have already provided fsl\_tickless\_systick.c and fsl\_tickless\_gpt.c to implement tickles low power feature. User need to define configUSE\_TICKLESS\_IDLE in FreeRTOSConfig.h.

#### 5.3.4.1 Choose a FreeRTOS tick timer

Normally, the system tick module is used as the tick timer in FreeRTOS. On i.MX RT series the system tick module in Cortex-M7 core can support two timer sources, core clock and 100KHz clock, which is derived from 24M oscillator and divided to 100 KHz.

As in FreeRTOS, the time consumed in tickless stop will be compensated. The time consumed in tickles stop should not exceed maximum time duration (or FreeRTOS won't be able to know how much time to compensate). The code to calculate maximum duration counts is in function vPortSetupTimerInterrupt() in tickless code.

ulTimerCountsForOneTick = ( configSYSTICK\_CLOCK\_HZ / configTICK\_RATE\_HZ ); xMaximumPossibleSuppressedTicks = portMAX\_32\_BIT\_NUMBER / ulTimerCountsForOneTick;

For system tick module, *portMAX\_32\_BIT\_NUMBER* is 0x00FFFFFF and normally *configTICK\_RATE\_HZ* is set to 1000, meaning that each time tick duration is 1 ms.

So, in case choose core clock 600 MHz as clock source for system tick module, *ulTimerCountsForOneTick* will be 600000 and *xMaximumPossibleSuppressedTicks* will be 27.962025, which is also 27.962025 ms.

27.962025 ms is too short for a tickless duration. It means when in tickles stop, the system need to wake up every 27.962025 ms to compensate the time.

So, when consider using tickles low power in a FreeRTOS application, we'd better not use core clock as systick clock source, but use 100 KHz clock source. In this case, *ulTimerCountsForOneTick* will be 100 and

*xMaximumPossibleSuppressedTicks* will be 167772.15 ms, which is about 168 s. It's an acceptable duration here.

To use 100 KHz clock just need to define configSYSTICK\_CLOCK\_HZ in FreeRTOSConfig.h. #define configSYSTICK\_CLOCK\_HZ (10000U).

#### 5.3.4.2 Choose a tickless timer

As in tickless mode, FreeRTOS also need to compensate the consumed time, we need to use a timer with maximum time ticks that FreeRTOS can hold.

Systick is the first choice for this timer. But in i.MX RT, systick interrupt is not imported in GPC module. So systick interrupt can't wake-up the system, but only the Arm core. We need to select another timer as tickless timer.

The requirement for a tickless timer will be:

- Timer.

- Imported in GPC and can wake up the system.

- Work in System Idle, Low Power Idle and Suspend mode, even when core and all PLLs are power down.

GPT module can use 32K RTC (by setting GPT\_CR[CLKSRC] = 4) as clock source which can work in System Idle, Low Power Idle and Suspend mode.

#### 5.3.4.3 Hook functions before and after WFI instruction

FreeRTOS tickless idle mode provide two methods.

• vPortSuppressTicksAndSleep function.

In tickless mode, the system will call vPortSuppressTicksAndSleep function in idle task and pass the expect sleep time in microsecond as parameter.

User can implement a customized vPortSuppressTicksAndSleep and Idle task will call this function periodically.

- Advantage: Can handle WFI instruction as user required.

For example, as in suspend mode, the core is power down and thus, the wake-up is indeed a core reset. But as context can be saved, user can run code from WFI after reset. User need to setup a restore point to restore when reset.

In this case, it is easier for user to handle the WFI instruction in customer function.

- Disadvantage: User function need to calculate the tickles period and call vTaskStepTick to compensate the consumed time.

Note: User can take the vPortSuppressTicksAndSleep function in fsl\_tickless\_systick.c and fsl\_tickless\_gpt.c as a reference to compensate the time.

- Two hook functions to call before and after WFI instruction, configPRE SLEEP PROCESSING and configPOST SLEEP PROCESSING.

If user want to reuse vPortSuppressTicksAndSleep in fsl\_tickless\_systick.c and fsl\_tickless\_gpt.c, configPRE\_SLEEP\_PROCESSING and configPOST\_SLEEP\_PROCESSING can be implemented to change and restore modules for a lower power consumption.

- Advantage: Don't need to care about time compensation.

vPortSuppressTicksAndSleep function in fsl\_tickless\_systick.c and fsl\_tickless\_gpt.c

will do it for you.

- Disadvantage: Not very flexible. User can't proceed WFI instruction in own function.

In Power Mode Switch example, we use the second method to reuse vPortSuppressTicksAndSleep.

#### 5.3.5 Doze and IPG STOP signal

In order to reduce power consumption the Doze and Stop bits should be set and ask each module to enter Doze of Stop status before entering low power mode. In the example code, all supported peripherals' DOZE bits are enabled, but in an application the developer should know what modules are needed and enable corresponding modules' DOZE bits.

#### 5.3.5.1 Doze mode

For each module in doze mode, the AHB clock and serial clock domain will be gated off internally, but IPS Bus clock is not gated off. This mode is entered by setting corresponding DOZE bits in IOMUXC\_GPR\_GPR8 and IOMUXC\_GPR\_GPR12 and exited by clear corresponding bits in IOMUXC\_GPR\_GPR8 and IOMUXC\_GPR\_GPR12.

The Doze mode works in all low power modes. So the Doze bits should be set before entering any low power mode.

Example code:

Before entering low power mode:

```

IOMUXC_GPR->GPR8 = 0xaaaaaaaa;

IOMUXC GPR->GPR12 = 0x0000000a;

```

After wake-up:

```

IOMUXC_GPR->GPR8 = 0x00000000;

IOMUXC_GPR->GPR12 = 0x00000000;

```

#### 5.3.5.2 Stop mode

When system requires a peripheral device to enter stop mode, it will wait for all transactions to complete and return ACK handshake to system. After ACK handshake returned, the system can gate the AHB Bus clock, IPG Bus clock and serial clock in system level. There is no clock gating action internally. The mode is entered by setting corresponding **DOZE and STOP bits** in **IOMUXC\_GPR\_GPR8** and IOMUXC\_GPR\_GPR12, and system should wait for the accordingly bits in **IOMUXC\_GPR\_GPR4 and IOMUXC\_GPR\_GPR7** to be set. The Suspend mode works under stop mode. So that the Stop and Doze bits should be set before entering Suspend mode.

In the example code, all supported peripherals' STOP and DOZE bits are enabled, but in an application, the developer should be aware of what modules are needed and enable corresponding modules' STOP and DOZE bits.

Example code:

Before entering suspend mode:

```

IOMUXC_GPR->GPR4 = 0x00000011;

while ((IOMUXC_GPR->GPR4 & 0x00110000) != 0x00110000) {};

IOMUXC_GPR->GPR4 = 0x000036ff;

IOMUXC_GPR->GPR7 = 0x0000ffff;

IOMUXC_GPR->GPR8 = 0xfffcffff;

IOMUXC_GPR->GPR12 = 0x0000000a;

while ((IOMUXC_GPR->GPR4 & 0x36f90000) != 0x36f90000) {};

while ((IOMUXC_GPR->GPR7 & 0xffff0000) != 0xffff0000) {};

```

After wake-up:

```

IOMUXC_GPR->GPR4 = 0x00000000;

IOMUXC_GPR->GPR7 = 0x000000000;

IOMUXC_GPR->GPR8 = 0x00000000;

IOMUXC_GPR->GPR12 = 0x00000000;

```

Looking at the codes above, the STOP request is sent to EDMA and ENET first.

```

IOMUXC_GPR->GPR4 = 0x00000011;

while ((IOMUXC_GPR->GPR4 & 0x00110000) != 0x00110000){};

```

The reason is that EDMA and ENET are two modules that can act as a master on BUS and initiate transfer. If the code run on SPI Flash, the stop request shouldn't send to SPI Flash.

**Note:** Ensure that before entering Suspend mode, if corresponding module's STOP request is asserted, the system should wait for the acknowledge bit to be set. Or the system may fail to enter the Suspend mode.

If the code run in SDRAM and user wants to enter Suspend mode. SDRAM needs to wait a STOP signal to enter self-refresh mode. Here if a STOP request is sent to SDRAM and polling for the acknowledge bit to be asserted, the bit asserted might never get . Because

the code is running on SDRAM and the transaction on SDRAM can't STOP. In this case, the code or data should be run in SPI Flash or On-chip RAM.

#### Note:

Depending on whether clock gate and IP module's enable bit is set, each IP module may have a different behavior when the stop signal send to it.

- Some modules can acknowledge to stop signal even clock gate is OFF, for example PIT.

- Some modules can't acknowledge to stop signal when clock gate is OFF. But when clock gate is ON, it can acknowledge to stop signal, for example EDMA.

- Some modules can acknowledge to stop signal when clock gate is ON and the module's enable bit is ON. Currently only CAN is of this type.

### 5.3.6 How to enable weak analog LDO

There are two types Analog LDO on i.MX RT, regular LDO and low power weak LDO. The 1.1 V and 2.5 V LDO includes an alternate, self-biased, low-precision, weak regulator which can be enabled for applications needing to keep the 1.1 V and 2.5 V output voltage alive during low-power modes where the main regulator and its associated global band gap reference module are disabled. Using the weak LDO can reduce power consumption under Low Power Idle mode.

• Enable Weak Analog LDO

```

/* Enable regular 2P5 and wait it stable */

PMU->REG_2P5_SET = PMU_REG_2P5_ENABLE_LINREG_MASK;

while ((PMU->REG_2P5 & PMU_REG_2P5_OK_VDD2P5_MASK) == 0)

{

}

/* Turn off weak 2P5 */

PMU->REG_2P5_CLR = PMU_REG_2P5_ENABLE_WEAK_LINREG_MASK;

/* Enable regular 1P1 and wait for stable */

PMU->REG_1P1_SET = PMU_REG_1P1_ENABLE_LINREG_MASK;

while ((PMU->REG_1P1 & PMU_REG_1P1_OK_VDD1P1_MASK) == 0)

{

/* Turn off weak 1P1 */

PMU->REG_1P1_CLR = PMU_REG_1P1_ENABLE_WEAK_LINREG_MASK;

```

#### Disable Weak Analog LDO

```

/* Enable weak 2P5 and turn off regular 2P5 */

PMU->REG_2P5 |= PMU_REG_2P5_ENABLE_WEAK_LINREG_MASK;

PMU->REG_2P5 &= ~PMU_REG_2P5_ENABLE_LINREG_MASK;

/* Enable weak 1P1 and turn off regular 1P1 */

PMU->REG_1P1 |= PMU_REG_1P1_ENABLE_WEAK_LINREG_MASK;

PMU->REG_1P1 &= ~PMU_REG_1P1_ENABLE_LINREG_MASK;

```

#### 5.3.7 How to disable OCRAM power

The i.MX RT1050 chips have On-Chip FlexRAM which is shared by I-TCM, D-TCM and general purpose On-Chip RAM (OCRAM). The FlexRAM manages a big on-chip RAM array. The FlexRAM have 16 RAM banks, which are divided into Bank0, FlexRAM0 (Bank 1 - 7) and FlexRAM1 (Bank 8 -15). Description of OCRAM banks is listed below.

| Table 8. | Description | of OCRAM | banks |

|----------|-------------|----------|-------|

|----------|-------------|----------|-------|

|                              | Bank 0                                   | Bank 1-7                                                                                          | Bank 8-15                                                             |

|------------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Alias Name                   | Bank0                                    | FlexRAM0                                                                                          | FlexRAM1                                                              |

| Power<br>Domain              | SNVS                                     | PDRAM0                                                                                            | PDRAM1                                                                |

| Power Gate<br>Bit            | N/A                                      | GPC_CNTR[PDRAM0_<br>PGE]                                                                          | PGC_MEGA_CTRL[PCR]                                                    |

| Power Gate<br>Default Value  | N/A                                      | 1 (Will power down in low power mode)                                                             | 0 (Won't power down)                                                  |

| LPM MODE<br>ON/OFF<br>Status | ON                                       | Controllable                                                                                      | Controllable                                                          |

| Power down<br>moment         | In SNVS mode,<br>bank0 is power<br>down. | GPC_CNTR[PDRAM0_<br>PGE] is set and Bank<br>1-7 will be off when core<br>executes WFI instruction | PGC_MEGA_CTRL[PCR] is<br>set and Bank 8-15 will be off<br>immediately |

**Note:** Pay attention to that when the power gate bit is set, FlexRAM0 will not be OFF immediately, unless core execute WFI instruction. But FlexRAM1 will be OFF immediately.

Code examples:

• Power Down FlexRAM0 and FlexRAM1

```

/* Turn off FlexRAM1 */

PGC->MEGA_CTRL |= PGC_MEGA_CTRL_PCR_MASK;

/* Turn off FlexRAM0*/

GPC->CNTR |= GPC_CNTR_PDRAM0_PGE_MASK;

```

• Power on FlexRAM0 and FlexRAM1

```

/* Turn on FlexRAM1 */

PGC->MEGA_CTRL &= ~PGC_MEGA_CTRL_PCR_MASK;

/* Turn on FlexRAM0*/

GPC->CNTR &= ~GPC_CNTR_PDRAM0_PGE_MASK;

```

#### 5.3.8 Band gap switch

In i.MX RT, there are two band gap modules, regular band gap and low power band gap. In a low-power application, the low power band gap should be used before entering low power wait or stop state.

**Note:** In suspend mode, STOP mode will be set in CLPCR, which will help to switch band gap to low power band gap automatically in low power stop.

Code example:

Switch band gap to low power band gap:

```

/* Switch band gap */

PMU->MISC0_SET = 0x00000004;

XTALOSC24M->LOWPWR_CTRL_SET =

XTALOSC24M_LOWPWR_CTRL_LPBG_SEL_MASK;

PMU->MISC0_SET = CCM_ANALOG_MISC0_REFTOP_PWD_MASK;

Switch band gap back to regular band gap:

```

```

/* Restore band gap */

/* Turn on regular band gap and wait for stable */

CCM_ANALOG->MISC0_CLR = CCM_ANALOG_MISC0_REFTOP_PWD_MASK;

while ((CCM_ANALOG->MISC0 &

CCM_ANALOG_MISC0_REFTOP_VBGUP_MASK) == 0)

{

/* Low power band gap disable */

XTALOSC24M->LOWPWR_CTRL_CLR =

XTALOSC24M_LOWPWR_CTRL_LPBG_SEL_MASK;

PMU->MISC0_CLR = 0x00000004;

```

### 5.3.9 Enable DCM mode of DCDC

DCDC module provides a Discontinuous Conduction Mode (DCM) and Continuous Conduction Mode (CCM). It can operate on the CCM mode or DCM mode under Run mode. Which mode is used depends on the level of the load current. Usually the CCM mode is used when the chip under Run mode and DCM mode is used when the chip under low power mode. The DCM mode also can be used if the power consumption is low under RUN mode. DCM mode can reduce current of DCDC\_IN, but DCDC\_OUT current will not change.

**Note:** Because discontinuous conduction mode(DCM) can increase the efficiency of DCDC in case of low current loading, it is always recommended.

The DCM mode should be set before entering low power mode. The details steps as flowing:

```

pwd_zcd=0x0

pwd_cmp_offset=0x0

loopctrl_en_rcscale=0x4

DCM SET CTRL=1'b1

```

Don't forget to restore to CCM mode when waked up. And enable CCM mode:

```

pwd_zcd=0x1

pwd_cmp_offset=0x0

loopctrl en rcscale=0x3

```

#### 5.3.10 Enable and disable RBC bit

In Suspend mode, the RBC bit need to be set before executing WFI instruction and cleared after wake-up. The RBC bit is in CCM\_CCR register. There is a VSTBY bit in CCM\_CLPCR, it will change voltage to standby voltage (DCDC will enter power saving mode). This bit needs to be set in Low Power Idle mode and Suspend Mode.

Enabling RBC\_EN and VSTBY will ask analog to enter low power in STOP. Two points need to be noted in enabling and disabling RBC\_EN bit.

- GPC interrupts need to be masked before setting the bit.

- A delay (3us) is needed after setting the bit.

Example:

• Enable RBC\_EN:

/\* Mask all GPC interrupts before enabling the RBC counters to

AN12085

21 / 26

#### How to use i.MX RT Low Power Feature

```

avoid the counter starting too early if an interrupt is

already pending.

*/

for (i = 0; i < LPM GPC IMR NUM; i++)

gpcIMR[i] = GPC->IMR[i];

GPC->IMR[i] = 0xFFFFFFFU;

}

/* Enable the RBC bypass counter here to hold off the

interrupts. RBC counter

* = 32 (1ms). Minimum RBC delay should be 400us.

* /

CCM->CCR = (CCM CCR RBC EN MASK | CCM CCR COSC EN MASK |

CCM CCR OSCNT(0xAF));

/* Recover all the GPC interrupts. */

for (i = 0; i < LPM GPC IMR NUM; i++)</pre>

{

GPC->IMR[i] = gpcIMR[i];

}

/* Now delay for a short while (3usec) Arm is at 528MHz

at this point

* so a short loop should be enough. This delay is

required to ensure that

* the RBC counter can start counting in case an

interrupt is already pending

* or in case an interrupt arrives just as Arm is about

to assert DSM request.

* /

for (i = 0; i < 22 * 24; i++)

{

NOP();

}

```

Disable RBC\_EN:

```

/* Mask all GPC interrupts before disabling the RBC counters

for (i = 0; i < LPM GPC IMR NUM; i++)</pre>

{

gpcIMR[i] = GPC->IMR[i];

GPC->IMR[i] = 0xFFFFFFFU;

/* Disable the RBC bypass counter */

CCM->CCR &= ~CCM CCR RBC EN MASK;

CCM->CCR &= ~CCM CCR REG BYPASS COUNT MASK;

/* Now delay for 2 CKIL cycles (61usec). Arm is at 528MHz

at this point

* so a short loop should be enough.

* /

for (i = 0; i < 528 * 22; i++)

{

NOP();

}

/* Recover all the GPC interrupts. */

for (i = 0; i < LPM GPC IMR NUM; i++)</pre>

```

AN12085

#### How to use i.MX RT Low Power Feature

GPC->IMR[i] = gpcIMR[i];

### 5.3.11 Workaround for ERR007265

}

Errata ERR007265 describes about a case that SoC may fail to enter a low power mode.

ERR007265: CCM: When improper low-power sequence is used, the SoC enters low power mode before the Arm core executes WFI.

Software workaround:

- 1. Software should trigger GPR\_IRQ to be always pending by setting IOMUX\_GPR1\_GINT.

- Software should then unmask GPR\_IRQ in GPC before setting CCM Low-Power mode.

- Software should mask GPR\_IRQ right after CCM Low-Power mode is set (set bits 0-1 of CCM\_CLPCR).

#### 5.3.12 How to run after suspend reset

#### 5.3.12.1 Introduction

Suspend mode is a low power mode with the least power. But as the core power down, the wake-up is a reset wake-up. In System Idle and Low Power Idle mode, when wake-up the code can continue run after WFI instruction which is convenient but can't get the least power consumption. The least power consumption can get under Suspend mode. After reset, the core can detect whether it is a suspend reset (via PGC->CPU\_SR[PSR]). If the system wants to run the code after WFI instruction, the restore data can be saved on OCRAM and the start address's offset is 32KB.That means FlexRAM0 cannot power down in Suspend mode.

#### 5.3.12.2 SDRAM data storage suggestion

In most applications, user may want to use SDRAM to store data. SDRAM can enter self-refresh mode automatically in Suspend and data won't be lost.

**CAUTION:** Before entering Suspend mode, a STOP request should be sent to SDRAM to ask SDRAM to enter self-refresh mode. It is important to avoid accessing SDRAM and use variable in OCRAM.

## 6 Reference

- 1. i.MX RT 1050 Reference Manual

- 2. Arm Cortex M7 Reference Manual

## 7 Revision history

| Revision number | Date          | Substantive changes                       |

|-----------------|---------------|-------------------------------------------|

| 0               | November 2017 | Initial release                           |

| 1               | January 2019  | Updated the design of low-power solutions |

AN12085

## **NXP Semiconductors**

# AN12085

## How to use i.MX RT Low Power Feature

| Revision number | Date            | Substantive changes |

|-----------------|-----------------|---------------------|

| 2               | 10 January 2023 | Updated Section 1   |

#### How to use i.MX RT Low Power Feature

## 8 Legal information

## 8.1 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

## 8.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Suitability for use in non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <u>PSIRT@nxp.com</u>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

## 8.3 Trademarks

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

### How to use i.MX RT Low Power Feature

## Contents

| 1        | Introduction2                               |

|----------|---------------------------------------------|

| 2        | Chip overview2                              |

| 2.1      | i.MX RT chip overview2                      |

| 3        | Low-power overview2                         |

| 3.1      | Power supply2                               |

| 3.2      | Run mode definition3                        |

| 3.3      | Run mode configuration3                     |

| 3.4      | Low-power mode definition4                  |

| 3.5      | Low power mode configuration4               |

| 3.5.1    | Wake-up source                              |

| 4        | Power mode switch example                   |

| 4.1      | Power mode switch menu                      |

| 4.2      | Task status show                            |

| 4.3      | Wake-up source                              |

| 5        | Low power application design7               |

| 5.1      | General description                         |

| 5.2      | Low power mode enter and exit sequence      |

| 5.2.1    | Enter system idle mode                      |

| 5.2.1.1  | How to enter                                |

| 5.2.1.1  | How to exit                                 |

| 5.2.2    | Enter low power idle mode                   |

| 5.2.2.1  | How to enter10                              |

| 5.2.2.1  |                                             |

|          | How to exit                                 |

| 5.2.3    | Enter suspend mode                          |

| 5.2.3.1  | How to enter                                |

| 5.2.3.2  | How to exit                                 |

| 5.2.4    | SNVS mode                                   |

| 5.2.4.1  | How to enter14                              |

| 5.2.4.2  | How to exit                                 |

| 5.3      | Low power design point15                    |

| 5.3.1    | How to change core frequency15              |

| 5.3.2    | How to change PLL frequency15               |

| 5.3.3    | How to change clock source for SPI Flash    |

|          | and SDRAM15                                 |

| 5.3.4    | How to enable tickless low power feature in |

|          | FreeRTOS15                                  |

| 5.3.4.1  | Choose a FreeRTOS tick timer 16             |

| 5.3.4.2  | Choose a tickless timer16                   |

| 5.3.4.3  | Hook functions before and after WFI         |

|          | instruction16                               |

| 5.3.5    | Doze and IPG STOP signal17                  |

| 5.3.5.1  | Doze mode17                                 |

| 5.3.5.2  | Stop mode18                                 |

| 5.3.6    | How to enable weak analog LDO19             |

| 5.3.7    | How to disable OCRAM power19                |

| 5.3.8    | Band gap switch20                           |

| 5.3.9    | Enable DCM mode of DCDC21                   |

| 5.3.10   | Enable and disable RBC bit                  |

| 5.3.11   | Workaround for ERR007265                    |

| 5.3.12   | How to run after suspend reset              |

| 5.3.12.1 | Introduction                                |

| 5.3.12.2 |                                             |

| 6        | Reference                                   |

|          |                                             |

| <b>Revision history</b> |  |

|-------------------------|--|

| Legal information       |  |

7 8

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

#### © 2023 NXP B.V.

#### All rights reserved.

For more information, please visit: http://www.nxp.com