# S12ZVM Family in 48 V Applications

by: NXP Semiconductors

## **1** Introduction

Nowadays, the number of hybrid vehicles is increasing constantly. It is expected by the year 2020, the amount of hybrid electric vehicles (HEVs) could represent the 15% of the automotive market. Most of the HEV systems operate with 48 V power-train architecture.

It is necessary to understand needs and requirements of a high-voltage system to provide the best solutions for 48 V automotive applications.

This application note contains useful information to enable <u>S12ZVM family</u> into a 48 V motor control system. The aim of this document is to give an accurate description of how our devices fully support the standard LV 148.

This document considers different design options to achieve the best solution for a general motor control application BLDC or PMSM.The key approach is to add the selected external components that extend the device's operational voltage range.

## 2 S12ZVM Family

#### Contents

| 1 Introduction 1                                              |

|---------------------------------------------------------------|

| 2 S12ZVM Family1                                              |

| 3 Norms2                                                      |

| 3.1 Operating voltage2                                        |

| 4 Supply line3                                                |

| 5 General block application3                                  |

| 5.1 Drive BLDC/PMSM<br>through PMF outputs4<br>5.1.1 Software |

| considerations5<br>5.2 Drive BLDC/PMSM                        |

| through GDU outputs5<br>5.2.1 Software                        |

| considerations5                                               |

| 6 Communication physical layer 6                              |

| 6.1 Block diagram6<br>6.2 Electric diagram7                   |

| 7 GDU fault detections7                                       |

| 8 References7                                                 |

The S12ZVM is a 16-bit microcontroller which is a monolithic solution for motor control applications, integrating several high-voltage analog blocks. The device offers a high-grade of system testability.

Not only reset status flagging and many failure status bits are implemented for module, but also sophisticated temperature and battery voltage monitoring capabilities are offered. Some of the advantages in S12ZVM systems are:

- · Improved accuracy of position sensing due to integration level

- · Dual ADC concept supports high accuracy of position sensing

- Flexible operation range down to 3.5 V Vsup with selectable boost option

- Integrated charge pump supports 100% duty cycle

- · High PMF resolution and speed up to 50 kHz covers large-range of motor applications

- · High level of safety

- · Integrated desaturation and overcurrent comparators

- · Protection against unintended clock and gate drive unit register access

- Flash/EEPROM margin read for run time cell status check

- High-grade of system testability

- · High-grade of failure status reporting and reset status flagging

Norms Operating voltage

- Sophisticated temperature and voltage monitoring capabilities

- · High-speed SPI or 250 kbaud LIN usable as test interface

- · Continuous automotive quality improvement

- · Reduction of BOM and soldering points in system

- · Robust 180nm technology with zero defect strategy

- NVM, RAM ECC, and protection

## 3 Norms

There is not an official norm for 48 V automotive systems. The standard in which are bases all the system requirements and specifications is the LV 148. This standard was described by German OEMs in order to set a base for 48 V systems.

### 3.1 Operating voltage

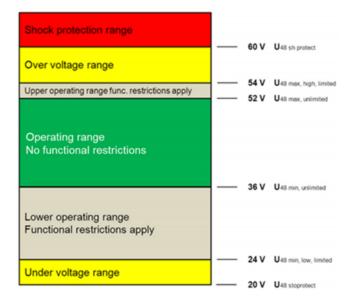

The normal operation of a 48 V is bases in the range between 36 V and 52 V. In the upper limits, we found: 54 V is the maximum voltage where the over-voltage protection should be active and for voltages above 60 V, an electric shock protection needs to be enabled.

For voltages below 36 V, there is an operating range with functional limitation and for voltages below 20 V, a storage protection should be enabled such as save important information into NVM.

Figure 1. Definitions of steady-state voltage ranges

The LV 148 provides with the premises regarding a 48 V connection:

- It is not necessary to have an electronic shock protection for a DC voltage under 60 V.

- A single malfunction must not result in a short circuit between 48 V and 12 V on the board electrical system.

- There is a common ground between 12 V / 24 V and 48 V systems which is connected by spatially separated ground terminals.

- The loss of ground of a 48 V component must not lead in the disturbance or destruction of communication networks or electrical systems.

• No component might lead to a transition into the over-voltage range (for example, in the event of a load dump or due to resonance rises)

## 4 Supply line

The power supply can be taken even from 48 V line and 12 V line.

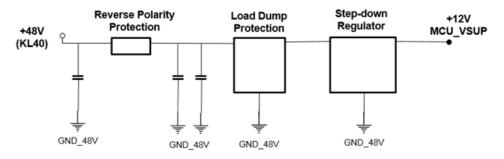

#### S12ZVM VSUP connected through 48 V line:

When S12ZVM is supplied from **48 V**, it is line is needed to reduce the voltage with a step-down regulator and to add protection such as reverse polarity and load dump. As the MCU is already in the 48 V line, it is not needed to add a fly-back converter to divide the 48 V and 12 V lines.

Figure 2. S12ZVM VSUP connected through 48 V line

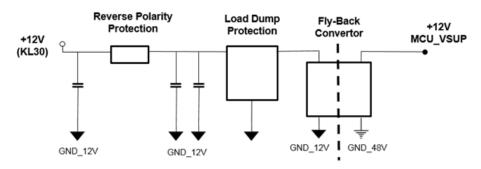

#### S12ZVM VSUP connected through 12 V line:

When S12ZVM is supplied from **12 V** line, it is needed to add a fly-back converter and to isolate the **12 V** line from the **48 V** line, this is because the MCU must be grounded to GND\_48V line for motor control applications.

Figure 3. S12ZVM VSUP connected through 12 V line

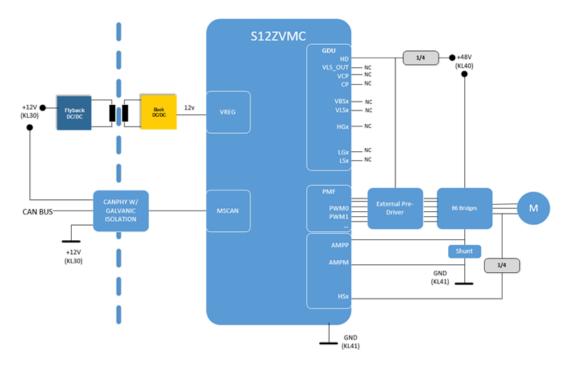

### **5** General block application

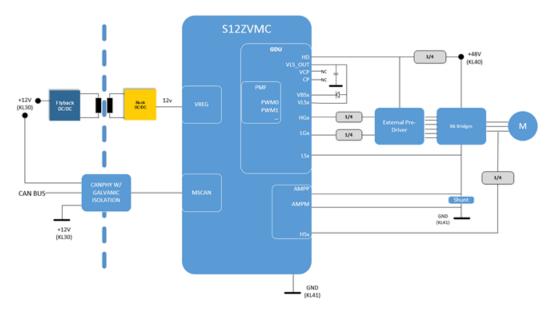

Using S12ZVM family along with third-party devices, it is possible develop applications for emerging 48 V systems. As S12ZVMC's GDU supply voltage range is up to 20 V on its HD pin, it is necessary to add an external gate drive unit which can manage a supply voltage range from 36 V to 52 V.

There are two main configurations for 48 V applications with S12ZVM:

- Drive BLDC/PMSM through PMF outputs

- Drive BLDC/PMSM motors through GDU outputs

### 5.1 Drive BLDC/PMSM through PMF outputs

In this configuration, almost all the pins from GDU are not connected, the external pre-driver is controlled directly by the PWM outputs:

| Pin | PWM channel |

|-----|-------------|

| PP0 | PWM_0       |

| PP1 | PWM_1       |

| PP2 | PWM_2       |

| РТО | PWM_3       |

| PT1 | PWM_4       |

| РТ2 | PWM_5       |

#### Table 1. Mapping of S12ZVM's pinout to external gate drivers

This means that the additional functionalities of pins PP0:PP2, PT0:PT2 such as KWI, SPI communication, timer functions, etc. will not remain available while PWM outputs are connected to external gate-driver and working for a motor control application.

Figure 4. External Pre-Driver controlled by PWM outputs

NOTE

This block diagram is the representation of one phase. Consider the connections for: VBSx, VLSx, HGx, etc. for the three phases.

This configuration allows a clear connection between external pre-driver and motor control signals, allowing also the measurement of phase voltages through HSx pins and phase currents though shunt resistor.

Due to the use of an external gate driver, some of our fault protections are disable, but some others remain are enable. For more details, see GDU fault detections on page 7.

### 5.1.1 Software considerations

Even if GDU pins are not used, it is important to keep set the GDU enable bit in order of use the internal operational amplifiers. It's also necessary to modify the bits PWMPRR1-0 to 0b01. With this setting, all the PMF channels are connected to PWM pins.

### 5.2 Drive BLDC/PMSM through GDU outputs

In this configuration, GDU outputs are used to control the external pre-driver. This solution brings advantages and disadvantages. The principal advantage is that PWM outputs functionalities are not sacrificed to control the external pre-driver, but this implies the use of additional components to reduce the output voltage from the gate drivers to the external pre-driver inputs. Another consideration is the intrinsic delay time introduced by the GDU to the pre-driver inputs (tdelon and tdeloff).

Most of the external pre-drivers accept an input (logical) voltage from 2.5 V to 10 V. For this reason, it is necessary to add a voltage divider of 1/4 from the HG and LG pins to fit with this requirement.

In the case of the HGx pin where the output voltage is around 20 V, the voltage going into the pre-driver's inputs will be around 5 V. For LGx pins the output voltage is 12 V so the voltage going into pre-driver inputs would be 3 V.

**NOTE** This block diagram is the representation of one phase. Consider the connections for: VBSx, VLSx, HGx, etc. for the three phases.

As previous configuration, some of the GDU faults remain active. For more details, see GDU fault detections on page 7.

### 5.2.1 Software considerations

Even if GDU pins are not used, it is important to keep set the GDU enable bit in order to use the internal operational amplifiers.

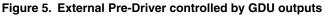

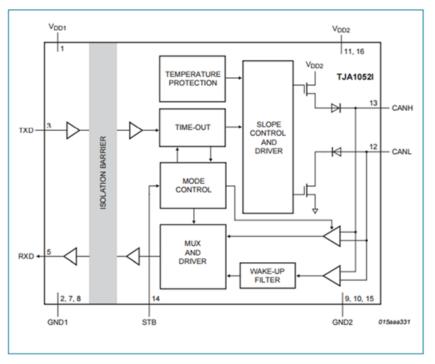

## 6 Communication physical layer

This application requires an external component capable to isolate 12 V and 48 V ground. The NXP's TJA1052i CAN Transceiver combines this protection with outstanding performance especially for high-speed (up to 1 Mbit/s) CAN applications in the automotive industry. The TJA1052i supplies the differential transmit and receive capability to a CAN protocol controller in a microcontroller. By integrating the galvanic isolation with the transceiver, this solution eliminates the need for standalone isolation and improves reliability and system performance parameters such as loop delay.

### 6.1 Block diagram

Figure 6. TJA1052 block diagram

#### 6.2 Electric diagram

Figure 7. Typical application with TJA1052

### 7 GDU fault detections

Using an external Pre-Driver implies that not of all the internal GDU faults remains active, the faults that can continue being monitored are:

- Over current condition through internal ADC channel/opamp

- · Over current condition through over-current comparator

- Over-voltage on pin HD

In "Dive BLDC/PMSM through GDU outputs" configuration, it could be possible detect short circuits between HS to DC bus or HS to ground through desaturation comparators on three phases.

However, some external pre-drivers have additional protections, some of them can be:

- High temperature

- Over-current detection

- Over-voltage detection

- Under-voltage detection

## 8 References

- 1. Galvanic Isolated high-speed CAN transceiver, TJA1052I data sheet by NXP semiconductors.

- 2. LV 148 internal 48 V VW standard, NDE\_VW82148-1\_LV148, by representatives of the automotive manufacturers.

- 3. NXP Automotive Products Microcontrollers and Processors 16-bit S12 MagniV.

#### How To Reach Us

Home Page:

#### nxp.com

Web Support:

#### nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/ SalesTermsandConditions.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT. MIFARE4MOBILE. MIGLO. NTAG. ROADLINK. SMARTLX. SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, QorIQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. ARM, AMBA, ARM Powered, Artisan, Cortex, Jazelle, Keil, SecurCore, Thumb, TrustZone, and µVision are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. ARM7, ARM9, ARM11, big.LITTLE, CoreLink, CoreSight, DesignStart, Mali, mbed, NEON. POP. Sensinode, Socrates, ULINK and Versatile are trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© 2017 NXP B.V.

AN11967 Rev. 0 May 2017