## **AN11741**

# How to design an antenna with DPC Rev. 1.0 — 24 November 2015

**Application note COMPANY PUBLIC**

#### **Document information**

| Info     | Content                                                                                                                                                                   |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords | DPC, Dynamic Power Control, Symmetrical antenna                                                                                                                           |

| Abstract | This document describe the "symmetrical" antenna design, which is must be used together with the Dynamic Power Control (DPC), and therefore is called DPC antenna tuning. |

## How to design an antenna with DPC

#### **Revision history**

| Rev | Date     | Description   |

|-----|----------|---------------|

| 1.0 | 20151124 | First release |

## **Contact information**

For more information, please visit: <a href="http://www.nxp.com">http://www.nxp.com</a>

#### How to design an antenna with DPC

#### 1. Introduction

The Dynamic Power Control (DPC) feature of the PN5180 offers an improved overall RF performance. This requires the antenna to be "symmetrically" tuned and it requires the Automatic Gain Control (AGC) to correlate with the driver current ITVDD. And it requires the dynamic power control to be properly calibrated.

This document describes the "symmetrical" antenna tuning, called "DPC antenna tuning", in principle (section 2) and it describes the simple tuning procedure itself (section 3).

The PN5180 GUI supports the process of the DPC calibration including the correlation test, the calibration itself and the PCD TX shaping. The steps to calibrate the DPC and optimize the PN5180 registers are described in [2].

**Warning:** A wrong antenna tuning or a bad DPC calibration might drive a too strong HF field and even might destroy the PN5180.

## 2. DPC antenna tuning principle and advantages

#### 2.1 Principle

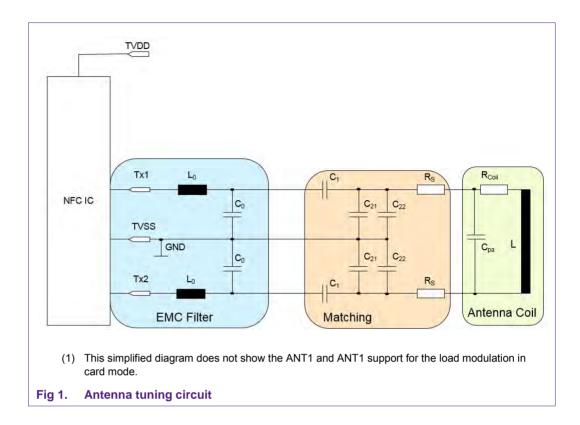

The antenna design for the PN5180 in principle uses the circuitry as shown in Fig 1. The blocks for the tuning procedure, the EMC filter, the matching block and the antenna coil itself, are the same as known with other NFC Reader ICs, and as described in [1].

#### How to design an antenna with DPC

However, the main difference between a standard "asymmetrical" antenna tuning and the improved "symmetrical" antenna tuning using the DPC is the EMC cut off frequency, which is much lower than in the standard antenna tuning.

<u>Note:</u> In case the NFC Reader has to support all NFC modes (including the card mode), the ANT1 and ANT2 pins have to be connected as described in [1] for the load modulation. There is no difference other than the values of the capacitors used to connect. For the standard tuning as well as for the DPC antenna tuning the impact of the ANT1 and ANT2 pins have to be considered using the  $10\Omega$  resistor across ANT1 and ANT2 during the impedance measurement.

## 2.2 "Symmetrical" versus "asymmetrical" tuning

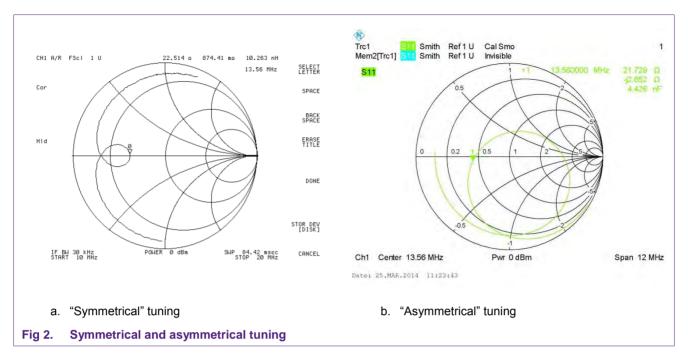

In the standard antenna design (Fig 1b) we use a cut off frequency of up to 21MHz to provide a proper detuning and loading behavior of then antenna (for details refer to [1]). This high cut off frequency helps to meet the minimum and maximum field strength limits with normal antennas, but it does not provide the optimum transfer function.

#### How to design an antenna with DPC

The improved DPC antenna tuning uses a cut off frequency of

$$f_{EMC} \approx 14.3...14.7MHz$$

(1)

With such low cut off frequency the impedance changes to a "symmetrical" impedance as shown in Fig 2a. This tuning improves the transfer function, which

- allows to use a higher Q factor

- increases the operating distance

- · allows to use smaller antennas

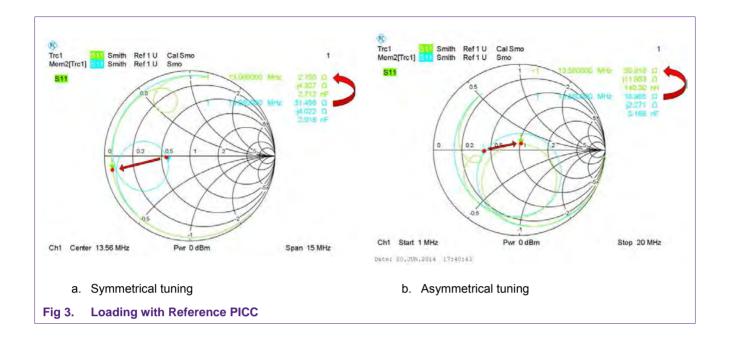

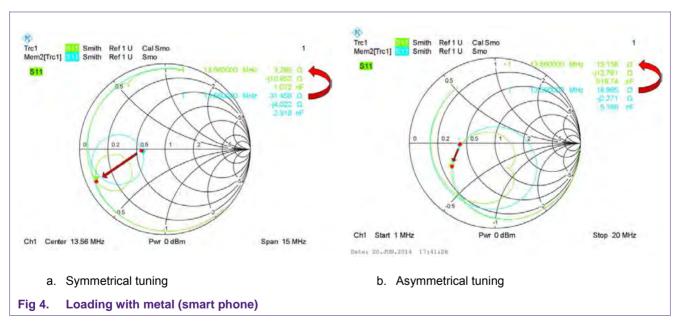

One problem related to the "symmetrical" tuning is the loading and detuning behavior, as shown in Fig 3 and Fig 4. While the impedance in case of the standard tuning increases under detuning and loading conditions, the impedance in case of the "symmetrical" tuning always decreases. This can cause serious problems, especially if the nominal impedance ("target impedance" unloaded) is already at a lower limit, which provides the maximum allowed output power, using an ITVDD close to the maximum limit.

5 of 21

#### How to design an antenna with DPC

Without any specific control of the output power the decreasing impedance increases the driver current and therefore the field strength, which might easily extend the allowed limits, i.e. it might exceed the IC specification for the driver current ITVDD as well as it might exceed the field strength limits of ISO/IEC 14443, NFC or EMVCo.

The PN5180 provides the dynamic power control to compensate the decreasing impedance and reduce the driver current automatically. This allows to use the "symmetrical" tuning with improved transfer function with the PN5180. Therefor this tuning is called "DCP antenna tuning".

How to design an antenna with DPC

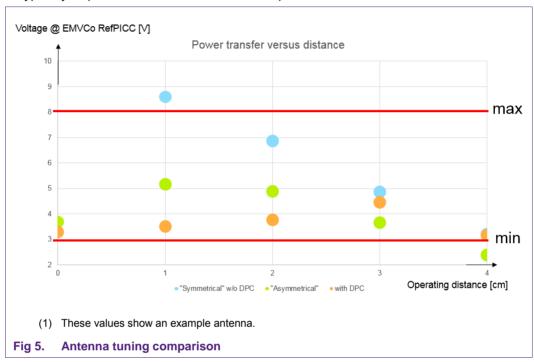

The Fig 5 shows an example of a comparison of three different antenna tunings, using the same antenna coil. All the three antennas are tuned to the same impedance, i.e. the ITVDD under unloaded condition is the same in all cases.

**Note:** The operating distance is measured in the center of the antenna, and the shown limits are the EMVCo power transfer limits including some margin. Such margin is typically required to meet the limit in all test positions.

The "asymmetrical" tuning does not generate enough field strength at 4cm operating distance. This tuning would fail the EMVC tests.

The "symmetrical" tuning without DPC generates enough field strength to meet the requirements at 4cm distance, but fails in closer distance due to the strong coupling. The measurement with 0cm distance was not even executed to protect the NFC Reader IC, since the driver current would exceed the specified limit by far. This tuning would fail the EMVCo tests.

The DPC Antenna tuning ("symmetrical tuning with DPC) combines the advantages of enough field strength at 4cm with the automatic power control to limit the maximum field strength at a close distance. This tuning would pass the EMVCo tests.

## 3. DPC antenna tuning procedure

#### How to design an antenna with DPC

#### 3.1 Difference in the tuning procedure

In principle the antenna tuning procedure for the DPC antenna tuning is not different than the tuning for the standard antennas. All the measurements and the related tools are the same, and all the calculations and simulations are the same.

However, some input parameters differ and some additional tests and adjustment steps must be done to provide a proper functionality.

The EMC filter cut off frequency must be adapted, the EMC filter inductance (L0) must be within certain limits, the Q factor of the antenna coil circuit itself can be higher, the correlation between AGC values and ITVDD values must be guaranteed, and the DPC must be calibrated properly.

### 3.2 DPC Tuning requirements

#### 3.2.1 EMC filter cut off frequency

The EMC cut off frequency as mentioned in section 2.2 must be lower than in the normal antenna tuning:

$$f_{EMC} \approx 14.3...14.7MHz$$

(2)

#### 3.2.2 EMC filter inductance

The inductance of the EMC filter inductor L0 must be:

$$L_0 \ge \frac{L_{AntennaCoil}}{2} \tag{3}$$

Otherwise the correlation between AGC and ITVDD might not be given.

Normally the inductance value of  $L_0$  is chosen to be as low as possible to achieve the best Q factor for the EMC filter. Combining these two requirements the L0 typically is chosen:

$$L_0 \approx \frac{L_{AntennaCoil}}{2} \tag{4}$$

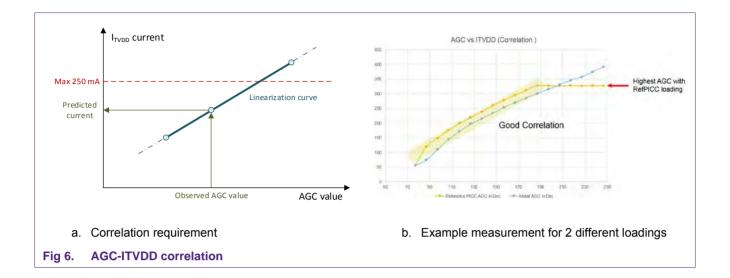

#### 3.2.3 Correlation of AGC and ITVDD

For the proper function of the dynamic power control the AGC values must correlate to the ITVDD values. Normally this is automatically granted, as soon as the requirements in section 3.2.1 and section 3.2.2 are fulfilled.

The Fig 6 illustrates this requirement, and an example measurement for two different loading cases (Reference PICC and metal loading).

Note: The NFC Cockpit (PN5180 graphical user interface) provides a test function, which allows a quick execution of this correlation tests. For details refer to [2].

#### How to design an antenna with DPC

#### 3.2.4 DPC calibration

The last requirement is the proper calibration of the dynamic power control. The details are described in [2]. The NFC Cockpit (PN5180 GUI) provides the functionality to perform this calibration and store the complete set of related settings into the EEPROM.

Note: The P5180 might be damaged, if a DPC tuned antenna is used without a proper DPC calibration and the antenna is loaded and detuned. So it is recommended during the design in phase to connect an external power supply to the TVDD supply of the PN5180, which allows to limit the current to e.g. 250mA, as long as the DPC is disabled or not properly calibrated.

**Note:** The DPC provides TX Shaping features, which help to meet the pulse shape requirements. These TX Shapings can be adjusted to be dynamically set properly even under the different loading cases. The required setup is described in [2].

**Note:** The DPC provides a production trimming feature, which allows to compensate production tolerances between devices. It is recommended to use this feature to trim each produced NFC Reader module or terminal before issuing. This feature and the related trim procedure is described in [2].

#### 3.3 DPC antenna tuning

The DPC antenna tuning itself is done with the same following steps, as described in [1]:

- 1. Measure the antenna coil

- 2. Define target impedance and Q-factor

- 3. Define the EMC filter

- 4. Calculate the matching components

- 5. Simulate the matching

How to design an antenna with DPC

- 6. Assembly and measurement

- 7. Adaptation of simulation

- 8. Correction and assembly

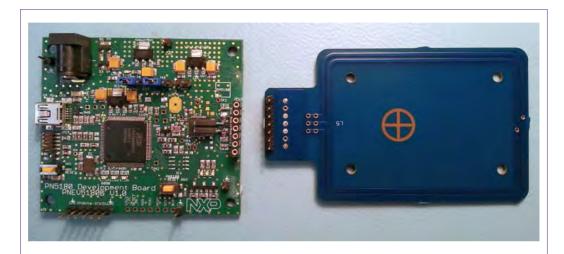

The following description uses the example of an NFC antenna of the size of 45mm x 65mm. The target is to meet the EMVCo limits with this antenna (see Fig 7).

(1) The antenna was made as NFC antenna and has the size of 35mm x 45mm.

Fig 7. DPC Tuning example

#### 3.3.1 Measure the antenna coil

The antenna coil must be designed as described in [1] and be measured. The measurement is required to derive the inductance L, the resistance  $R_{\text{Coil}}$  and the capacitance  $C_{\text{pa}}$  as accurate as possible.

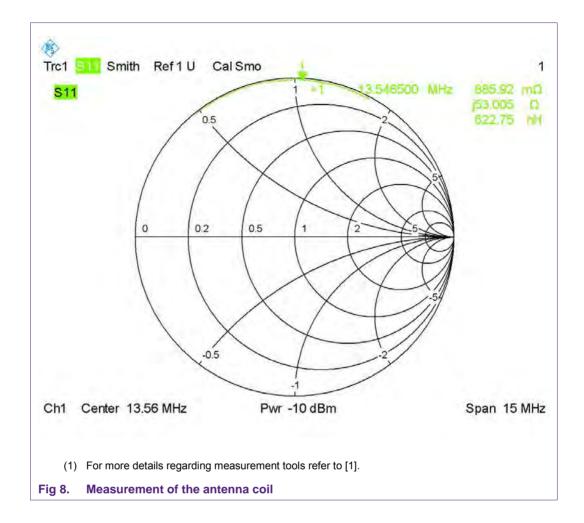

The easiest even though not most accurate way is to use the VNA to measure the impedance  $\underline{Z}$  of the antenna coil at 13.56MHz and to calculate L and R out of it:

$$\underline{Z} = R + j\omega L_{AntennaCoil}$$

(5)

Typically the VNA directly can show the L and R, as shown in Fig 8.

10 of 21

#### How to design an antenna with DPC

In this example the antenna coil is measured with these values:

L = 623nH

R<sub>Coil</sub> ≈ 900mΩ

C<sub>pa</sub> = not measured, can be estimated

The inductance can be measured quite accurate, but the resistance is not very accurate due to the relationship between R and j $\omega$ L. And the capacitance is not measured at all with this simple measurement.

There are several ways to improve the accuracy and even further derive the capacitance, but these simple results are enough to start the tuning procedure. This tuning procedure needs to be done anyway, so there is no real need to spend more effort in measuring the antenna coil parameters more accurate.

#### 3.3.2 Define target impedance and Q-factor

The target impedance must be defined. For the maximum power transfer it should be  $18...20\Omega$  (as indicated in [1]). In such case the driver current ITVDD gets close to the limit of ITVDDmax = 250mA.

#### How to design an antenna with DPC

The impedance target might be different for different applications. An impedance target of Rmatch =  $50...80\Omega$  might be better in battery powered devices, where the current consumption must be minimum, while at the same time the required maximum operating distance can be lower.

Note: The following example targets a proper power transfer for an EMVCo POS design. So the target is  $20\Omega$ , but due to some uncertainties the final impedance is  $26\Omega$ . The current consumption stays far below the maximum limit (≈ 142mA unloaded). Still EMVCo limits can easily be met, since the DPC antenna tuning provides enough margin.

The quality factor Q depends on the overall system requirements and frame conditions. The overall system requires the Q to be in a range, which allows us to meet the timing and pulse shape requirements of the corresponding standard (ISO, NFC or EMV). These requirements are mainly the same, but with some differences:

While ISO allows data rates of up 848 kbit/s, NFC allows the data rates of up to 424 kbit/s. EMV systems are limited to 106 kbit/s. So typically the Q of EMV reader systems can be higher than the Q of ISO or NFC reader systems.

The Q is an indirect value, since the measurement of the Q in the overall antenna system, which includes the antenna driver as well as the contactless card, is complex – and not required. The wave shape and timing measurements, as required according to the standards, are the relevant measurements, and the corresponding Q value is not of any importance.

Here in a first step the Q is chosen for the passive and linear antenna circuit only. So it can be seen as **start value** to calculate the damping resistors  $R_Q$ .

Good starting values as entry for the calculation of the matching calculation are shown in Table 1.

The Q factor for the DPC antenna tuning can be higher than normal due to the improved transfer function and the TX shaping features of the PN5180.

Table 1. Q-factor start value for antenna tuning

These values can be taken as start values for the DPC antenna tuning

| Q  | Condition                                                                                     | Antenna tuning |

|----|-----------------------------------------------------------------------------------------------|----------------|

| 20 | Start value for the matching calculation for typical NFC Reader design.                       | Normal         |

| 25 | Start value for the matching calculation for typical NFC Reader design, limited to 106kbit/s. | Normal         |

| 30 | Nominal value for MIFARE (Classic) communication.                                             | Normal         |

| 30 | Start value for the DPC antenna tuning                                                        | DPC antenna    |

**Note:** The Q factor for the DPC antenna tuning can be higher than normal due to the improved transfer function and the TX shaping features of the PN5180.

Note: The Q of the L0 inductance is a major factor: the higher the better!

**Note:** The final Q must be tuned with the pulse shape measurements, if the antenna shall be fully optimized.

#### How to design an antenna with DPC

Note: It might be helpful to slightly adapt the Q in the given Excel sheet calculation in such a way that the resulting damping resistor RQ is calculated to be within an Eseries of values (i.e.  $2.7\Omega$  or  $3.3\Omega$ , but not  $2.845\Omega$ ). In such case the following calculation is more accurate, i.e. the calculation result gets closer to the measured result.

#### 3.3.3 Define the EMC filter

The EMC filter is a second order low pass filter as shown in Fig 1, and contains an inductor (L0) and a capacitor (C0). The cut off frequency defines the overall detuning behavior as well as the transfer function of the antenna circuit.

The inductor L0 needs to be capable to drive the full power into the antenna without going into saturation. The Q-factor of this inductor is a key parameter and should be as high as possible.

Typically the inductance is in the range of

$L_0 = 330nH...560nH$  (see section 3.2.2!)

For the example we stay with a value of

$L0 = 470nH > L_{AntennaCoil} / 2$

The cut off frequency typically must be in the range as given in section 3.2.1:

For the example we start with a value of

$f_{EMC} = 14.6MHz$

Note: For the example antenna the RF performance might be even better with an EMC inductance of e.g. 390nH or 330nH, which would still be possible to achieve a proper correlation between AGC and ITVDD.

#### 3.3.4 Calculate the matching components

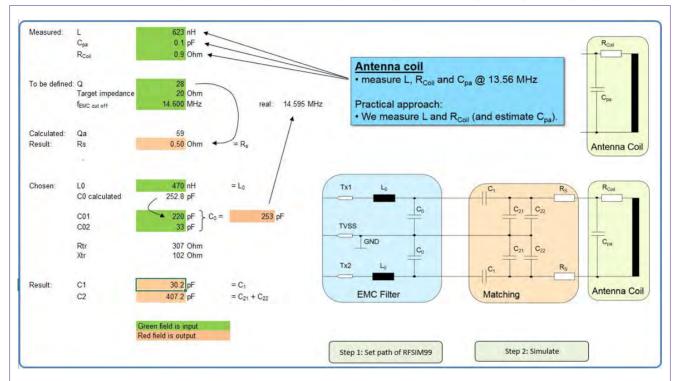

The next step is to calculate the values of the matching circuit. The input for the Excelsheet as shown in Fig 9 needs to be:

#### "Measured" values:

$L_{AntennaCoil} = L = 623nH$  (measured antenna coil inductance)

Ca = Cpa = 0.1pF (estimated parallel capacitance of the antenna coil)

Ra = RCoil =  $900m\Omega$  (measured antenna coil resistance)

#### **Preset values:**

Q = 28 (defined Q-factor, see section 3.3.2)

Rmatch =  $20\Omega$  (defined target impedance, see section 3.3.2)

L0 = L0A = L0B = 470nH (EMC filter inductance, see section 3.2.2 and 3.3.3)

#### How to design an antenna with DPC

C0 = C0A = C0B = 220pF + 33pF (EMC filter capacitance, see section 3.2.1)

#### Calculated Values (see Fig 9):

$Rq = RQ = R_S = 0.5\Omega$

C1 = (C1A + C1B) = (C1C + C1D) = 30.2pF -> 33pF (chosen)

C2 = (C2A + C2B) = (C2C + C2D) = 407.2pF -> 330pF + 82pF + 1.5pF (chosen)

(1) Excelsheet available on www.nxp.com

Fig 9. Calculation of the matching values

Due to the DPC antenna tuning the EMC filter uses a cut off frequency, which is quite close to the operating frequency (13.56MHz). Therefore it might be dangerous to disconnect the antenna after the EMC filter (which is the typical connection, if there is any), since the open at the connector is transformed into something very close to a short. Disconnecting the antenna after the EMC filter might destroy the NFC reader IC. The alternative might be to split the EMC filter capacitance (C0) into two capacitors and assemble only one part of the EMC filter capacitance (C0a) on the main board, and another part (C0b) on the antenna board. In such case the EMC filter cut off frequency automatically shifts up a few MHz, as soon as the antenna is disconnected, and no short occurs. In case of the used demo boards the C0 therefore is split into the 2 parts of 220pF assembled on the main board and 33pF assembled on the antenna board.

#### How to design an antenna with DPC

#### 3.3.5 Simulate the matching

The measurement of the antenna coil itself typically is not very accurate. Therefore a (fine) tuning of the antenna normally is required, which might become easier in combination together with a simulation.

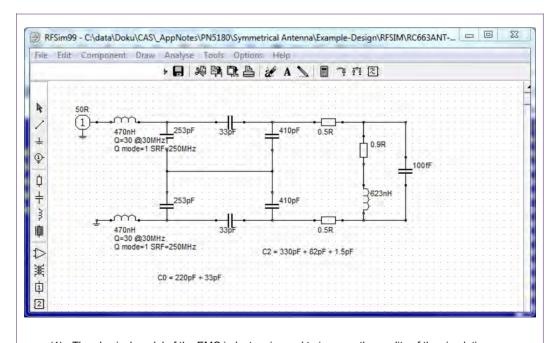

A simple matching simulation tool like e.g. RFSIM99 (refer to [3]) can be used to support the antenna tuning.

The excel sheet supports the direct simulation: the path for the simulation must be set by pressing the green button <Step 1: Set Path of RFSIM99>. Afterwards pressing the green button <Step 2: Simulate> starts the simulation with the given and calculated values.

The final schematic using the example antenna is shown in Fig 10. In this example the antenna coil measurement was accurate enough. The capacitors have been chosen as indicated.

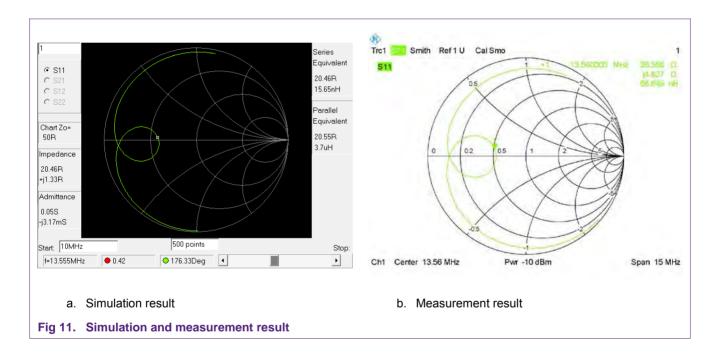

The simulation result as well as the measurement result is shown in Fig 11.

The standard simulation is done with ideal components, which is accurate enough for the capacitors. However, the antenna coil as well as the EMC filter inductors L0 are typically far from being ideal. RFSIM99 allows to use physical models, which requires to enter e.g. the self-resonant frequency and the Q-factor measured at a certain frequency. With these models the simulation already becomes more accurate.

With these values the first assembly can be done, even though the reality still might be slightly different due to inaccurate values for the antenna coil itself and due to the slightly different component values.

(1) The physical model of the EMC inductors is used to improve the quality of the simulation.

Fig 10. Simulation circuit with RFSIM99

## How to design an antenna with DPC

#### 3.3.6 Assembly and measurement

The measurement result is shown in Fig 11b.

Sometimes the measurement result is slightly different than the simulation result, since the accuracy of the original antenna coil measurement is limited, and therefore the antenna coil parameters in the simulation typically do not 100%ly reflect the real parameters. This must be corrected – and then re-tuned in the next steps.

However, in this example the measurement is already close enough - except that the overall impedance is higher than expected. The further measurements will show that with  $26\Omega$  (reality) instead of  $20\Omega$  (original target) the ITVDD is lower than originally targeted, but the EMVCo limits can still be met.

So for our example no re-tuning is required, therefor in our example the next two steps can be skipped.

#### 3.3.7 Impedance adaptation in simulation

The easiest and fastest way to (fine) tune the antenna is to first of all adapt the simulation in such a way that it shows the same result like the reality. The parameters of the antenna coil are the parameters to be changed, since these parameters are not measured (or estimated) correctly.

So with the values of L, Cpa, and RCoil the simulation is tuned, until the simulation result matches the real measurement result (even though both look "detuned").

#### How to design an antenna with DPC

#### 3.3.8 Impedance correction and assembly

Now in the last tuning step the impedance must be corrected with the values of C1 and C2 (first) in the simulation, until the target impedance is matched. Then the final assembly should show the same result as the simulation.

#### 4. References

- [1] AN11740 PN5180 standard antenna design, www.nxp.com

- [2] AN11742 PN5180 Dynamic Power Control, www.nxp.com

- [3] Simulation tool RFSIM99, www.nxp.com/redirect/electroschematics.com/835/rfsim99-download/

17 of 21

#### How to design an antenna with DPC

## 5. Legal information

#### 5.1 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

#### 5.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

**Evaluation products** — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer.

In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages.

Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

#### 5.3 Licenses

#### Purchase of NXP ICs with NFC technology

Purchase of an NXP Semiconductors IC that complies with one of the Near Field Communication (NFC) standards ISO/IEC 18092 and ISO/IEC 21481 does not convey an implied license under any patent right infringed by implementation of any of those standards. Purchase of NXP Semiconductors IC does not include a license to any NXP patent (or other IP right) covering combinations of those products with other products, whether hardware or software.

#### 5.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are property of their respective owners.

MIFARE — is a trademark of NXP Semiconductors N.V.

## How to design an antenna with DPC

## 6. List of figures

| Fig 1.  | Antenna tuning circuit              | 4  |

|---------|-------------------------------------|----|

| Fig 2.  | Symmetrical and asymmetrical tuning | 5  |

| Fig 3.  | Loading with Reference PICC         | 6  |

| Fig 4.  | Loading with metal (smart phone)    | 6  |

| Fig 5.  | Antenna tuning comparison           | 7  |

| Fig 6.  | AGC-ITVDD correlation               | 9  |

| Fig 7.  | DPC Tuning example                  | 10 |

| Fig 8.  | Measurement of the antenna coil     | 11 |

| Fig 9.  | Calculation of the matching values  | 14 |

| Fig 10. | Simulation circuit with RFSIM99     | 15 |

| Fia 11  | Simulation and measurement result   | 16 |

How to design an antenna with DPC

## 7. List of tables

Table 1. Q-factor start value for antenna tuning......12

## How to design an antenna with DPC

## 8. Contents

| 1.    | Introduction                               | 3    |

|-------|--------------------------------------------|------|

| 2.    | DPC antenna tuning principle and advantage | es 3 |

| 2.1   | Principle                                  |      |

| 2.2   | "Symmetrical" versus "asymmetrical" tuning | 4    |

| 3.    | DPC antenna tuning procedure               | 7    |

| 3.1   | Difference in the tuning procedure         | 8    |

| 3.2   | DPC Tuning requirements                    | 8    |

| 3.2.1 | EMC filter cut off frequency               | 8    |

| 3.2.2 | EMC filter inductance                      | 8    |

| 3.2.3 | Correlation of AGC and ITVDD               | 8    |

| 3.2.4 | DPC calibration                            |      |

| 3.3   | DPC antenna tuning                         | 9    |

| 3.3.1 | Measure the antenna coil                   | 10   |

| 3.3.2 | Define target impedance and Q-factor       | 11   |

| 3.3.3 | Define the EMC filter                      |      |

| 3.3.4 | Calculate the matching components          | 13   |

| 3.3.5 | Simulate the matching                      |      |

| 3.3.6 | Assembly and measurement                   | 16   |

| 3.3.7 | Impedance adaptation in simulation         | 16   |

| 3.3.8 | Impedance correction and assembly          | 17   |

| 4.    | References                                 | 17   |

| 5.    | Legal information                          | 18   |

| 5.1   | Definitions                                | 18   |

| 5.2   | Disclaimers                                | 18   |

| 5.3   | Licenses                                   | 18   |

| 5.4   | Trademarks                                 | 18   |

| 6.    | List of figures                            | 19   |

| 7.    | List of tables                             |      |

| 0     | Contents                                   | 21   |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in the section 'Legal information'.

© NXP Semiconductors N.V. 2015.

All rights reserved.

For more information, visit: http://www.nxp.com

Date of release: 24 November 2015