**AN11557** BGU8052[BTS1001M] 1900MHz LNA improved IRL Rev. 2 — 28 April 2017 1

**1900 MHz LNA**

#### **Document information**

| Info                | Content                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords            | BGU8052 [BTS1001M], 1900 MHz, LNA, BTS                                                                                                                                                                                                                                                                                                                                                                                            |

| Abstract            | This application note provides circuit schematic, layout, BOM and typical evaluation board performance of a 1900 MHz LNA with the use of the BGU8052. The design has been tuned for better input return loss. For the 1700 to 2700 MHz wireless communication bands. Covering LTE FDD bands 1-4,7,9,10,15,16,23-25,30. The performance is given at 3.3 and 5 V supply supporting small cell respectively large cell applications. |

| Ordering info       | Demonstrator boards OM7893,<br>12NC: 9340 690 55598                                                                                                                                                                                                                                                                                                                                                                               |

| Contact information | For more information, please visit: <u>http://www.nxp.com</u>                                                                                                                                                                                                                                                                                                                                                                     |

#### **Revision history**

| Rev | Date              | Description                                         |

|-----|-------------------|-----------------------------------------------------|

| 1   | 03 September 2015 | First publication                                   |

| 2   | 28 April 2017     | Update of the circuit topology to reduce IP3 spread |

## **Contact information**

For more information, please visit: <u>http://www.nxp.com</u>

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

AN11557 Application note All information provided in this document is subject to legal disclaimers.

Rev. 2 — 28 April 2017

© NXP B.V. 2017. All rights reserved.

2 of 21

#### 1. Introduction

NXPs semiconductors BGU805x series is a family of integrated low noise amplifiers for the 300 MHz to 6000 MHz range. The series consists of the:

- BGU8051 recommended for 300 MHz 1500 MHz

- BGU8052 recommended for 1500 MHz 2700 MHz

- BGU8053 recommended for 2500 MHz 6000 MHz

The BGU805X series is a low noise high linearity amplifier family intended for wireless infrastructure applications like BTS, RRH, small cells, but can also be used in other general low noise applications, e.g. active antennas for automotive.

Being manufactured in NXPs high performance QUBiC RF Gen 8 SiGe:C technology, the BGU805X combines high gain, ultra-low noise and high linearity with the process stability and ruggedness which are the characteristics of SiGe:C technology.

BGU805X series comes in the industry standard 2 x 2 x 0.75 mm 8 terminal plastic thin small outline package HVSON8 (SOT1327). The LNA is ESD protected on all terminals.

The 3 types can all use the same PCB layout topology. This enables design in simplicity using one PCB layout for designing LNA's covering the frequency range from 300MHz to 6000 MHz with one single PCB layout design.

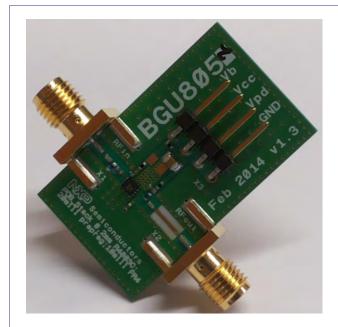

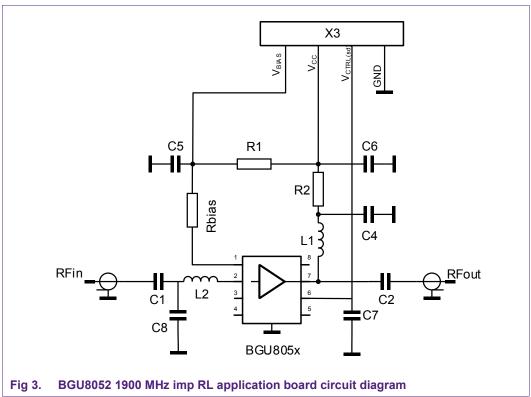

In application note <u>AN11416</u> the use of the BGU8052 is describes as a wideband LNA for the 1500 to 2700 MHz range with compromised input return loss. In this application note a design procedure is described to improve the input return loss for better filter integration, without NF degradation. Design can be suited for the wireless communication bands from 1700 to 2700 MHz. In Fig 1, the evaluation board described in this application note is shown.

a. Front side

- Fig 1. BGU8052 1900 MHz evaluation board

- b. Back side

## 2. Product description

The BGU8052 is a fully integrated low noise amplifier with integrated bias circuit. The MMIC is internally matched to 50  $\Omega$ . The BGU8052 also features an integrated shutdown circuit to enable fast turn on/off settling time, enabling switched (time domain duplexing TDD) applications. The device bias current can be set by the value of an external bias resistor R<sub>BIAS</sub>, which connects the supply voltage to the V<sub>BIAS</sub> pin, or by an external control voltage applied directly to V<sub>BIAS</sub> pin 1. This adjustable bias current gives flexibility in biasing the device for the optimum performance on NF or linearity. This feature can be useful in case more than one BGU8052 are cascaded. This bias resistor value changes the bias current directly which can be used to trade of linearity for power saving in battery operated applications.

The BGU8052 key features and benefits at 1900MHz are;

- Low noise performance: NF = 0.57 dB

- High linearity performance: IP3<sub>0</sub> = 36.6 dBm

- High output power at 1dB gain compression PL1dB = 18.5 dBm

- High input return loss RLin = 21 dB

- High out return loss RL<sub>out</sub> = 17dB

- Unconditionally stable up to 20 GHz

- Max RF input power of +20 dBm

- ESD protection on all pins

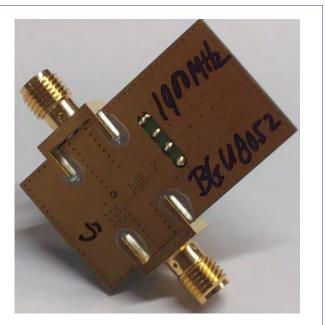

In Fig 2 the pin out of the BGU8052 is given, the n.c. and i.c pin are recommended to connect to ground, which is the case on the evaluation boards.

#### 3. 1900 MHz LNA improved input return loss evaluation board.

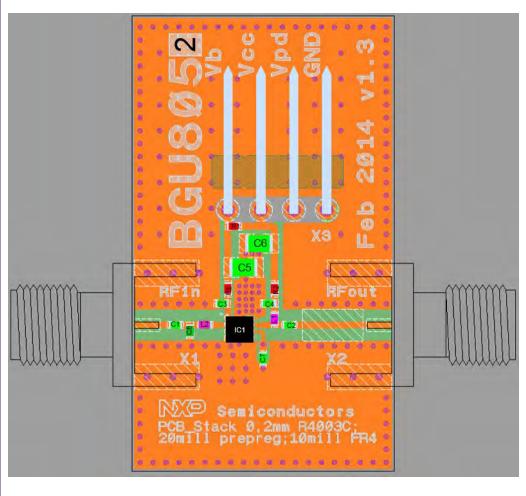

The 1900MHz improved return-loss evaluation board simplifies the RF evaluation of the BGU8052. The EVB enables testing the device RF performance and requires no additional support circuitry. The EVB is fabricated on a  $35 \times 20 \times 1000$  mm 4 layer PCB that uses 0.2 mm (8 mill) R4003C for the RF performance. The board is fully assembled with

the BGU8052, including the external components. The board is supplied with two SMA connectors to connect input and output to the RF test equipment. The EVB is also enabled with the possibility to evaluate the BGU8052 at different bias currents.

#### 3.1 Application circuit

The BGU8052 has been characterized for S-parameter and Noise-parameters at different bias settings. This data can be downloaded from NXPs website as a zip file. The S2P files you can find in this zip file have been used as a small signal model to design this 1900MHz LNA. The low pas matching structure that is created by means of L2 and C8, improves the input return loss for better filter integration.

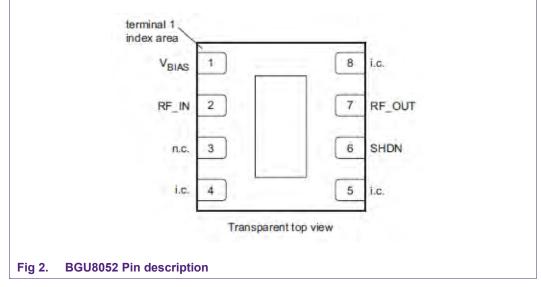

The application board circuit diagram that is implemented on the EVB is shown in Fig 3

As already indicated the bias current of the BGU8052 can be set by the value R<sub>BIAS</sub>. The evaluation boards are supplied with a 5.1 k $\Omega$  bias resistor (I<sub>CC</sub> = 48 mA +/-5 mA @ V<sub>CC</sub>=5V). If however it is required to evaluate the BGU8052 at different bias currents, resistor R1 which is 0  $\Omega$  can be removed and an external control voltage can be applied to V<sub>BIAS</sub> (V<sub>b</sub> pin) on the bias header X3, see Fig 3.

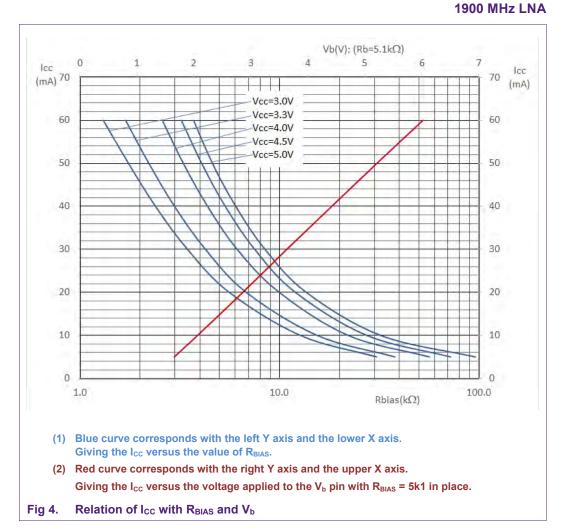

By applying this separate bias voltage on the V<sub>BIAS</sub> pin of the bias header X3, the I<sub>CC</sub> current can be swept without changing R<sub>BIAS</sub>. With bias voltage window from 1.5 to 6 V on V<sub>BIAS</sub> while keeping the V<sub>CC</sub> pin on 5 V, I<sub>CC</sub> can be varied from 5-60 mA. In Fig 4 the relation between I<sub>CC</sub> and R<sub>BIAS</sub> at V<sub>CC</sub> = 5 V as well as the relation between I<sub>CC</sub> and V<sub>BIAS</sub> with R<sub>BIAS</sub> = 5k1 is shown. In Fig 4 you can also find the bias resistor values when applying the BGU8052 at lower supply voltages. Which indicates the BGU805x series can also be biased with lower voltage e.g. 3.3V which makes it excellent suitable for small cells. In paragraph 4.1 typical performance of the LNA @ 3.3V 48mA is also included.

# AN11557

#### 3.2 PCB Layout information

- A good PCB layout is an essential part of an RF circuit design. The LNA evaluation board can serve as a guideline for laying out a board using the BGU8052.

- The evaluation board uses micro strip coplanar ground structures for controlled impedance lines for the high frequency input and output lines.

- V<sub>CC</sub> is decoupled by C4 and C6 decoupling capacitors, C4 should be located as close as possible to the device, to avoid AC leakage via the bias lines. For long bias lines it may be necessary to add decoupling capacitors along the line further away from the device.

- The self-resonance frequency of inductor L1 should be chosen above frequency band of interest for good choking. In this case the Murata LQW15 series has been used.

- Inductor L2 and capacitor C8 are creating the low pass matching structure and are in that sense critical, to the input return loss at the frequency of interest.

- C1 and C2 are DC blocking capacitors, C1 needs to be in the range of 100nF to keep the provided input source impedance for low frequencies low impedance. [1]

- C5 is not mounted on the evaluation boards, but can be used as additional V<sub>CC</sub> decoupling, but is not critical to the RF performance.

All information provided in this document is subject to legal disclaimers.

AN11557

- C7 is used to decouple the shutdown pin

- R2 increases the low frequency stability

- Proper grounding of the GND pins is also essential for good RF performance. Either connect the GND pins directly to the ground plane or through vias, or do both, which is recommended. The layout and component placement of the BGU8052 evaluation board is given in Fig 5

Fig 5. BGU8052 1900MHz evaluation board component placement

#### 3.2.1 PCB stack and recommended footprint.

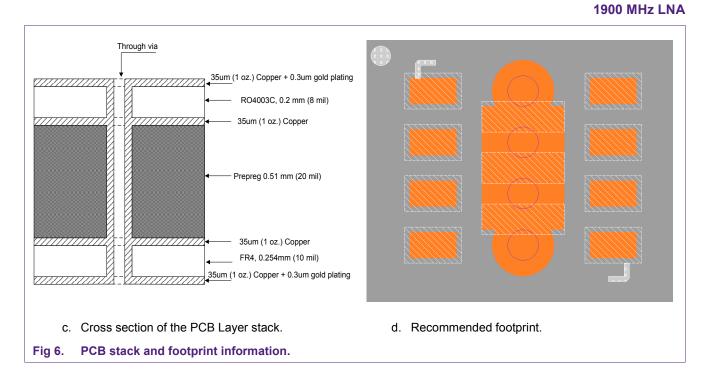

The PCB material used to implement the LNA is a 0.2 mm (8 mil) RO4003C low loss printed circuit board which is merged to a 0.51 mm (20 mil) prepreg and a 0.254 mm (10 mil) FR4 layer for mechanical stiffness. See Fig 6a

The official drawing of the recommended footprint can be found on the PIP page of the BGU8052. If micro strip coplanar PCB technology is used it is recommended to use at least 4 ground-via holes of 300 um, this is also used on the EVBs as shown in Fig 6b.

#### **NXP Semiconductors**

#### 3.3 Bill of materials

Table 1 gives the bill of materials as is used on the EVB.

#### Table 1. BOM

| Designator | Description | Footprint | Value | Supplier Name/type                          | Comment/function        |

|------------|-------------|-----------|-------|---------------------------------------------|-------------------------|

| IC1        | BGU8052     |           |       |                                             |                         |

| PCB        | 20x35x1mm   |           |       | KOVO                                        | RO4003C PCB v 1.3       |

| C1         | Capacitor   | 0402      | 100nF | Various                                     | DC block                |

| C2         | Capacitor   | 0402      | 100pF | Various                                     | DC block                |

| C4         | Capacitor   | 0402      | 1nF   | Various                                     | RF decoupling           |

| C5         | Capacitor   | 0806      | 4.7uF | Various                                     | Optional                |

| C6         | Capacitor   | 0806      | 4.7uF | Various                                     | LF Decoupling           |

| C7         | Capacitor   | 0402      | 10pF  | Various                                     | Decoupling              |

| C8         | Capacitor   | 0402      | 0.9pF | Murata GJM15                                | Input match             |

| L1         | Inductor    | 0402      | 15nH  | Murata LQW15                                | Bias choke/Output match |

| L2         | Inductor    | 0402      | 1.8nH | Murata LQP15                                | Input match             |

| R1         | Resistor    | 0402      | 0Ohm  | Various                                     |                         |

| R2         | Resistor    | 0402      | 10Ohm | Various                                     | stability               |

| Rbias      | Resistor    | 0402      | 5k1   | Various                                     | Bias setting            |

| X1,X2      | SMA RF      |           |       | Johnson, End launch                         | RF connections          |

|            | connector   |           |       | SMA 142-0701-841                            |                         |

| X3         | DC header   |           |       | Molex, PCB header, right angle, 1 row 4 way | DC connections          |

AN11557

## 4. Measurement results

#### 4.1 Typical board performance

The values given in <u>Table 2</u> are typical values of >25 boards measured.

Table 2.

Typical board performance using the BOM given in Table 1

| Symbol               | Parameter                             | Conditions                                           |                    | Min          | Тур          | Max          | Тур          | Unit |

|----------------------|---------------------------------------|------------------------------------------------------|--------------------|--------------|--------------|--------------|--------------|------|

| Vcc                  | Supply voltage                        |                                                      |                    | 5            | 5            | 5            | 3.3          | V    |

| Icc                  | Supply current                        |                                                      |                    | 46.9         | 49.1         | 51.6         | 49.7         | mA   |

| Gass                 | Associated gain                       |                                                      | 1500MHz<br>1900MHz | 20.3<br>18.2 | 20.4<br>18.3 | 20.6<br>18.5 | 20.4<br>19.3 | dB   |

| NF                   | Noise figure                          | Error! Reference source not<br>found.                | 1500MHz<br>1900MHz | 0.48<br>0.55 | 0.52<br>0.57 | 0.56<br>0.61 | 0.58<br>0.63 | dB   |

| P <sub>L((1dB)</sub> | Output power at 1dB gain compression  |                                                      | 1500MHz<br>1900MHz | 17.4<br>18.0 | 17.9<br>18.5 | 18.3<br>18.9 | 14.4<br>15.0 | dBm  |

| IP3o                 | Output third-order<br>intercept point | 2-tone; tone spacing = 1MHz;<br>Pi = -15dBm per tone | 1500MHz<br>1900MHz | 36.2<br>36.2 | 36.5<br>36.6 | 36.8<br>37.0 | 34.7<br>34.7 | dBm  |

| RLin                 | Input return loss                     |                                                      | 1500MHz<br>1900MHz | 14.7<br>18.7 | 15.4<br>21.4 | 16.0<br>22.8 | 16.0<br>22.0 | dB   |

| RLout                | Output return loss                    |                                                      | 1500MHz<br>1900MHz | 18.3<br>15.1 | 20.5<br>17.2 | 21.5<br>18.2 | 20.9<br>17.6 | dB   |

| ISL                  | Isolation                             |                                                      | 1500MHz<br>1900MHz | 25.2<br>23.6 | 25.3<br>23.7 | 25.5<br>23.9 | 25.3<br>23.7 | dB   |

[1] Board losses have not been de-embedded.

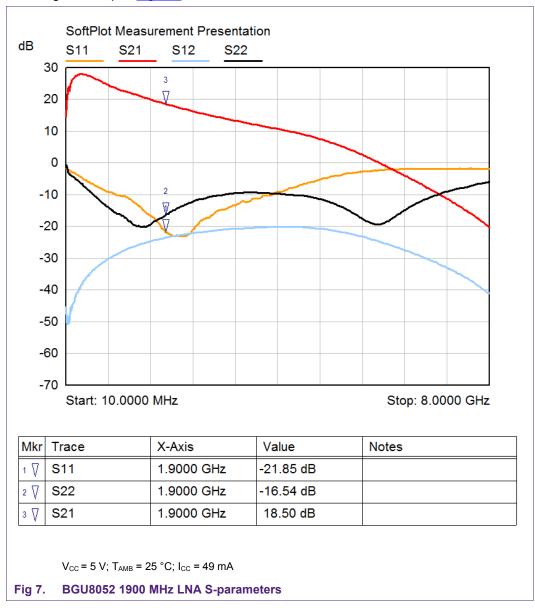

#### 4.2 S\_Parameters

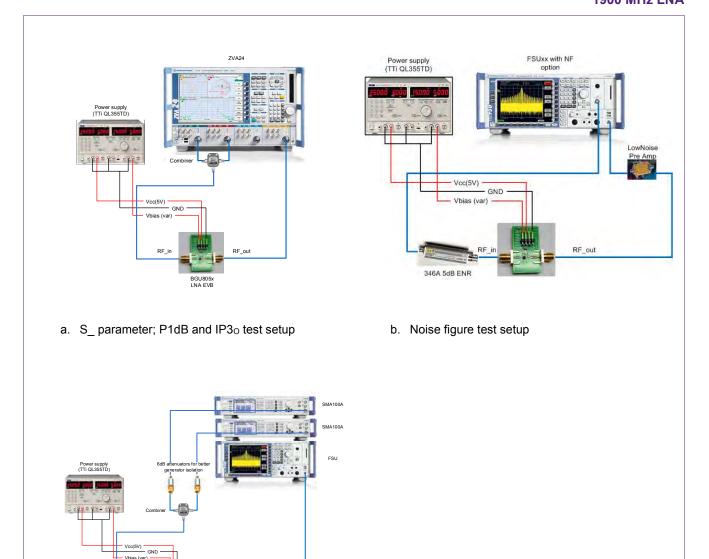

The measured S-parameters are given in Fig 7. For the measurements, a typical BGU8052 1900 MHz EVB is used. All the S-parameter measurements have been carried out using the setup in Fig 12a

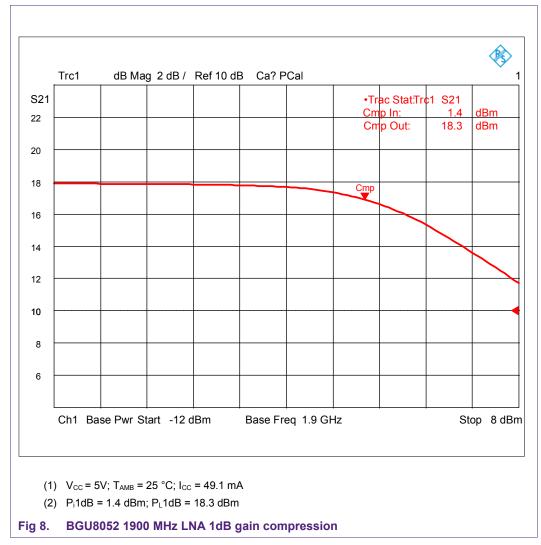

#### 4.3 1dB Gain compression point.

The measured Gain versus input power is given in <u>Fig 8</u> for the measurements, a typical BGU8052 1900 MHz EVB is used. All the P1dB measurements have been carried out using the setup in <u>Fig 12a</u>.

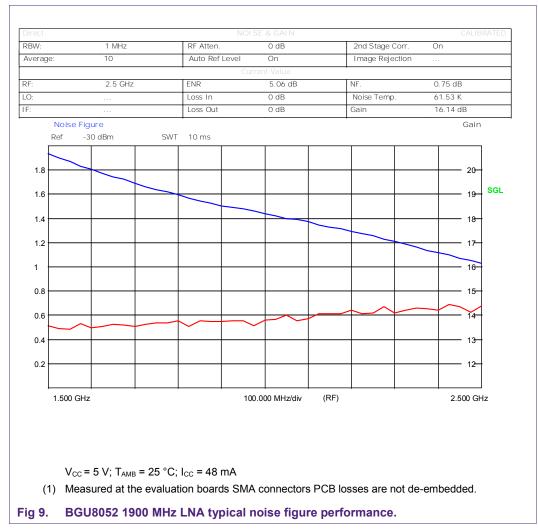

#### 4.4 Noise figure

The measured noise figure are given in  $\underline{Fig 9}$ . For the measurements, a typical BGU8052 1900MHz EVB is used. The noise figure measurement have been carried out using the setup in  $\underline{Fig 12b}$

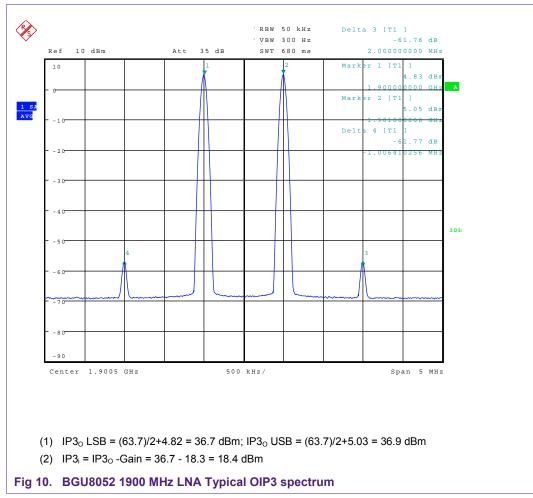

#### 4.5 3<sup>rd</sup> order intercept point, output referred

The evaluation board provided in the customer evaluation kit is automatically measured on linearity using the set-up shown in Fig 12a. Alternatively the setup given in Fig 12c can be used, which is done for the spectrum plot in Fig 10. For the measurements, a typical BGU8052 1900 MHz EVB is used.

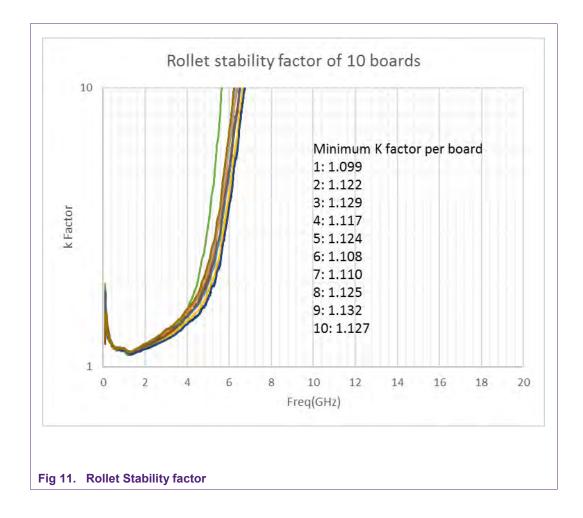

#### 4.6 Stability Factor

Due to the low pass shape of the input matching circuit the low frequency gain becomes high. This might introduce potential instability issues. Proper selection of the output bias choke together with the 10 Ohm resistance R1 avoids this. **Error! Reference source not found.** shows the rollet stability factor plots of 10 EVBs with the improved input return loss BOM.

#### 5. Measurement methods and setups.

#### 5.1 Required Measurement Equipment

In order to measure the evaluation board, the following is necessary:

- $\checkmark$  2 (channel) DC Power Supply up to 100 mA at 5 V, to set Vcc and eventual Vbias.

- ✓Two RF signal generators capable of generating RF signals up to 2 GHz

- ✓An RF spectrum analyzer that covers at least the operating frequencies and a few of the harmonics. Up to 6 GHz should be sufficient.

- ✓A network analyzer for measuring gain, return loss and reverse isolation

- ✓Noise figure analyser and noise source

- ✓ Proper RF cables with male SMA connectors.

#### 5.2 Connection and setup

The typical values shown in this report have been measured on the fully automated test setups shown in <u>Fig 12.</u> Please follow the steps below for a step-by-step guide to operate the LNA evaluation board and testing the device functions.

- 1. Connect the DC power supply to the  $V_{\text{CC}}$  and GND terminals. Set the power supply to 5V

- 2. Connect the RF signal generator and the spectrum analyzer to the RF input and the RF output of the evaluation board, respectively. Do not turn on the RF output of the signal generator yet, set it to approximately -30 dBm output power at the center frequency of the wanted frequency band and set the spectrum analyzer at the same center frequency and a reference level of 0 dBm.

- 3. Turn on the DC power supply and it should read approximately 48 mA.

- 4. Enable the RF output of the generator: The spectrum analyzer displays a tone around -11.5 dBm.

- Instead of using a signal generator and spectrum analyzer one can also use a network analyzer in order to measure gain as well as in- and output return loss and P1dB (see Fig 12a)

- 6. For noise figure evaluation, either a noise figure analyzer or a spectrum analyzer with noise option can be used. The use of a 5 dB noise source, like the Agilent 364B, is recommended. When measuring the noise figure of the evaluation board, any kind of adaptors, cables etc. between the noise source and the evaluation board should be minimized, since this affects the noise figure (see Fig 12b).

# AN11557 1900 MHz LNA

c. Third order intercept point test setup

Fig 12. Characterization measurements setups.

#### 5.3 Noise figure measurement setup

In Fig 12b the noise figure measurement set-up is shown, this is intended as a guide only, substitutions can be made. For sub 1 dB noise figure levels like the BGU8052 has it is recommended to perform the noise-measurements in a Faraday's cage or at least put the DUT in a shielded environment. This is recommended to avoid any interference of cellular frequencies that are in the same frequency range. A spectrum analyzer with noise option. A 5dB ENR noise source was used. To achieve the lowest possible setupnoise figure an external pre-amplifier is also recommended. The Noise figure value in Fig 9 is the value measured at the evaluation board SMA connectors. Correcting for the connector and PCB loss will end up in 0.1dB lower noise figure.

#### 5.4 Third order intercept

In [1] the effect on linearity of SiGe BiCMOS BJTs and the advantage of using low source impedances at the low frequencies of the 2<sup>nd</sup> order mixing terms is described. To make the application unsensitive to IP3 spread (magnification, cancelation of the IM3 components) the source impedance seen by the input of the BGU8052 needs to be low-impedance. This is achieved with the C8, L2 and C1, and give the best linearity performance with the lowest IP3 spread. Small drawback is that the circuit as presented is not fast enough to be applied in TDD platforms. When measuring the high OIP3 values it is essential check the capabilities of the used measurement equipment. Be aware that the measurement set-up itself is not generating dominating IM3 levels. Advised is to do a THRU measurement without a DUT first.

#### 6. References

Vladimir Aparin, Lawrence E. Larson, "Linearization of monolithic LNAs Using Low-Frequency Low-Impedance Input Termination". IEEE 0-7 803-8 108-4/03 ©2003

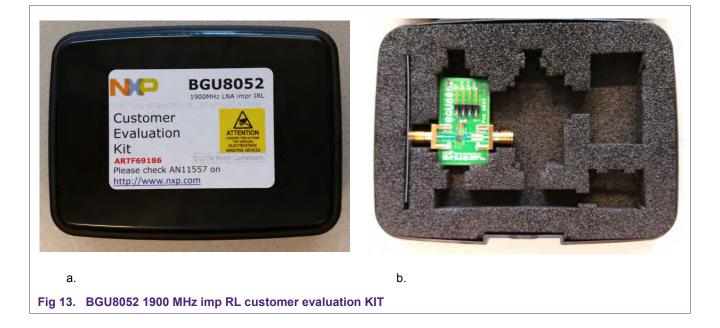

#### 7. Customer Evaluation Kit

In the customer evaluation kit you will find;

- One 1900MHz improved return loss EVB

- 10 loose samples.

# 8. Legal information

#### 8.1 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

#### 8.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Evaluation products** — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer.

In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages.

Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

#### 8.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are property of their respective owners.

# 9. List of figures

| Fig 1.  | BGU8052 1900 MHz evaluation board3                               |

|---------|------------------------------------------------------------------|

| Fig 2.  | BGU8052 Pin description4                                         |

| Fig 3.  | BGU8052 1900 MHz imp RL application board                        |

|         | circuit diagram5                                                 |

| Fig 4.  | Relation of $I_{CC}$ with $R_{\text{BIAS}}$ and $V_{\text{b}}$ 6 |

| Fig 5.  | BGU8052 1900MHz evaluation board                                 |

|         | component placement7                                             |

| Fig 6.  | PCB stack and footprint information8                             |

| Fig 7.  | BGU8052 1900 MHz LNA S-parameters 10                             |

| Fig 8.  | BGU8052 1900 MHz LNA 1dB gain                                    |

|         | compression11                                                    |

| Fig 9.  | BGU8052 1900 MHz LNA typical noise figure                        |

|         | performance12                                                    |

| Fig 10. | BGU8052 1900 MHz LNA Typical OIP3                                |

|         | spectrum13                                                       |

| Fig 11. | Rollet Stability factor14                                        |

| Fig 12. | Characterization measurements setups16                           |

| Fig 13. | BGU8052 1900 MHz imp RL customer                                 |

| -       | evaluation KIT                                                   |

**Application note**

# 10. List of tables

| Table 1. | BOM8                                          |

|----------|-----------------------------------------------|

| Table 2. | Typical board performance using the BOM given |

|          | in Table 19                                   |

**Application note**

## 11. Contents

| 1.    | Introduction                                           | 3  |

|-------|--------------------------------------------------------|----|

| 2.    | Product description                                    | 4  |

| 3.    | 1900 MHz LNA improved input return loss                |    |

|       | evaluation board                                       |    |

| 3.1   | Application circuit                                    |    |

| 3.2   | PCB Layout information                                 |    |

| 3.2.1 | PCB stack and recommended footprint                    |    |

| 3.3   | Bill of materials                                      |    |

| 4.    | Measurement results                                    |    |

| 4.1   | Typical board performance                              |    |

| 4.2   | S_Parameters                                           |    |

| 4.3   | 1dB Gain compression point.                            |    |

| 4.4   | Noise figure                                           |    |

| 4.5   | 3 <sup>rd</sup> order intercept point, output referred |    |

| 4.6   | Stability Factor                                       |    |

| 5.    | Measurement methods and setups                         |    |

| 5.1   | Required Measurement Equipment                         |    |

| 5.2   | Connection and setup                                   |    |

| 5.3   | Noise figure measurement setup                         |    |

| 5.4   | Third order intercept                                  |    |

| 6.    | References                                             |    |

| 7.    | Customer Evaluation Kit                                |    |

| 8.    | Legal information                                      |    |

| 8.1   | Definitions                                            | 18 |

| 8.2   | Disclaimers                                            |    |

| 8.3   | Trademarks                                             | -  |

| 9.    | List of figures                                        | 19 |

| 10.   | List of tables                                         | 20 |

| 11.   | Contents                                               | 21 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in the section 'Legal information'.

#### © NXP B.V. 2017.

#### All rights reserved.

For more information, visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

> Date of release: 28 April 2017 Document identifier: AN11557