# AN10861 GreenChip III TEA1752 integrated PFC and flyback controller Rev. 01 — 16 July 2010 Application note

#### **Document information**

| Info     | Content                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords | GreenChip III, TEA1752, PFC, flyback, high efficiency, adaptor, notebook, PC power                                                                                                                                                                                                                                                                                                                                     |

| Abstract | The TEA1752 is a member of the new generation of PFC and flyback<br>combination controller ICs, used for efficient switched mode power<br>supplies. It has a high level of integration which allows the design of a<br>cost-effective power supply with a minimum number of external<br>components. The TEA1752 is fabricated in a Silicon On Insulator (SOI)<br>process, enabling it to operate a wide voltage range. |

**Revision history**

| Rev | Date     | Description |

|-----|----------|-------------|

| 01  | 20100716 | First issue |

#### **Contact information**

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

All information provided in this document is subject to legal disclaimers.

Application note

#### 1. Introduction

The TEA1752 is a combination controller with a PFC and flyback controller integrated into an SO-16 package. Both controllers operate in Quasi-Resonance (QR) mode and in Discontinuous Conduction Mode (DCM) with valley detection. Both controllers are switched independently.

The PFC output power is on-time controlled for simplicity. It is not necessary to sense the phase of the mains voltage. The flyback output power is current mode controlled for good suppression of the input voltage ripple.

The communication circuitry between the controllers is integrated and no adjustment is needed.

The voltage and current levels mentioned in this application note are typical values. A detailed description of the pin level spreading can be found in the *TEA1752T\_LT data sheet*.

#### 1.1 Scope

This application note describes the functionality of the TEA1752 and the adjustments needed within the power converter application.

The large signal parts of the PFC and the flyback power stages, the design and the data for the coil and the transformer are dealt with in a separate application note.

#### 1.2 The TEA1752 GreenChip III controller

The features of the GreenChip III allow a power supply engineer to design a reliable, cost-effective and efficient switched mode power supply with a minimum number of external components.

#### 1.2.1 Key features

- PFC and flyback controller integrated in one SO-16 package

- Switching frequencies of PFC and flyback are independent of each other

- No external hardware required for the communication between both controllers

- High level of integration, resulting in minimal external component count

- Integrated mains voltage enable and brownout protection

- Fast latch reset function implemented

#### **1.2.2 System features**

- Safe restart mode for system fault conditions

- High voltage start-up current source (5.4 mA)

- Reduction of HV current source (1 mA) in Safe restart mode

- Wide V<sub>CC</sub> range (38 V)

- MOSFET driver voltage limited

- Easy control of start-up behavior and V<sub>CC</sub> circuit

- General purpose input for latched protection

- Internal IC overtemperature protection

- One high-voltage spacer between the HV pin and the next active pin

- Open pin protection on the VINSENSE, VOSENSE, PFCAUX, FBCTRL and FBAUX pins

#### 1.2.3 PFC features

- Dual output voltage boost converter

- QR/DCM operation with valley switching

- Frequency limitation (250 kHz) to reduce switching losses and ElectroMagnetic Interference (EMI)

- t<sub>on</sub> controlled

- Mains input voltage compensation for control loop for good transient response

- OverCurrent Protection (OCP)

- Soft start and soft stop

- Open/short detection for PFC feedback loop: no external Overvoltage Protection (OVP) circuit necessary

- Adjustable delay for turning off the PFC

#### 1.2.4 Flyback features

- QR/DCM operation with valley switching

- Frequency Reduction (FR) with fixed minimum peak current and valley switching to maintain high efficiency at low output power levels without audible noise

- Frequency limitation (125 kHz) to reduce switching losses and EMI

- Current mode controlled

- Overcurrent protection

- Soft start

- Accurate OVP through auxiliary winding

- Time-out protection for output overloads and open flyback feedback loop, available as safe restart (TEA1752T) or latched (TEA1752LT) protection

#### **1.3 Application schematic**

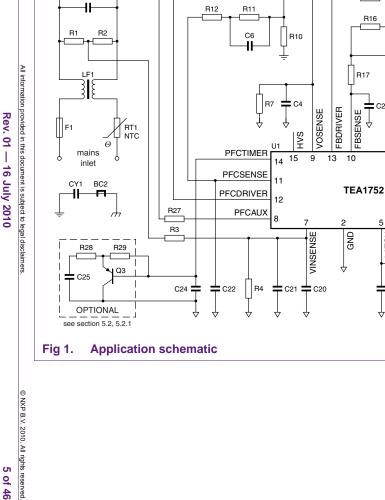

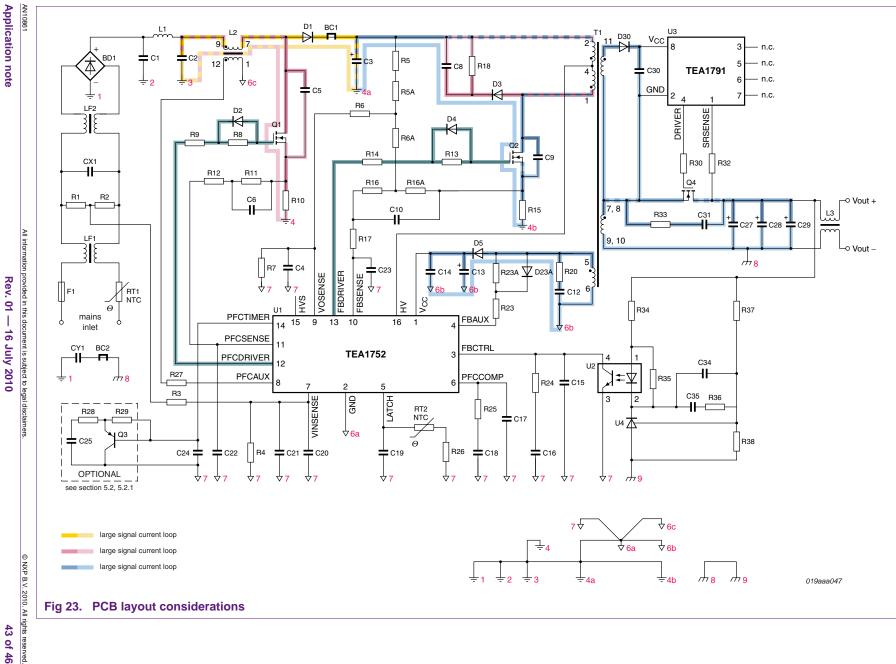

Figure 1 shows the complete functional schematic of the TEA1752 application.

AN10861 Application note

L1

C2

R9

÷

C1

÷

BD1

÷

LF2

318

CX1

L2

4

D2 H R8

Q1

Ē

\_9 7 ل

12

**≠** C5

4 ÷

Сз

R6

R14

R5

R5A

R6A

R16A

C10

╢

C23

5

LATCH

📫 C19

4

R18

D5

Ю

🕇 C13

FBAUX

FBCTRL

PFCCOMP

R25

C18

4

Ą

4

3

6

R26

Ą

۲<sub>00</sub>

RT2 NTC/

đ

Θ

₹

16 1 D3

Ю

**⇒** C9

R15

Ŧ

R23A 🛨 D23A

R23

C17

$\Delta$

茾 C8

D4

Ŕ

R13

5 of 46

**NXP Semiconductors**

U3

DRIVER

TEA1791

SRSENSE

R32

R30

C31

C34

╢

C35 R36

019aaa027

Q4

— n.c. 3

n.c.

– n.c.

n.c.

C27 🚔 C28 🚔 C29

$\mathcal{H}$

R37

R38

- Vout +

Lo Vout -

L3

V<sub>CC</sub> 8

C30

GND

R33

R34

$\mathbf{\nabla}$

$\mathcal{H}$

2

R35

T1

25

4

1

11

7, 8

9, 10

5

U2

3

4

R20 .

4

R24 📥 C15

4

🛨 C16

4

AN10861

# GreenChip III TEA1752 integrated PFC and flyback controller

### 2. Pin description

| Pin | Name            | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>CC</sub> | Supply voltage: V <sub>startup</sub> = 22 V, V <sub>th(UVLO)</sub> = 15 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |                 | At mains switch-on, the capacitor connected to this pin is charged to $V_{startup}$ by the internal HV current source. When the pin voltage is lower than 0.65 V the charge current is limited to 1 mA to prevent overheating of the IC if the $V_{CC}$ pin is short-circuited. When the pin voltage is between 0.65 V and $V_{th(UVLO)}$ , the charge current is 5.4 mA to enable a fast start-up. When it is between $V_{th(UVLO)}$ and $V_{startup}$ , the charge current is limited to 1 mA again to reduce the safe restart duty cycle. This results in a reduction of the input power during fault conditions. When $V_{startup}$ is reached, the HV current source is pinched off and $V_{CC}$ is regulated to $V_{startup}$ until the flyback starts. See Section 3.2 for a complete description of the start-up sequence. |

| 2   | GND             | Ground connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3   | FBCTRL          | Control input for flyback for direct connection of the optocoupler.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

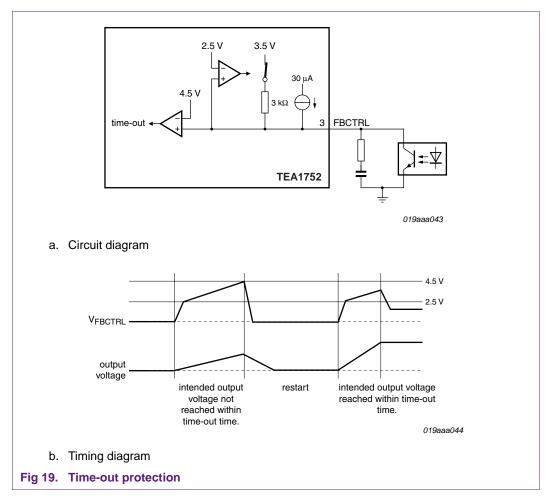

|     |                 | At a control voltage of 2 V the flyback delivers maximum power. At a control voltage of 1.5 V the flyback enters the Frequency reduction mode. At 1.3 V the flyback stops switching. There is an internal 30 $\mu$ A current source connected to the pin, which is controlled by the internal logic. This current source can be used to implement a time-out function to detect an open control loop or a short circuit of the output voltage. The time-out function car be disabled with a resistor of 100 k $\Omega$ between this pin and ground.                                                                                                                                                                                                                                                                                |

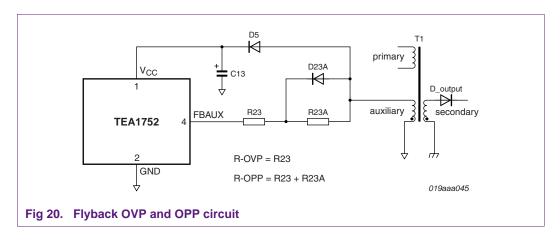

| 4   | FBAUX           | Input from auxiliary winding for transformer demagnetization detection,<br>mains dependent OverPower Protection (OPP) and OverVoltage Protection<br>(OVP) of the flyback.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

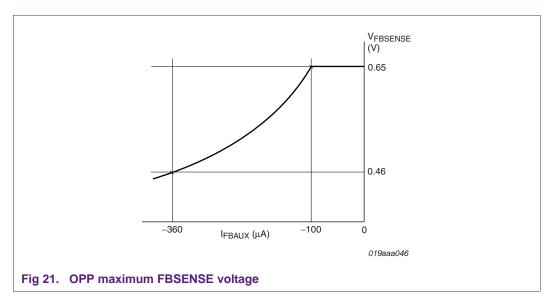

|     |                 | The combination of the demagnetization detection and the valley detection at pin HV determines the switch-on moment of the flyback in the valley. A flyback OVP is detected at a current higher than 300 $\mu$ A to the FBAUX pin. Internal filtering prevents false detection of an OVP. The flyback OPP starts at a current lower than –100 $\mu$ A from the FBAUX pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

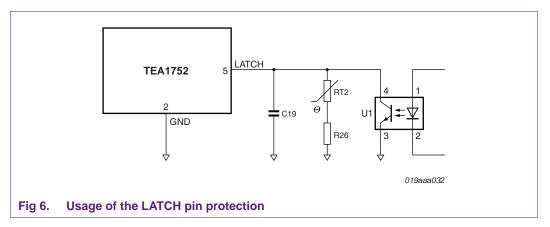

| 5   | LATCH           | General purpose latched protection input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |                 | When V <sub>startup</sub> (on pin 1) is reached, this pin is charged to 1.35 V before the PFC and the flyback can be enabled. The latched protection is triggered when the pin is pulled below 1.25 V and the PFC and the flyback are disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |                 | An internal 80 $\mu$ A current source is connected to the pin, which is controlled<br>by the internal logic. Because of this current source, a<br>Negative Temperature Coefficient (NTC) resistor for temperature protection<br>can be directly connected to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6   | PFCCOMP         | Frequency compensation pin for the PFC control loop.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7   | VINSENSE        | Sense input for mains voltage. This pin has five functions:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |                 | <ul> <li>mains enable level: V<sub>start(VINSENSE)</sub> = 1.15 V;</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |                 | <ul> <li>mains stop level (brownout): V<sub>stop(VINSENSE)</sub> = 0.89 V;</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |                 | <ul> <li>mains voltage compensation for the PFC control loop gain bandwidth;</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |                 | <ul> <li>fast latch reset: V<sub>fir</sub> = 0.75 V;</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |                 | <ul> <li>dual boost switchover point: V<sub>bst(dual)</sub> = 2.2 V.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |                 | The voltage on pin VINSENSE must be an averaged DC value, representing<br>the AC line voltage. The pin is not used for sensing the phase of the mains<br>voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

#### Table 1. Pin description ...continued

| Table | Findesc   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin   | Name      | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

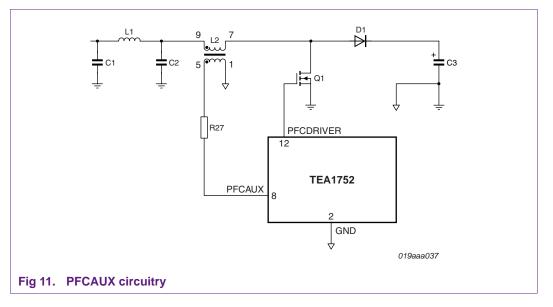

| 8     | PFCAUX    | Input from an auxiliary winding of the PFC coil for demagnetization timing and valley detection to control PFC switching.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       |           | The auxiliary winding needs to be connected via a 5 k $\Omega$ series resistor to prevent damage to the input because of lightning surges.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 9     | VOSENSE   | Sense input for the output voltage of the PFC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |           | VOSENSE pin, open-loop and short circuit detection:<br>V <sub>th(ol)(VOSENSE)</sub> = 1.15 V;                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       |           | Regulation of the PFC output voltage: V <sub>reg(VOSENSE)</sub> = 2.5 V;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |           | PFC soft OVP (cycle-by-cycle): V <sub>ovp(VOSENSE)</sub> = 2.63 V;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |           | Control output for the output voltage of the PFC:<br>- dual boost current: $I_{bst(dual)} = -15 \ \mu A$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 10    | FBSENSE   | Current sense input for flyback.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       |           | At this pin the sum of three voltages across three resistors is measured.<br>Selecting the proper resistor values:                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |           | • Prevents or minimizes the risk of saturation of the flyback transformer;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       |           | <ul> <li>Allows some adjustment for enabling or disabling the PFC;</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       |           | <ul> <li>Allows a system that operates line voltage independently.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       |           | The maximum setting level for $V_{sense(fb)max}$ is 0.63 V at dV/dt = 0 mV/µs.<br>The level of $V_{sense(fb)min}$ is 0.30 V at dv/dt = 0 mV/µs and is related to the fixed peak current through the flyback transformer when the flyback is running in Frequency reduction mode. There are two internal current sources connected to this pin, $I_{start(soft)fb}$ and $I_{adj(FBSENSE)}$ .                                                                                                                                                                              |

|       |           | $I_{start(soft)fb}$ is an internal current source of 60 $\mu A$ , which is controlled by the internal logic. The current source is used to implement a soft start function for the flyback. The flyback only starts when the internal current source can charge the soft start capacitor to a voltage of more than 0.63 V. Therefore a minimum soft start resistor of 16 k\Omega is required to guarantee the enabling of the flyback. The current source $I_{adj(FBSENSE)}$ is 3 $\mu A$ . It is intended to support the adjustment for enabling and disabling the PFC. |

| 11    | PFCSENSE  | Overcurrent protection input for PFC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |           | This input is used to limit the maximum peak current in the PFC core. The PFCSENSE is a switching-cycle-by-switching-cycle protection. When it reaches 0.52 V at $dV/dt = 50 \text{ mV}/\mu \text{s}$ the PFC MOSFET is switched off.                                                                                                                                                                                                                                                                                                                                    |

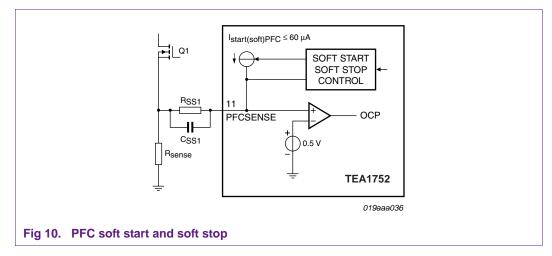

|       |           | An internal 60 $\mu$ A current source is connected to this pin, which is controlled by the internal logic. This current source is used to implement a soft start and soft stop function for the PFC to prevent audible noise. The PFC only starts when the internal current source can charge the soft start capacitor to a voltage of more than 0.5 V. A soft start resistor of at least 12 k $\Omega$ is required to guarantee the enabling of the PFC.                                                                                                                |

| 12    | PFCDRIVER | Gate driver output for PFC MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 13    | FBDRIVER  | Gate driver output for flyback MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Pin | Name     | Functional description                                                                                                                                                |

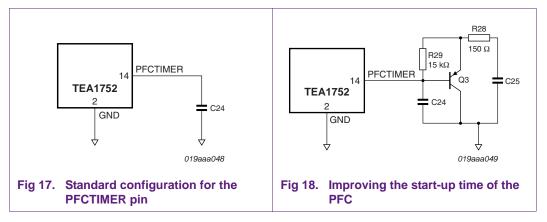

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14  | PFCTIMER | Timer pin to delay the turning off of the PFC when the load of the flyback is removed or minimized.                                                                   |

|     |          | The PFC is enabled when the voltage across this pin is low ( $\leq$ 1.27 V). It is disabled when the voltage is high ( $\geq$ 3.6 V).                                 |

| 15  | HVS      | High-voltage safety spacer, not connected.                                                                                                                            |

| 16  | HV       | High-voltage input for the internal start-up current source (output at pin 1) and valley sensing of the flyback.                                                      |

|     |          | The combination of the demagnetization detection at the FBAUX pin and the valley detection at the HV pin determine the switch-on moment of the flyback in the valley. |

#### 3. System description and calculation

#### 3.1 PFC and flyback start conditions

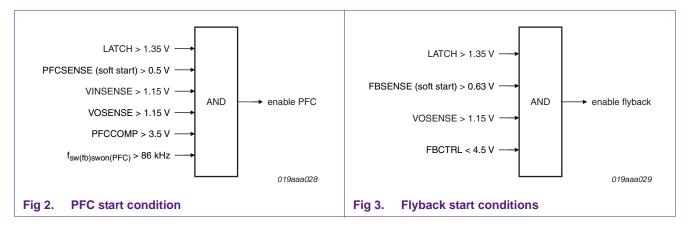

Figure 2 and Figure 3 show the conditions for enabling the PFC and the flyback. If start-up problems occur these conditions can be checked to find the cause of the problem. Some of the conditions are dynamic signals (see Figure 4) and should be checked with an oscilloscope.

#### 3.2 Start-up sequence

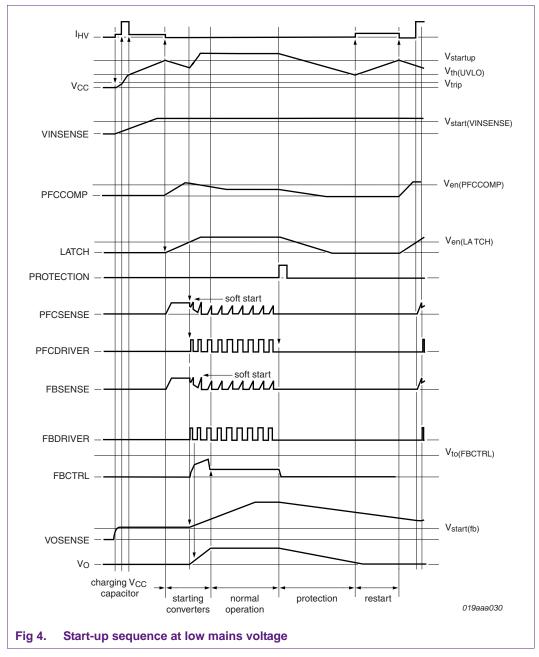

At switch-on with a low mains voltage the TEA1752 power supply has the following start-up sequence (see Figure 4):

- 1. The HV current source is set to 1.0 mA and the  $V_{CC}$  elcap is charged to 0.65 V to detect a possible short circuit at pin  $V_{CC}$ .

- 2. At V<sub>CC</sub> = 0.65 V, the HV current source is set to 5.4 mA and the V<sub>CC</sub> elcap is quickly charged to  $V_{th(UVLO)}$ .

- 3. At  $V_{CC} = V_{th(UVLO)}$ , the HV current source is set to 1.0 mA again and the  $V_{CC}$  elcap is charged to  $V_{startup}$ .

- 4. At V<sub>startup</sub>, the HV current source is switched off and the 80  $\mu$ A LATCH pin current source is switched on to charge the LATCH pin capacitor. At the same time the PFCSENSE and FBSENSE soft start current sources are switched on.

- 5. When the LATCH pin is charged to 1.35 V the PFC and the flyback can start switching, but only when the VINSENSE pin has reached a level of 1.15 V.

- 6. Four extra conditions have to be met for enabling the PFC: The soft start capacitor at pin PFCSENSE must be charged to 0.5 V, the voltage on the VOSENSE pin must be greater than 1.15 V, the capacitors connected to the PFCCOMP pin should be charged to 3.5 V and f<sub>sw(fb)swon(PFC)</sub> must be greater than 86 kHz.

**Remark:** The last condition is automatically met by the TEA1752 during (initial) start-up. This can be measured at the PFCTIMER pin. It is internally forced down to a low voltage, which means that the PFC is enabled.

- 7. The soft start capacitor at pin FBSENSE must be charged to 0.63 V and the voltage on pin FBCTRL must be lower than 4.5 V to enable the flyback. Normally, the voltage on pin FBCTRL is lower than 4.5 V at the first flyback switching cycle, unless the FBCTRL pin is open. When the flyback starts, the FBCTRL time-out current source is switched on.

- 8. When the flyback has reached its nominal output voltage, the V<sub>CC</sub> supply of the IC is taken over by the auxiliary winding. If the flyback feedback loop signal is missing, the time-out protection at the FBCTRL pin is triggered, both converters are switched off,  $V_{CC}$  drops to  $V_{th(UVLO)}$  and the IC continues with step 3 of the start-up cycle. This is the safe restart cycle.

#### **NXP Semiconductors**

# AN10861

#### GreenChip III TEA1752 integrated PFC and flyback controller

The charge time of the soft start capacitors can be chosen independently for the PFC and the flyback, based on their values.

#### 3.3 V<sub>CC</sub> cycle in safe restart protection mode

In Safe restart mode the controller goes through the steps 3 to 8 as described in <u>Section 3.2</u>.

#### 3.4 Mains voltage sensing and brownout

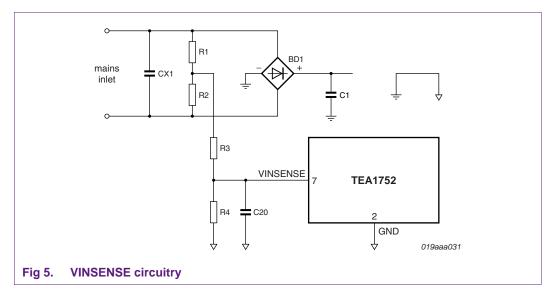

The mains input voltage is measured through the VINSENSE pin. When the VINSENSE pin has reached V<sub>start(VINSENSE)</sub> (1.15 V) the PFC can start switching, but only if the other start conditions are met as well, see <u>Section 3.1</u>. As soon as the voltage on pin VINSENSE drops below V<sub>stop(VINSENSE)</sub> (0.89 V), the PFC stops switching. The flyback however, continues switching until its maximum on-time protection, t<sub>on(fb)max</sub> (40  $\mu$ s) is triggered. When this protection is triggered, the IC stops switching and enters Safe restart mode.

The voltage on pin VINSENSE must be an average DC value, representing the mains input voltage. The system works optimally with a time constant of approximately 150 ms at the VINSENSE pin. The high time constant on pin VINSENSE prevents a fast restart of the PFC after a mains dropout, therefore the voltage at the VINSENSE pin is clamped to 100 mV below the  $V_{start(VINSENSE)}$  level. This guarantees a fast PFC restart after recovery of the mains input voltage.

#### 3.4.1 Discharge of mains input capacitor

The X-capacitors in the ElectroMagnetic Compatibility (EMC) input filtering must be discharged with a time constant of  $\tau < 1$  second for safety reasons (see Ref. 1).

In a typical 90 W adapter application with CX1 = 220 nF, the replacement value resistor value  $R_V$  is determined by:

$$R_V = R + \frac{R \times (R_3 + R_4)}{R + R_3 + R_4} \tag{1}$$

Where:

The value of  $R_V$  must be lower than or equal to the following:

$$R_V \le \frac{\tau}{CX1} = \frac{1}{220 \ nF} = 4.55 \ M\Omega$$

#### 3.4.2 Brownout voltage adjustment

The rectified AC input voltage is measured via R1 and R2. Each resistor alternately senses half the sine wave, so both resistors must have the same value. The average voltage sensed at the connection of R1 and R2 is calculated with Equation 2:

$$V_{avg} = \frac{2 \times \sqrt{2}}{\pi} \cdot V_{acrms} \tag{2}$$

The V (AC) brownout RMS level is calculated with Equation 3:

$$V_{brownout} (AC) = \frac{\pi}{2 \times \sqrt{2}} \times V_{stop(VINSENSE)} \times \frac{(R_V + R_3 + R_4)}{R_4}$$

(3)

Where: V<sub>stop(VINSENSE)</sub> = 0.89 V

At a brownout threshold of 68 V (AC) and in compliance with *IEC-60950 chapter 2.1.1.7* "*discharge of capacitors in equipment*" (Ref. 1). Example values are shown in Table 2.

| Table 2. | VINSENSE component values |        |        |       |  |

|----------|---------------------------|--------|--------|-------|--|

| CX1      | R1                        | R2     | R3     | R4    |  |

| 220 nF   | <b>2</b> ΜΩ               | 2 MΩ   | 560 kΩ | 47 kΩ |  |

| 330 nF   | 1.5 MΩ                    | 1.5 MΩ | 820 kΩ | 47 kΩ |  |

| 470 nF   | 1 MΩ                      | 1 MΩ   | 1.1 MΩ | 47 kΩ |  |

A value of 3.3  $\mu$ F for capacitor C20, with 47 k $\Omega$  at R4, gives the recommended time constant of ~150 ms at the VINSENSE pin.

#### 3.5 Internal Overtemperature Protection (OTP)

The IC has an internal temperature protection to protect the IC from overheating by overloads at the V<sub>CC</sub> pin. When the junction temperature exceeds the thermal shutdown temperature, the IC stops switching. As long as the OTP is active, the V<sub>CC</sub> capacitor is not recharged from the HV mains. The OTP circuit is supplied from the HV pin if the V<sub>CC</sub> supply voltage is not sufficient. The OTP is a latched protection.

#### 3.6 LATCH pin

The LATCH pin is a general purpose input pin, which can be used to latch both converters off. The pin sources a bias current  $I_{O(LATCH)}$  of 80 µA for the direct connection of an NTC. When the voltage on this pin is pulled below 1.25 V, switching of both converters is stopped immediately and V<sub>CC</sub> starts cycling between the V<sub>th(UVLO)</sub> and V<sub>startup</sub> without a restart. Switching off and then switching on the mains input voltage triggers the fast latch reset circuit and resets the latch (see Section 3.7).

At start-up, the LATCH pin has to be charged to above 1.35 V before both converters can be enabled. Charging of the LATCH pin starts when  $V_{CC} = V_{startup}$ .

No internal filtering is present at the LATCH pin. A 10 nF capacitor must be placed between this pin and the IC GND pin to prevent false triggering, also when the LATCH pin function is not used.

Latching on application overtemperature occurs when the total resistance value of the NTC and its series resistor drops below the following:

$$R_{OTP} = \frac{V_{prot(LATCH)}}{I_{O(LATCH)}} = \frac{1.25 \ V}{80 \ \mu A} = 15.6 \ k\Omega$$

(4)

The optocoupler triggers the latch if the driven optotransistor conducts more than 80  $\mu$ A.

#### 3.7 Fast latch reset

Switching off and then switching on the mains input voltage resets the latched protection. After the mains input is switched off, the voltage on pin VINSENSE drops below  $V_{flr}$  (0.75 V). This triggers the fast latch reset circuit, but does not reset the latched protection. After the mains input is switched on, the voltage on pin VINSENSE rises again. The latch is reset when the level has passed 0.85 V. The system restarts when the V<sub>CC</sub> pin is charged to V<sub>startup</sub> (See step 4 of Section 3.2).

#### 4. PFC description and calculation

The PFC operates in QR mode or DCM mode with valley detection to reduce the switch-on losses. The maximum switching frequency of the PFC is limited to 250 kHz to reduce switching losses. If necessary, one or more valleys are skipped to keep the frequency below 250 kHz.

The PFC of the TEA1752 is designed as a dual boost converter with two output voltage levels that are dependent on the mains input voltage range. The advantage is that the overall system efficiency at low mains is improved because of the reduction of the PFC switching losses. In low and medium power adapters (< 120 W) the contribution of PFC switching losses to the total losses is relatively high.

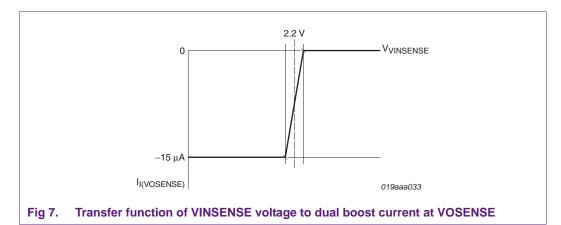

The dual output voltage is controlled by an internal current source of 15  $\mu$ A at pin VOSENSE. As shown in <u>Figure 7</u>, the mains input voltage measured at pin VINSENSE is used to control the internal current source. This current source, in combination with the resistors at pin VOSENSE, sets the lower PFC output voltage. At high mains, the current source is switched off. Therefore, the maximum PFC output voltage is not affected by the

AN10861

© NXP B.V. 2010. All rights reserved.

accuracy of the current source. In a typical adapter with a PFC output voltage of 385 V (DC) at high mains, the PFC output voltage is 250 V (DC) at low mains. A voltage of 2.2 V at pin VINSENSE corresponds with a mains input voltage of approximately 180 V (AC). The small slope at the transfer function ensures a stable switchover of the PFC output voltage without hiccups.

The PFC is switched off to ensure high efficiency during low output currents and standby (no output current). After switch-off the bulk elcap voltage drops to *line voltage*  $\times \sqrt{2}$ .

#### 4.1 PFC output power and voltage control

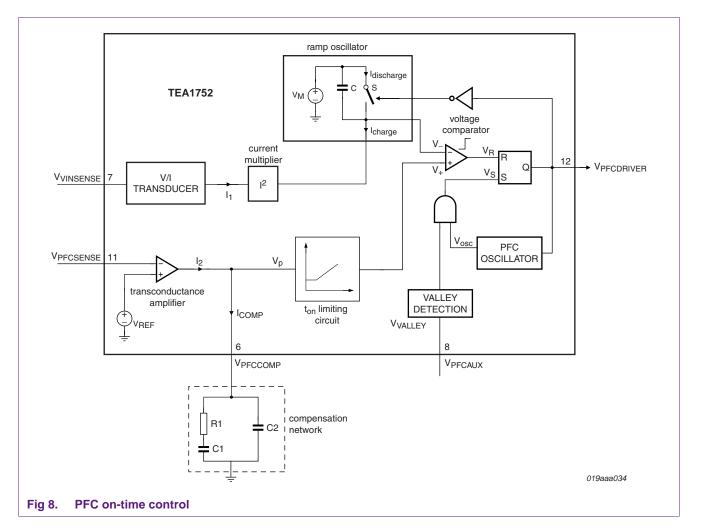

The PFC of the TEA1752 is on-time controlled, therefore it is not necessary to measure the mains phase angle. The on-time is kept constant during the half sine wave to obtain a good Power Factor (PF) and a class-D Mains Harmonics Reduction (MHR).

The PFC output voltage is controlled through the VOSENSE pin. At the VOSENSE pin there is a transconductance error amplifier with a reference voltage of 2.5 V. The error at the VOSENSE pin is converted with 80  $\mu$ A/V to a current on pin PFCCOMP. The voltage on pin PFCCOMP, in combination with the voltage on pin VINSENSE, determines the PFC on-time.

AN10861

14 of 46

#### **NXP Semiconductors**

# AN10861

#### GreenChip III TEA1752 integrated PFC and flyback controller

A network with one resistor and two capacitors at the PFCCOMP pin is used to stabilize the PFC control loop. The mathematical equation for the transfer function of a boost converter contains the square of the mains input voltage. In a typical application this results in a low regulation bandwidth for low mains input voltages and a high regulation bandwidth at high input voltage. The result might be that at high mains input voltages it can be difficult to meet the MHR requirements. The TEA1752 uses the mains input voltage measured through the VINSENSE pin to compensate the control loop gain as a function of the mains input voltage. As a result the gain is constant over the entire mains input voltage range.

The voltage at the VINSENSE pin must be an average DC value, representing the mains input voltage. The system works optimally with a time constant of approximately 150 ms at the VINSENSE pin.

#### 4.1.1 Setting the PFC output voltage

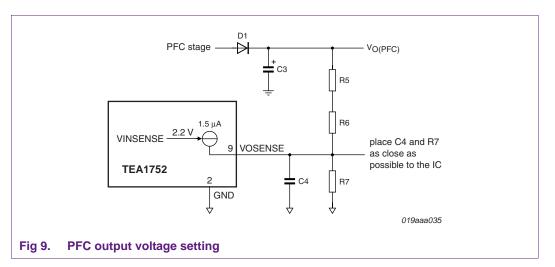

The PFC output voltage is set with a resistor divider between the PFC output voltage and the VOSENSE pin. In Normal mode, the PFC output voltage is regulated so that the voltage on the VOSENSE pin is equal to  $V_{reg(VOSENSE)} = 2.5 V$ .

15 of 46

#### GreenChip III TEA1752 integrated PFC and flyback controller

Two resistors of 4.7 M $\Omega$  (1 %) can be used between the bulk elcap and the VOSENSE pin. The dimensioning of the I<sub>bst(dual)</sub> current source (–15  $\mu$ A) has been adapted to the use of these resistor values. With a resistor value of 4.7 M $\Omega$  for R5 and R6 and 60 k $\Omega$  to 62 k $\Omega$  for R7 a universal mains adapter has a PFC output voltage of approximately 380 V to 390 V at high mains and 240 V to 250 V at low mains.

The resistor R7 (1 %) between the VOSENSE pin and ground can be calculated with Equation 5:

$$R7 = \frac{(R5 + R6) \times V_{reg(VOSENSE)}}{(V_{O(PFC)} - V_{reg(VOSENSE)})}$$

(5)

Example with a regulated PFC output voltage of 382 V:

$$R7 = \frac{(4.7 \ M\Omega + 4.7 \ M\Omega) \times 2.5 \ V}{(382 \ V - 2.5 \ V)} = 62 \ k\Omega \ (1 \ \%)$$

At low mains the 15  $\mu$ A current source I<sub>bst(dual)</sub> is active. The lower PFC output voltage can be calculated with Equation 6:

$$V_{O(PFC)low} = \frac{R5 + R6 + R7}{R7} \cdot (V_{reg(VOSENSE)} - I_{bst(dual)} \cdot R7)$$

(6)

Example for calculating the lower PFC output voltage:

- R5 and R6 = 4.7 M $\Omega$

- R7 = 62 kΩ

$$V_{O(PFC)low} = \frac{4.7 \ M\Omega + 4.7 \ M\Omega + 62 \ k\Omega}{62 \ k\Omega} \cdot (2.5 \ V - 15 \ \mu A \cdot 62 \ k\Omega) = 240 \ V$$

The function of capacitor C4 at the VOSENSE pin is to filter noise and to prevent false triggering of the protection modes because of MOSFET switching noise, mains surge events or ElectroStatic Discharge (ESD) events. False triggering of the  $V_{ovp(VOSENSE)}$  protection can cause audible noise and disturbance of the AC mains input current. False

triggering of the  $V_{th(ol)(VOSENSE)}$  protection causes a safe restart cycle. A time constant of 500 ns to 1 ms at the VOSENSE pin should be sufficient, which results in a value of 10 nF for capacitor C4.

It is advisable to place R7 and C4 as close as possible to the IC between the VOSENSE pin and the IC GND pin.

#### 4.1.2 Calculation of the PFC soft start and soft stop components

The soft start and soft stop are implemented through the RC network at the PFCSENSE pin.

$R_{SS1}$  must have a minimum value of 12 k $\Omega$  to ensure that the voltage  $V_{start(soft)PFC}$  of 0.5 V is reached to enable the start-up of the PFC. See <u>Section 3.2</u> for a description of start-up.

The total soft start or soft stop time is:  $t_{softstart} = 3 \times R_{SSI} \times C_{SSI}$

It is advised to keep the soft start time of the PFC shorter than the soft start time of the flyback. It is also advised that the soft start time is kept within a range of 2 ms to 5 ms.

With C6 = 100 nF and R11 = 12 k $\Omega$ , the total soft start time is 3.6 ms.

#### 4.2 PFC demagnetizing and valley detection

The PFC MOSFET is switched on after the transformer is demagnetized. The internal circuitry connected to the PFCAUX pin detects the end of the secondary stroke. It also detects the voltage across the PFC MOSFET. The next primary stroke is started when the voltage across the PFC MOSFET is at its minimum in order to reduce switching losses and electromagnetic interference (EMI) (valley switching).

The maximum switching frequency of the PFC is limited to 250 kHz to reduce the switching losses. If necessary, one or more valleys are skipped to keep the frequency below 250 kHz.

If no demagnetization signal is detected on pin PFCAUX, the controller generates a Zero Current Signal (ZCS) 50  $\mu$ s after the last PFC gate signal. If no valley signal is detected on this pin, the controller generates a valley signal 4  $\mu$ s after demagnetization was detected.

AN10861

**Application note**

#### GreenChip III TEA1752 integrated PFC and flyback controller

#### 4.2.1 Design of the PFCAUX winding and circuit

It is advised to set the voltage on pin PFCAUX as high as possible, but still within the absolute maximum voltage rating of  $\pm$  25 V. Doing this improves the valley detection at low ringing amplitudes.

Taking into account its absolute maximum rating of  $\pm$  25 V, the voltage on pin PFCAUX must be set as high as possible to guarantee valley detection at low ringing amplitudes.

The number of turns of the PFCAUX winding can be calculated with Equation 7:

$$N_{aux\_max} = \frac{V_{PFCAUX}}{V_{Lmax}} \times N_p = \frac{25 V}{V_{Lmax}} \times N_p$$

(7)

- V<sub>PFCAUX</sub> is the absolute maximum rating of the PFCAUX pin

- V<sub>Lmax</sub> is the maximum voltage across the PFC primary winding

The PFC output voltage at the PFC<sub>OVP</sub> level determines the maximum voltage across the PFC primary winding and can be calculated with Equation 8:

$$V_{Lmax} = \frac{V_{ovp(VOSENSE)}}{V_{reg(VOSENSE)}} \times V_{O(PFC)} = \frac{2.63 V}{2.5 V} \times V_{O(PFC)}$$

(8)

When a PFC coil with a higher number of auxiliary turns is used, a resistor voltage divider can be placed between the auxiliary winding and pin PFCAUX. The total resistive value of the divider should be lower than 10 k $\Omega$  to prevent delay of the valley detection by parasitic capacitance.

The polarity of the signal at the PFCAUX pin must be reversed compared to the PFC MOSFET drain signal.

It is recommended to have a 5 k $\Omega$  resistor between the PFC auxiliary winding and pin PFCAUX to protect the pin against electrical overstress, for example, during lightning surge events. This resistor should be placed as close as possible to the IC to prevent incorrect valley switching of the PFC because of external disturbances.

#### 4.3 PFC protection modes

#### 4.3.1 VOSENSE overvoltage protection

Overvoltage can occur across the bulk elcap during the initial start-up and large load changes. This overvoltage is caused by the relative slow response of the PFC control loop. The PFC control loop response must be relatively slow to guarantee a good power factor and meet the MHR requirements. The OverVoltage Protection (OVP) at the VOSENSE pin limits the overvoltage. When the  $V_{ovp(VOSENSE)}$  level of 2.63 V is detected, the PFC MOSFET is switched off immediately regardless of the on-time setting. The switching of the MOSFET remains blocked until the voltage on pin VOSENSE drops below 2.63 V again.

When the resistor between the VOSENSE pin and ground is open, the OVP is also triggered.

The peak voltage across the bulk elcap generated by the PFC because of an overshoot and limited by the PFC OVP can be calculated with Equation 9:

$$V_{O(PFC)peak} = \frac{V_{ovp(VOSENSE)}}{V_{reg(VOSENSE)}} \cdot V_{O(PFC)nominal} = \frac{2.63 V}{2.5 V} \cdot V_{O(PFC)nominal}$$

(9)

#### 4.3.2 VOSENSE open and short pin detection

The VOSENSE pin, which is sensing the PFC output voltage, has an integrated protection circuit to detect an open and short circuited pin. This pin can also sense that one of the resistors in the voltage divider is open. Therefore the VOSENSE pin is completely fail-safe. It is not necessary to add an external OVP circuit for the PFC. An internal current source pulls the pin down to below the  $V_{th(ol)(VOSENSE)}$  detection level (1.15 V) when the pin is open. When  $V_{th(ol)(VOSENSE)}$  is detected, level switching of the PFC and the flyback MOSFETs is blocked until the voltage on pin VOSENSE rises to above 1.15 V again.

#### 4.3.3 VINSENSE open pin detection

The VINSENSE pin, which senses the mains input voltage, has an integrated protection circuit for detecting an open pin. An internal current source pulls the pin down to below  $V_{stop(VINSENSE)}$  (0.89 V) when the pin is open.

#### 4.3.4 Overcurrent protection

The overcurrent protection limits the maximum current through the PFC MOSFET and PFC coil. The current is measured via a current sense resistor in series with the MOSFET source. The MOSFET is switched off immediately when the voltage at pin PFCSENSE exceeds the V<sub>sense(PFC)max</sub> level of 0.52 V at dV/dt = 50 mV/ $\mu$ s. The OCP is a switching-cycle-by-switching-cycle protection.

It is recommended to take into account a margin of 0.1 V to avoid false triggering of the PFC OCP by switching of the flyback. False triggering of the  $V_{sense(PFC)max}$  protection can cause disturbances to the AC mains input current. It is also advised that a small capacitor between 100 pF and 220 pF is placed directly at the PFCSENSE pin to suppress external disturbance.

The current sense resistor can be calculated with Equation 10:

$$R_{OCP(PFC)} = \frac{V_{sense(PFC)max} - V_{margin}}{I_{pQR(PFC)max}} = \frac{0.52 \ V - 0.1 \ V}{I_{pQR(PFC)max}}$$

(10)

Where: IpQR(PFC)max is the maximum PFC peak current at the high load and low mains.

The maximum peak current for the PFC operating in Quasi-resonant mode can be calculated with Equation 11:

$$I_{pQR(PFC)max} = \frac{2\sqrt{2} \cdot P_{i(max)} \cdot 1.1}{Vac_{min}} = \frac{2\sqrt{2} \cdot \frac{P_{o(max)}}{\eta} \cdot 1.1}{Vac_{min}}$$

(11)

Where:

- P<sub>o(max)</sub> is the maximum output power of the flyback

- 1.1 is a factor to compensate for the dead time between zero current in the PFC inductor at the end of the secondary stroke and the detection of the first valley in Quasi-resonant mode

- $\eta$  is the expected efficiency of the total converter at maximum output power

- Vacmin is minimum mains input voltage.

#### 5. Flyback description and calculation

#### 5.1 Flyback output power control

An important aspect of the TEA1752 flyback system is that it waits until the transformer is demagnetized and at least one valley has appeared before it is magnetized again for the next cycle. The FBAUX pin detects demagnetization via the auxiliary winding. The HV pin detects the bottom of the valley via the drain of the MOSFET or the central tap of the primary winding.

(12)

#### GreenChip III TEA1752 integrated PFC and flyback controller

The output power ( $P_0$ ) of the flyback can be calculated with Equation 12:

$$P_O = \frac{1}{2} \cdot L_p \cdot I_p^2 \cdot fs \cdot \eta$$

Where:

- L<sub>p</sub> stands for the primary inductance of the flyback transformer

- Ip stands for the peak current through the flyback transformer

- f<sub>S</sub> stands for operating frequency of the flyback

- $\eta$  stands for the efficiency of the flyback

$L_p$  is selected at the start of the design, so the setting of the primary peak current controls the output power. The switching frequency is a result of external application parameters and internal IC parameters.

External application parameters are the transformer turns ratio, the primary inductance, the drain source capacitance, the input voltage, the output voltage and the feedback signal from the control loop. Internal IC parameters are the oscillator setting, the setting of the peak current and the detection of demagnetization and valley.

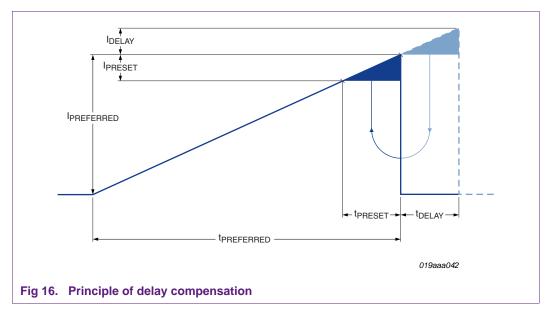

Another logical method of controlling the output power is keeping the primary peak current  $I_p$  fixed and changing the operating frequency. Output power and operating frequency are linearly related during this type of control. This method is usually only done at low output power. In this application note it is called "operating in Frequency reduction mode" (See Section 5.1.1.3).

The input voltage of the flyback is measured through pin FBAUX and used to implement an OverPower Protection (OPP). The OPP keeps the maximum output power of the flyback constant over the input voltage.

The flyback has an accurate OVP circuit. The overvoltage is measured through pin FBAUX. Both controllers (flyback and PFC) are switched off in a latched protection when an overvoltage is detected.

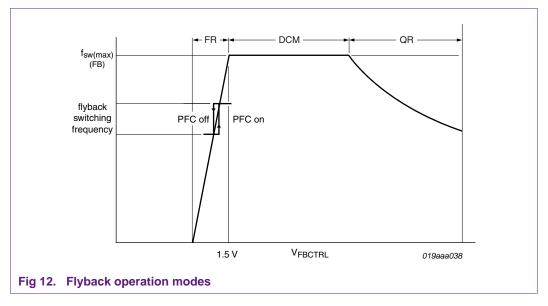

#### 5.1.1 Three different operation modes of the TEA1752

At initial start-up, the flyback always starts at the maximum output power. This means that the system starts up in the so-called Quasi-resonant mode. The flyback of the TEA1752 passes through three operation modes (see Figure 12) from maximum to minimum output power:

- Quasi-Resonant (QR) mode

- Discontinuous Conduction Mode (DCM

- Frequency Reduction (FR) mode

Demagnetization detection and valley switching circuitry inside the IC is active in all three different operation modes.

#### GreenChip III TEA1752 integrated PFC and flyback controller

#### 5.1.1.1 Quasi-resonant mode

The flyback operates in Quasi-resonant mode at high and maximum output power. The output power is controlled by the peak current (see <u>Section 5.1</u>). A lower peak current than the maximum allowed value results in lower output power and a higher operating frequency until the maximum operating frequency is reached. The Quasi-resonant mode can easily be recognized. The next primary switching cycle starts when the bottom of the first valley is detected.

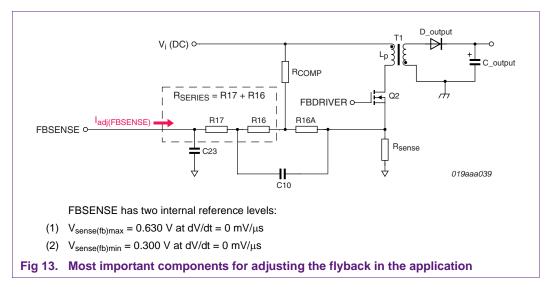

The primary peak current ( $I_p$ ) is set by the voltage on pin FBCTRL. It is advised to place a 10 nF noise filter capacitor (C15) as close as possible to the FBCTRL pin to avoid disturbance of the flyback by switching of the PFC MOSFET. The voltage on pin FBCTRL is measured back at the FBSENSE pin and can be calculated with Equation 13 (only valid during QR mode or DCM):

$$V_{sense(fb)} \cong 0.66 \times V_{FBCTRL} - I_{adj(FBSENSE)} \times (R16 + R17) - 0.69 V$$

<sup>(13)</sup>

Where:

- V<sub>FBCTRL</sub> is allowed to vary between the 1.5 V and 2.0 V (only valid during QR mode or DCM mode)

- I<sub>adj(FBSENSE)</sub> is related to a current source inside the IC, connected to the FBSENSE pin

- Resistors R16 and R17 can be found in the circuit diagram, see Figure 13.

#### GreenChip III TEA1752 integrated PFC and flyback controller

The peak current  $I_p$  through the flyback transformer is defined by:

$$I_p = \frac{V_{sense(fb)} - I_{adj(FBSENSE)} \times \{R16 + R17\}}{R_{sense}}$$

(14)

The maximum peak current  $I_{pmax}$  is determined by  $V_{sense(fb)max}$ . R16A is not mentioned in <u>Equation 14</u>, but this is explained in <u>Section 5.1.5</u>. Usually the required output power continues to drop after the initial start-up. This results in the flyback entering the Discontinuous conduction mode when the maximum switching frequency is reached.

#### 5.1.1.2 Discontinuous conduction mode

In DCM the output power is reduced by a further reduction of the peak current  $(I_p)$  and by skipping one or more valleys at the same time. In this mode the switching frequency is kept more or less constant. The exact switching frequency depends on the detection of the valleys, but it is never higher than the maximum frequency.

The output power is decreased by reducing the peak current and as a result more valleys are skipped until the voltage across FBCTRL drops below 1.5 V. When this happens the operating mode shifts from DCM to FR mode.

Sometimes the DCM is not reached when the selected primary inductance value of the transformer is too large. In such a situation the flyback skips the DCM when it is reducing power, it jumps directly from the QR mode to the FR mode.

#### 5.1.1.3 Frequency reduction mode

The voltage across the FBCTRL pin in Frequency reduction mode no longer sets the peak current. Instead it sets the operating frequency. The minimum peak current ( $I_{pmin}$ ) through the transformer is kept constant during the FR mode.

The ratio between  $I_{pmin}$  and  $I_{pmax}$  depends mainly on the value of the sense resistor  $R_{sense}$ , assuming that the core is not saturated at  $I_{pmax}$ . The output power is reduced by reducing the operating frequency and as a result more valleys are skipped.

The operating frequency of the flyback during FR mode determines if the PFC is turned on or turned off. The turn-on operating frequency for enabling the PFC is selected at a higher rate than the turn-off operating frequency. So the PFC is turned on at a higher output power and turned off again at a lower output power.

In general the output voltage of an adapter is fixed, so a higher or lower output power of the flyback results in a higher or lower output current.

The overall efficiency of the system is improved if the PFC is disabled at low output currents. For this reason the PFC is turned off above 25 % of the nominal output current. On the other hand, the PFC is turned on at larger output currents in order to improve the power factor of the line current. This is often done below 50 % of the nominal output current.

The hysteresis between turning on and turning off the PFC depends on the primary inductance value, the output power and the line voltage. It is therefore important to select the right inductance value to ensure enough PFC-on/PFC-off hysteresis. <u>Section 5.1.2</u> describes how this is done.

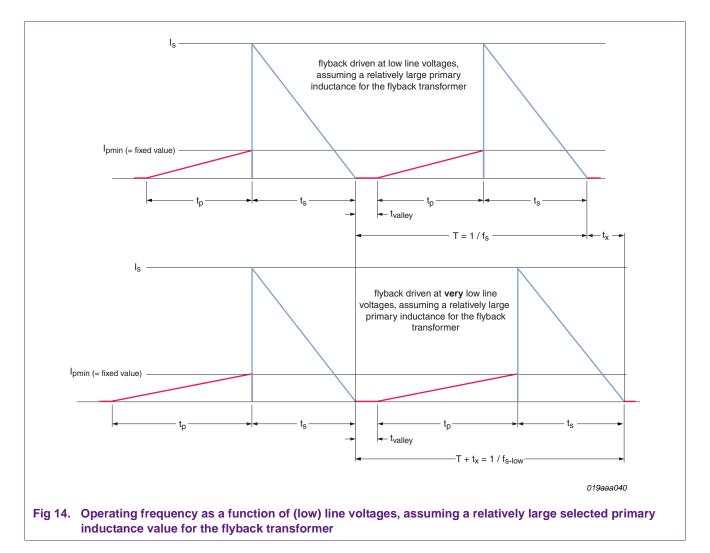

#### 5.1.2 The relationship between inductance value and the hysteresis of the PFC

The TEA1752 runs with a fixed minimum peak current ( $I_{pmin}$ ) to control the output power during the Frequency reduction mode, see <u>Section 5.1</u> (the value of  $I_{pmin}$  is calculated in <u>Equation 17</u>). Therefore the on-time (conducting time of the MOSFET) depends on the selected inductance value and the input voltage, it is linearly related to the inductance value and inversely proportional to the input voltage. The relationship between on-time and off-time of the MOSFET is fixed via the turns ratio of the transformer and the output voltage (neglecting the influence of the relatively short valley time). At lower line voltages the operating frequency and output power decrease when a relatively large primary inductance is selected, see also <u>Section 5.1</u> and <u>Figure 14</u>.

#### **NXP Semiconductors**

# AN10861

#### GreenChip III TEA1752 integrated PFC and flyback controller

The situation becomes worse when the primary inductance value is increased as well, because this limits the maximum deliverable output power at low line voltages even more (by default flyback runs at a lower operating frequency, assuming a fixed peak current). In practice this means that the flyback supports a limited amount of power at low line voltages. Asking more power activates the feedback loop and results in enabling the PFC at lower output power than was originally intended. In other words, the hysteresis between turning on and turning off the PFC becomes smaller at low line voltages in comparison with typical line voltages, assuming that a relatively large primary inductance value for the transformer is selected. When the selected primary inductance value is much too large, unwanted system behavior occurs, because there is no hysteresis left. The maximum inductance value should be limited to prevent this unwanted system behavior at low line voltages.

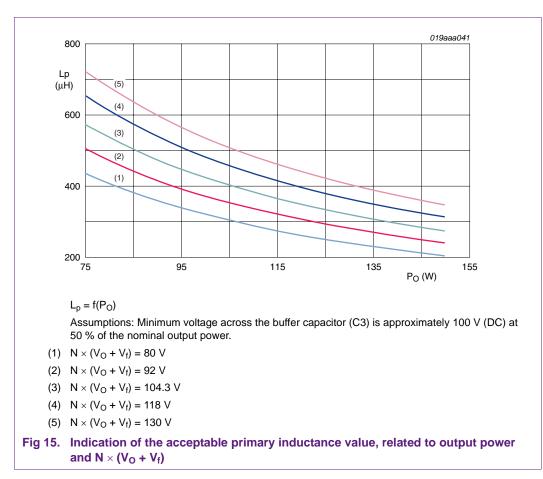

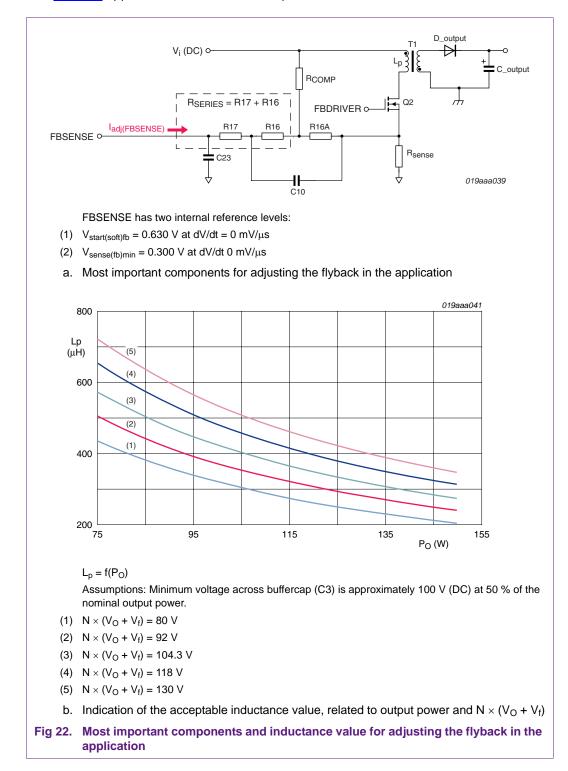

Most customers prefer a certain minimum hysteresis between turning on and turning off the PFC at low line voltages. So it is helpful to have an indication of the acceptable maximum primary inductance value of the transformer at the start of the design. Note that several assumptions have to be made to calculate these inductance values in <u>Figure 15</u>. Therefore these values should only be thought of as indications.

#### GreenChip III TEA1752 integrated PFC and flyback controller

Figure 15 shows an indication value for the primary inductance value of the flyback at different output powers and different turn ratios. Selecting a larger value than proposed here can result in too much loss of hysteresis. Selecting a smaller value prevents that, but causes more overall switching losses. The inductance values shown in Figure 15 results in loss of some hysteresis below roughly 115 V (AC) line voltage. However, they are usually still acceptable at 90 V (AC), assuming that the voltage across bulk elcap C3 does not drop too much. A rule of thumb is that the value of the buffer capacitor C3 in microfarads is usually selected equal to the output power in Watts. Applying this general rule of thumb results in a minimum voltage across the buffer capacitor of approximately 100 V (DC) at 90 V (AC) line voltage at 50 % of the nominal output power.

Selecting the inductance value with the help of  $\underline{Figure 15}$  is one method. Another method is using  $\underline{Equation 15}$ :

$$L_p = \left(\frac{N \times (V_O + V_f)}{104.3}\right) \times 43061 \times 10^{-6} \times \left(I_{O(nom)} \times (V_O + V_f)\right)^{-1.0005}$$

(15)

Where:

- I<sub>O(nom)</sub> stands for the nominal output current according to the type plate of the adapter

- V<sub>O</sub> stands for the output voltage

- V<sub>f</sub> stands for forward voltage across the secondary diode

- L<sub>p</sub> stands for the primary inductances of the flyback transformer

N is the turns ratio between the primary and secondary windings (N<sub>p</sub>/N<sub>s</sub>)

<u>Equation 15</u> gives some deviation at a low and a high value of the  $N \times (V_O + V_f)$  product. It is therefore recommended to keep this value between 80 V and 130 V.

Example:

- I<sub>O(nom)</sub> = 4.62 A

- V<sub>O</sub> = 19.5 V

- V<sub>f</sub> = 0.05 V

- $N \times (V_O + V_f) = 104.3$

$$L_p = \left(\frac{104.3}{104.3}\right) \times 43061 \times 10^{-6} \times \left(4.62 \times (19.5 + 0.05)\right)^{-1.0005} = 476 \times 10^{-6} \ H$$

The final value used is 450  $\mu$ H.

#### 5.1.3 Relationship between Ipmin and the required PFC-on/off level

The PFC is usually turned on and turned off between 50 % and 25 % of the nominal output current of the flyback. The PFC can only be turned on or turned off by the flyback when it is running in FR mode. The typical internal operating frequency of the flyback for turning on the PFC is 86 kHz and for turning off the PFC is 48 kHz. Using the average of both values (percentage wise and frequency wise) in combination with Equation 12 results in Equation 16:

$$0.375 \times I_{O(nom)} \times (V_O + V_f) = \frac{1}{2} \times L_p \times I_{pmin}^2 \times 67000 \times \eta_{fb}$$

(16)

Or:

$$I_{pmin} = \sqrt{\frac{2 \times 0.375 \times I_{O(nom)} \times (V_O + V_f)}{L_p \times 67000 \times \eta_{fb}}}$$

(17)

Where:

- 0.375 is the average value of 50 % and 25 % of the nominal output current

- V<sub>O</sub> is the output voltage

- V<sub>f</sub> is forward voltage across the secondary diode

- L<sub>p</sub> is the primary inductances of the flyback transformer

- 67000 is the average value of 86000 Hz and 48000 Hz

- η<sub>fb</sub> is the efficiency of the flyback (please use relatively high values, such as 0.97...0.98)

#### Example:

- I<sub>O(nom)</sub> = 4.62 A

- V<sub>O</sub> = 19.5 V

- V<sub>f</sub> = 0.05 V

- L<sub>p</sub> = 450 μH

- $\eta_{fb} = 0.98$

$$I_{pmin} = \sqrt{\frac{2 \times 0.375 \times 4.62 \times (19.5 + 0.05)}{450 \times 10^{-6} \times 67000 \times 0.98}} = 1.514 \text{ A}$$

#### 5.1.4 The influence of R<sub>sense</sub> and the series resistance R16 + R17

The sense resistor,  $R_{\text{sense}}$ , together with the series impedance R16 and R17, has four functions:

- Prevent or minimize the risk of saturation of the flyback transformer.

- Allow enough power to the output (assuming the inductance is not going into saturation).

- Allow some adjustment for enabling or disabling the PFC at a certain output power level. Note that the value of R<sub>sense</sub> is more dominant for this adjustment than the values of R16 and R17, as their influence is much smaller.

- R17 and C23 prevent FBSENSE being charged negative because of disturbances across R<sub>sense</sub>.

The saturation level  $(I_{p(sat)})$  of the transformer and the value of the sense resistor are important design parameters. Section 5.1.4.1 shows the calculation for the saturation level of the transformer. After that the maximum peak current  $(I_{pmax})$  through the transformer is determined. This value should preferably be below the saturation level of the transformer.

#### 5.1.4.1 Calculating the saturation current Ip(sat) of the flyback transformer

The saturation level of a transformer can be calculated with Equation 18.

$$I_{p(sat)} = \frac{N_p \times B_{max} \times A_e}{L_p}$$

(18)

Example with the following assumptions:

- N<sub>p</sub> = 32 turns

- B<sub>max</sub> = 390 mT (PQ3220, material PC44, B<sub>max</sub> at 100 °C)

- $A_e = 170 \times 10^{-6} \text{ m}^2$  (from transformer supplier data sheet)

- $L_p = 450 \times 10^{-6}$

Result:

$$I_{p(sat)} = \frac{32 \times 0.39 \times 170 \times 10^{-6}}{450 \times 10^{-6}} = 4.71 \text{ A}$$

Values for  $A_e$  and  $B_{max}$  can be found in the data sheet of the transformer supplier. The  $B_{max}$  value depends on temperature. It decreases rapidly at high operating temperatures. Therefore the  $B_{max}$  value should be selected at high operating temperatures. Saturation of the core does not happen when the maximum peak current ( $I_{pmax}$ ) is below the saturation current ( $I_{p(sat)}$ ). Section 5.1.4.2 shows the calculation of  $I_{pmax}$ . A saturated core does not deliver more power to the output, but only deteriorates the overall performance of the system (more stress and EMI and, worst case, a possible system failure).

#### GreenChip III TEA1752 integrated PFC and flyback controller

#### 5.1.4.2 Calculation of I<sub>pmax</sub> for flyback operating in Quasi-resonant mode

The flyback peak current operating in Quasi-resonant mode can be calculated with Equation 19:

$$I_{pmax} = \frac{-b + \sqrt{(b^2 - 4 \times a \times c)}}{2 \times a}$$

(19)

Where:

- $a = N \times V_{i(DC)min} \times L_p$

- $b = -2 \times I_O \times L_p \times \{N \times (V_O + V_f) + V_{i(DC)min}\}$

- $c = -2 \times I_O \times t_{valley} \times N \times V_{i(DC)min} \times (V_O + V_f)$

For a, b and c:

- V<sub>O</sub> is the output voltage

- N is the turns ratio between the primary and secondary windings (N<sub>p</sub>/N<sub>s</sub>)

- L<sub>p</sub> is the inductance value of the primary winding

- $t_{\text{valley}}$  is the valley time, sometimes also described as dead time. This time is usually around the 1.1  $\mu s$

- V<sub>i(DC)min</sub> is the minimum voltage across bulk elcap C3 at its nominal output load. In this example this is 75 V (DC). The actual voltage depends on how fast the PFC is enabled. It is therefore recommended to check this value in every application.

Examples:

- a =  $5.3333 \times 75 \times 450 \times 10^{-6} = 180 \times 10^{-3}$

- $b = -2 \times 4.62 \times 450 \times 10^{-6} \times \{5.3333 \times (19.5 + 0.05) + 75\} = -745.39 \times 10^{-3}$

- $c = -2 \times 4.62 \times 1.1 \times 10^{-6} \times 5.3333 \times 75 \times (19.5 + 0.05) = -79.4824 \times 10^{-3}$

$I_{pmax} (at I_0 = 4.62 \text{ A}) = \frac{745.39 \times 10^{-3} + \sqrt{(-745.39 \times 10^{-3})^2 - 4 \times 180 \times 10^{-3} \times -79.4824 \times 10^{-3}}}{2 \times 180 \times 10^{-3}} = 4.25 \text{ A}$

The calculated peak current is below the saturation level of 4.71 A (see Section 5.1.4.1). It is recommended to have some margin between this calculated value and the saturation level of the core. For example, the system might still run into a problem during a peak load. This is something that has to be checked as well for the final design. The calculation below shows the results if the assumed peak output current is 5.7 A and the PFC has been on for some time. It is assumed that the minimum voltage across buffer cap C3 is 240 V (DC).

- $a_1 = 5.3333 \times 240 \times 450 \times 10^{-6} = 576 \times 10^{-3}$

- $b_1 = -2 \times 5.70 \times 450 \times 10^{-6} \times \{5.3333 \times (19.5 + 0.05) + 240\} = -1.7661$

- $c_1 = -2 \times 5.70 \times 1.1 \times 10^{-6} \times 5.3333 \times 240 \times (19.5 + 0.05) = -313.8 \times 10^{-3}$