## AN10170

# Design guidelines for COG modules with NXP monochrome LCD drivers

Rev. 4 — 4 August 2014

**Application note**

## **Document information**

| Info     | Content                                                                                                                                                                                                                                                                                                        |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords | ITO layout LCD driver, PCA2117, PCF2113x, PCF2116x, PCF2119x, PCF21219DUGR, PCA85132U, PCA85133U, PCA85232U, PCA85233UG, PCA8538UG, PCA8576DU, PCA8576FUG, PCA9620U, PCF85132U, PCF85133U, PCF8532U, PCF8534AU, PCF8538UG, PCF8576CU, PCF8576DU, PCF8576EUG, PCF8577CU                                         |

| Abstract | This application note explains how to design the optimal ITO layout on the input side of the LCD driver IC. These design guidelines apply to all NXP monochrome LCD driver ICs unless otherwise stated. The guidelines help toward successful first-time module design and better overall display performance. |

## Design guidelines for COG modules with NXP monochrome drivers

## **Revision history**

| Rev | Date     | Description     |

|-----|----------|-----------------|

| v.4 | 20140804 | revised version |

| v.3 | 20090611 | revised version |

| v.2 | 20030205 | revised version |

| v.1 | 20021119 | first release   |

## **Contact information**

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

#### Design guidelines for COG modules with NXP monochrome drivers

## 1. Introduction

In COG applications, the designer must not neglect the resistance of ITO tracks. Special attention must be paid to the ITO layout in order to keep the effects of track resistance to an acceptable level. This Application Note explains how to design the optimal ITO layout on the input side of the driver IC for various power supply lines.

## 1.1 Who should read this application note?

It is important that engineers in charge of the LCD module design and ITO layout design on the interface side read this application note. Both module maker and OEM (set-maker) will find this application note useful.

## 2. Guidelines for power supply lines V<sub>SS</sub>, V<sub>DD</sub> and V<sub>LCD</sub>

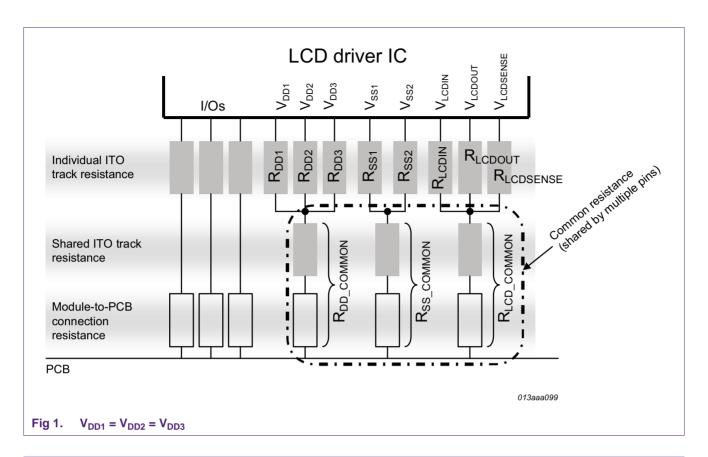

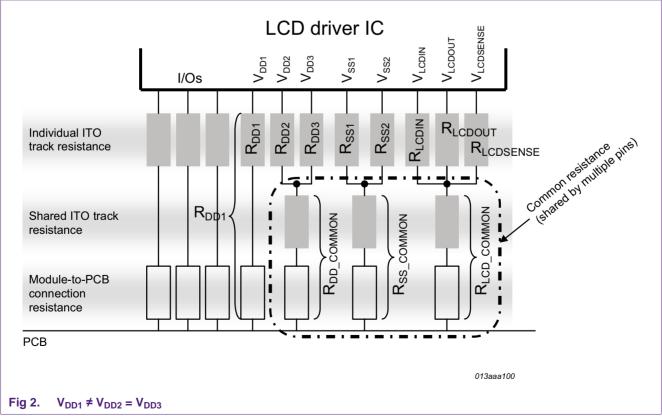

For COG applications, the power supply circuits of NXP LCD driver ICs are separated internally into  $V_{DD1}$ ,  $V_{DD2}$ ,  $V_{DD3}$ ,  $V_{SS1}$ ,  $V_{SS2}$  and sometimes  $V_{SS3}$  supply rails. This allows the module maker to connect these supply circuits using separate ITO tracks. In this way, the common (shared) part of the ITO track is minimized or eliminated. This reduces the amount of common-mode electrical noise.

For similar reasons, the LC drive supply circuits are separated internally into  $V_{LCDIN}$ ,  $V_{LCDOUT}$  and  $V_{LCDSENSE}$ . The shared part of the ITO supply track thus is kept to a minimum.

<u>Figure 1</u> and <u>Figure 2</u> represent the ITO and glass-to-PCB connection paths in two typical configurations. Suggested maximum resistance values of the power supply for a typical small display application (pixel size is in the order of 0.15 mm x 0.15 mm to 0.5 mm x 0.5 mm) are given in <u>Table 1</u>. These limits depend on the display load and have to be revised for each particular application.

Excessive track resistance, especially common (shared) track and connection resistance results in:

- a deterioration of the display quality

- increased power consumption

- incorrect operation.

#### Design guidelines for COG modules with NXP monochrome drivers

## Design guidelines for COG modules with NXP monochrome drivers

Table 1. Maximum ITO track resistance for display drivers

| Resistance path         | Description                                           |            | Maximum resistance ( $\Omega$ ) |

|-------------------------|-------------------------------------------------------|------------|---------------------------------|

| With integrated charg   | e pump                                                |            | 1                               |

| R <sub>DD_COMMON</sub>  | common V <sub>DD</sub> track (including connector)    | <u>[1]</u> | 40                              |

| R <sub>DD1</sub>        | positive logic supply                                 |            | 500                             |

| R <sub>DD2</sub>        | positive charge pump supply                           |            | 200                             |

| R <sub>DD3</sub>        | positive analog supply                                |            | 2000                            |

| R <sub>SS_COMMON</sub>  | common V <sub>SS</sub> track<br>(including connector) | [1]        | 40                              |

| R <sub>SS1</sub>        | negative supply (excluding charge pump)               |            | 80                              |

| R <sub>SS2</sub>        | negative charge pump supply                           |            | 200                             |

| R <sub>LCD_COMMON</sub> | common V <sub>LCD</sub> track (including connector)   | [1]        | 60                              |

| R <sub>LCDOUT</sub>     | generated output V <sub>LCD</sub>                     |            | 100                             |

| R <sub>LCDIN</sub>      | V <sub>LCD</sub> input to chip                        |            | 500                             |

| R <sub>LCDSENSE</sub>   | V <sub>LCD</sub> sense input                          |            | 2000                            |

| Without integrated ch   | arge pump                                             |            | 1                               |

| R <sub>LCD_COMMON</sub> | common V <sub>LCD</sub> track (including connector)   | [1]        | 500                             |

| R <sub>SS_COMMON</sub>  | common V <sub>SS</sub> track<br>(including connector) | [1]        | 150                             |

| R <sub>OSC</sub>        | oscillator select                                     | [2]        | 1000                            |

| R <sub>DD_COMMON</sub>  | common V <sub>DD</sub> track (including connector)    | [1][2]     | 500                             |

| R <sub>CLK</sub>        | clock input and output                                | [2]        | 1000                            |

| R <sub>SCL</sub>        | I <sup>2</sup> C-bus serial clock input               | [2]        | 2000                            |

| R <sub>SDA</sub>        | I <sup>2</sup> C-bus serial data input                | [2][3]     | 2000                            |

| An                      | subaddress inputs                                     | [2]        | 1000                            |

| SAn                     | I <sup>2</sup> C-bus slave address input              | [2]        | 1000                            |

<sup>[1]</sup> Common-mode resistance in supply circuits is the most critical element for optical display performance. It is most effectively minimized by connecting the separate ITO tracks outside of the LCD glass (on PCB, FPC, foil etc.) instead of at the connection point on the glass ledge. However this may not always be practical in the application.

- [2] The ITO track recommendations are valid for both drivers with and without charge pump.

- [3] The values of R<sub>SDA</sub> depend on the external pull-up resistors, see Section 4.

Table 2. SYNC (cascade synchronization input and output) contact resistance

| Number of devices | Maximum resistance ( $\Omega$ ) |

|-------------------|---------------------------------|

| 2                 | 6000                            |

| 3 to 5            | 2200                            |

| 6 to 10           | 1200                            |

| 11 to 16          | 700                             |

## Design guidelines for COG modules with NXP monochrome drivers

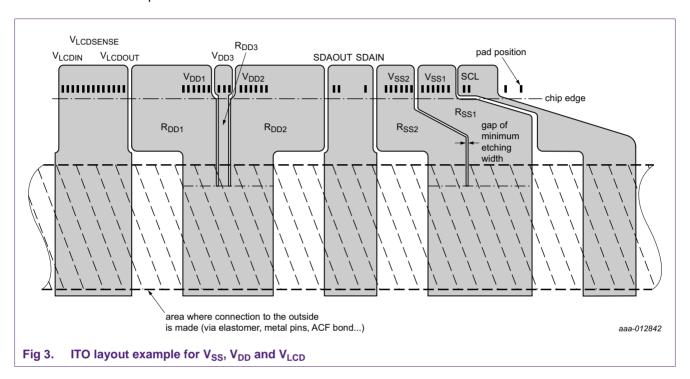

**Remark:** In order to keep the ITO track resistance to a minimum, the pitch and position of the module connection to the outside must be selected such that the power tracks run as straight as possible to the glass edge. In order to minimize common connection resistance use low-ohmic elastomeric connection, metal pin connection or ACF bonded flat cable.

<u>Figure 3</u> shows an example of how the ITO layout for the power supply tracks looks in practice.

## 2.1 Exception to the general rule

The PCF8811 LCD driver uses a slightly different power architecture where the V<sub>LCD</sub> voltage generation is concerned. Because of this, the ITO layout guidelines for connecting pins V<sub>LCDIN</sub>, V<sub>LCDOUT</sub>, V<sub>LCDSENSE</sub> are also different (see <u>Table 3</u>).

Table 3. Exception

| Resistance path         | Description                                         | Maximum resistance (Ω) |

|-------------------------|-----------------------------------------------------|------------------------|

| R <sub>LCD_COMMON</sub> | common V <sub>LCD</sub> track (including connector) | 60                     |

| R <sub>LCDOUT</sub>     | generated output V <sub>LCD</sub>                   | 0[1]                   |

| R <sub>LCDIN</sub>      | V <sub>LCD</sub> input to chip                      | 0[1]                   |

| R <sub>LCDSENSE</sub>   | V <sub>LCD</sub> sense input                        | 0[1]                   |

This means in practice, that V<sub>LCDIN</sub>, V<sub>LCDOUT</sub> and V<sub>LCDSENSE</sub> must be connected together with one thick ITO track.

#### Design guidelines for COG modules with NXP monochrome drivers

## 3. Guidelines for I/O lines

ITO track impedance also affects the AC characteristics of the I/O lines. The ITO track resistance together with any parasitic capacitances adds RC-type delay constants which must be taken into account. NXP recommends that COG modules are not operated close to the limits of the interface timing requirements. Particular attention must be paid to open-drain outputs (see Section 4).

## 4. Guidelines for I<sup>2</sup>C-bus pins SDA and SCL

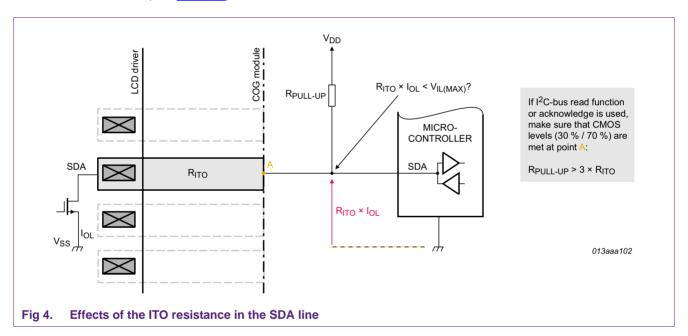

The SDA line in  $I^2C$  devices is an open-drain output and therefore needs an external pull-up resistor. The ITO track resistance,  $R_{ITO}$ , together with the pull-up resistor,  $R_{PULL-UP}$ , forms a potential divider. Because of this, there is danger that the other device(s) on the  $I^2C$ -bus will not see a valid logic LOW when the LCD driver IC drives the SDA line LOW e.g. during the ACKnowledge cycle or during read-back from the IC (see Figure 4).

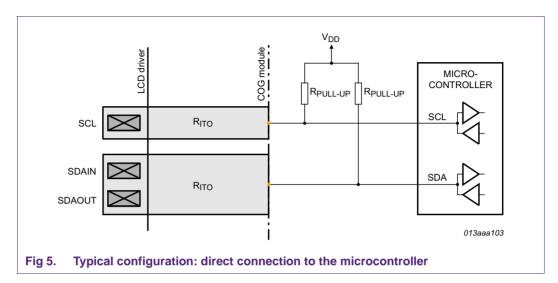

For this reason, the SDA signal in LCD driver ICs is sometimes split into SDAIN and SDAOUT or SDA and SDAACK. A number of possibilities for connecting an LCD driver to the host microcontroller exist, three examples are given.

• The I<sup>2</sup>C protocol is fully implemented in the system, i.e. the master-transmitter device (host microcontroller) expects an ACKnowledge after each byte. In this case connect LCD driver's SDAIN and SDAOUT pins on the glass with a single ITO trace, taking care to minimize track and connection resistance. Choose a pull-up resistor value that will ensure that the V<sub>IL</sub> spec of the other device(s) on the I<sup>2</sup>C-bus is always met, under all conditions and including all tolerances.

Note that the value of  $R_{PULL-UP}$  directly affects the SDA signal rise time. If  $R_{PULL-UP}$  is too high, the maximum rise time limit is violated.

## Design guidelines for COG modules with NXP monochrome drivers

A simple rule in this case is to make sure that (2 x  $C_{SDA}$  x  $R_{PULL-UP)}$  <  $t_{R(max)}$ ), where  $C_{SDA}$  is the capacitance of the SDA bus rail, including the associated parasitic pad capacitances of all the devices connected to the  $I^2C$ -bus and  $t_{R(max)}$  is the specified maximum rise time (see Figure 5).

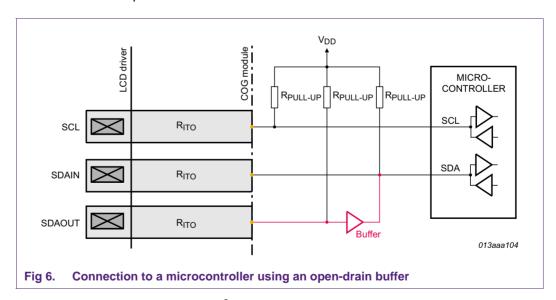

• The I<sup>2</sup>C protocol is fully implemented in the system but the value of the pull-up resistor required to satisfy the maximum logic low-level requirement V<sub>IL</sub>(max) is too high to satisfy simultaneously the maximum rise time requirement, t<sub>R</sub>. In this case, the full SDA signal may be reconstituted using an external open-drain buffer (see <u>Figure 6</u>). The buffer isolates the SDAOUT pin from the capacitance of the I<sup>2</sup>C-bus and makes the rise time requirement easier to meet.

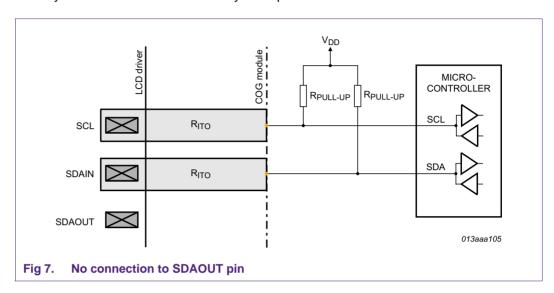

It is possible to implement the I<sup>2</sup>C protocol partially, in a way that ignores the ACKnowledge bit after each byte.

#### Design guidelines for COG modules with NXP monochrome drivers

In this case, the SDAOUT can be left unconnected (see <u>Figure 7</u>). Such a configuration may be desirable because it eliminates the common-mode noise that results from the ACKnowledge current flowing through the common resistance in the V<sub>SS</sub> supply of the driver IC. Note, however, that in this case it is not possible to use any read-back function which may be implemented in the LCD driver IC.

## 5. Guidelines for ESD/EMC protection

## 5.1 Dummy pads

Dummy pads (test or reserve pads) must not be connected to ITO tracks. Connecting dummy pads may compromise the ESD protection of the LCD module because these pads have no ESD protection elements.

## 5.2 Hardware reset pad

In COG applications, the interface and supply lines have a higher impedance compared to COB, TCP, or COF. The resistance of individual lines may differ in value considerably from one ITO track to the next. This difference may be hundreds of ohms. As a result it is possible to generate a large differential voltage across the ITO tracks during an EMC event. The RESET pad recognizes such an EMI-induced voltage spike (of the order of 5 ns) as a reset command. To prevent this, a low-pass filter is built into the RESET pad of the LCD driver ICs.

## 5.3 Power supply tracks V<sub>SS</sub> and V<sub>DD</sub>

To further increase EMC immunity NXP recommends that the resistance of the ITO tracks and connections for the power supply -  $V_{DD1}$ ,  $V_{DD2}$ ,  $V_{DD3}$ ,  $V_{SS1}$ ,  $V_{SS2}$  - must be reduced as much as possible.

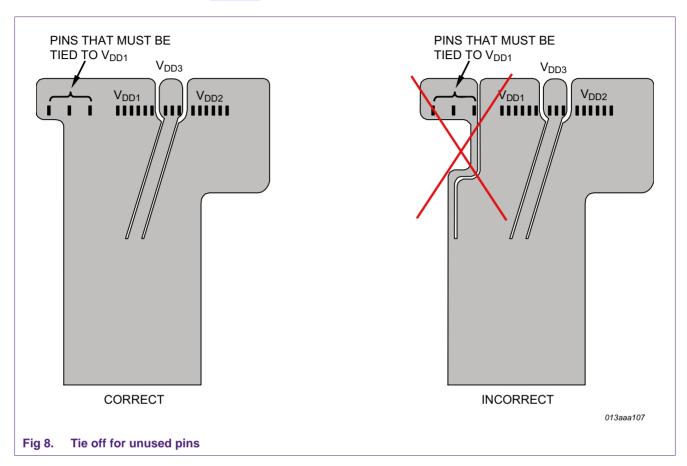

#### 5.4 Unused pins

When pins are not used in the application (e.g. test pins, unused interface pins etc.) it may be a requirement that these pins are tied to  $V_{DD1}$  or  $V_{SS1}$  (tied off). In this case, it is important to make the connection to  $V_{DD1}$  or  $V_{SS1}$  as direct as possible. Sometimes

#### Design guidelines for COG modules with NXP monochrome drivers

so-called tie-off pads are provided for this purpose (called Vxx1 TIEOFF or similar). If there are no tie-off pads, then the connection must be made directly to the  $V_{DD1}$  or  $V_{SS1}$  pads (see Figure 8).

## 6. Hard and soft gold bumps

After conventional IC fabrication, the bonding pads of LCD drivers for COG application are plated with gold bumps, which allow the LCD driver to be bonded directly to contact pads on a flex foil, or on the display glass. Here the chip is mounted upside-down in what is known as 'flip chip' geometry. Gold ball bumping is an evolution of the more than 50 year old gold wire bonding process. Because of the maturity of the wire bonding process, these bump connections are very reliable.

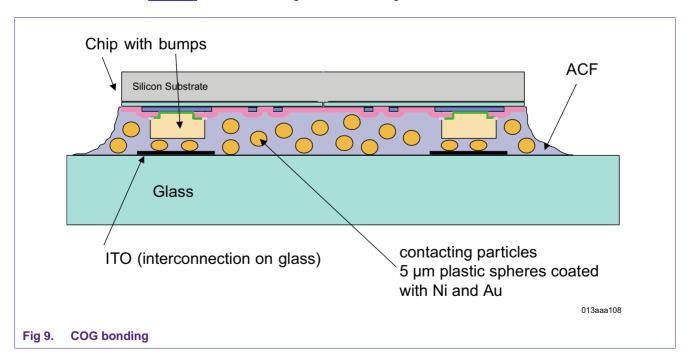

In COG manufacturing, the chips are mounted on a glass substrate. The chip is bonded directly to the conductive ITO tracks on the glass, using Anisotropic Conductive Film (ACF), see Figure 9. ACF is the name given to the combination of the conductive particles, metallic particles (as small as 3  $\mu m$  to 5  $\mu m$ ) or metal-coated polymer balls together with the adhesive resin. ACF is actually a non-conductive film containing dispersed microscopic conductive particles. Anisotropic refers to directionally different properties. The conductive adhesive becomes conductive only in the Z-direction, which is the direction in which it is being compressed during assembly of the COG module. The compressed adhesive is that which is trapped between the bump and the glass. When this is compressed, conductive particles inside the epoxy will align themselves and create a

#### Design guidelines for COG modules with NXP monochrome drivers

conductive path between the die and the ITO tracks. There is no conductive path in the X or Y direction. This is of course also required as it would create a shorting path between the bumps.

Besides bonding to glass, the chip can be bonded to a foil as well (chip on foil, COF).

Gold bumps (also known as studs) can be divided in so called hard and soft bumps. The Au hardness is expressed in HV (Vickers). The border between soft and hard is not a very strict division and there is a small overlap in the definitions that are commonly used in the industry.

Soft bumps: 35 HV - 80 HV

Hard bumps: 60 HV - 120 HV

Whether to use hard or soft bumps depends on the application (assembly process. i.e COG or COF) and sometimes also a bit on user preference.

In general, for COG products, the bumps need to be harder because the harder bumps could bear/brake ACF particles which could be located below the gold bumps. When the bumps are harder, the connection will be established after breaking the ACF particles during the COG manufacturing process. If the bump is soft, it is difficult to bear/break the ACF particles. Experiments have shown that using gold bumps with a hardness of 70 HV leads to a lower contact resistance compared to a 40 HV gold bump. Also the pressure applied to the chip during bonding has an influence on the final contact resistance.

Therefore, with COG the typical hardness used is around 70 HV to 75 HV (50 HV  $\sim$  100 HV or 55 HV  $\sim$  95 HV).

For Chip-on-foil (COF) products, the hardness should be lower due to the assembly process. The typical hardness here is around 50 HV (35 HV ~ 65 HV).

Balls do have a non-conductive polymer layer which gets pushed away when they are trapped between the gold bump and the ITO.

The main reason for wanting hard bumps is that the particles are a kind of "hard" themselves. As a result, the particle will be pushed into the bump in case the bump is soft.

This again results in a larger increase in contact resistance over lifetime, as the particle has less compression when pushed into the bump compared to being squeezed between bump and substrate.

Also bump pitch and bump gap play a role in the choice. With decreasing gaps, this becomes more of an issue. Soft bumps will easily show bump deformation and hence reduction of resulting gap. If it was too small to start with, short circuits may be formed. Usually with hard bumps the gap between bumps needs to be at least three times the diameter of the conductive particles in order to prevent short circuiting. Using soft bumps results in a wider gap being required.

In addition, soft bumps need to be processed by annealing. This is not necessary for hard bumps. Annealing is a heat treatment that alters a material to make it more workable. It involves heating a material to above its critical temperature, maintaining a suitable temperature, and then cooling. It can a.o. soften material, relieve internal stresses, refine the structure by making it homogeneous, and improve cold working properties.

#### Design guidelines for COG modules with NXP monochrome drivers

As a consequence of the above, hard bumps are more widely used than soft bumps in the manufacturing of COG display modules.

## 7. Guidelines for COG mounting

## 7.1 COG bonding conditions

The COG bonding conditions described are based on practical experience within NXP Semiconductors and must be used as a guideline. The COG bonding conditions in each application must be validated using reliability and reproducibility tests. Special care must be taken in analyzing the following parameters after COG bonding to prevent abnormalities:

- · bump height

- bump deformation

- bump roughness

- IC passivation integrity

- uniform ACF particle density.

Special care must be taken in the COG bonding production facility to:

- avoid dust and other alien particles interfering with the COG bonding process

- · avoid ESD overstress during COG bonding.

## 7.2 COG Bonding parameters

Figure 9 shows a drawing of COG bonding with ACF.

The following parameters apply to all COG bonding (Au bumps) processes:

#### Design guidelines for COG modules with NXP monochrome drivers

- bonding pressure as a function of total bump area of the IC: 12 kg / mm<sup>2</sup>

- ACF temperature 220 °C  $\pm$  10 °C.

## 8. Sensitivity to light

Semiconductors are sensitive to light. Any p-n junction, if illuminated, is potentially a photodiode. Semiconductor devices such as transistors and ICs contain p-n junctions, and will not function correctly if they are illuminated by unwanted electromagnetic radiation (light) of a wavelength suitable to produce a photocurrent.

Some LCD drivers contain a One Time Programmable (OTP) memory. UV radiation entering the driver could erase the OTP.

Therefore devices must be shielded against light. If this is not done properly, transistors and ICs can malfunction and will show increased current consumption due to induced photo-currents. In COG applications, the driver IC and the chip-on-glass bonds must therefore be sealed by coating the chip in black epoxy. To prevent light from entering the IC (especially important for backlit displays), a small black sticker is glued on the glass, underneath the driver IC.

**Application note**

#### Design guidelines for COG modules with NXP monochrome drivers

## 9. References

- [1] AN11267 EMC and system level ESD design guidelines for LCD drivers

- [2] AN11494 Cascading NXP LCD segment drivers

- [3] PCA2117 Automotive LCD driver for character displays

- [4] PCF2113x LCD controllers/drivers

- [5] PCF2116x LCD controllers/drivers

- [6] PCF2119x LCD controllers/drivers

- [7] PCF21219 LCD driver for character displays

- [8] PCA85132 LCD driver for low multiplex rates

- [9] PCA85133 Automotive LCD driver for low multiplex rates

- [10] PCA85232 LCD driver for low multiplex rates

- [11] PCA85233 Automotive LCD driver for low multiplex rates

- [12] PCA8538 Automotive 102 x 9 Chip-On-Glass LCD segment driver

- [13] PCA8576D Automotive 40 x 4 LCD segment driver for low multiplex rates

- [14] PCA8576F Automotive LCD driver for low multiplex rates

- [15] PCA9620 60 x 8 LCD high-drive segment driver for automotive and industrial

- [16] PCF85132 LCD driver for low multiplex rates

- [17] PCF85133 Universal LCD driver for low multiplex rates

- [18] PCF8532 Universal LCD driver for low multiplex rates

- [19] PCF8533 Universal LCD driver for low multiplex rates

- [20] PCF8534A Universal LCD driver for low multiplex rates

- [21] PCF8538 Universal 102 x 9 Chip-On-Glass LCD segment driver

- [22] PCF8576C Universal LCD driver for low multiplex rates

- [23] PCF8576D Universal LCD driver for low multiplex rates

- [24] PCF8576E Universal LCD driver for low multiplex rates

- [25] PCF8577C LCD direct/duplex driver with I<sup>2</sup>C-bus interface

- [26] R\_10015 Chip-On-Glass (COG) a cost-effective and reliable technology for LCD displays

- [27] UM10204 I<sup>2</sup>C-bus specification and user manual

#### Design guidelines for COG modules with NXP monochrome drivers

## 10. Legal information

## 10.1 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

## 10.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

#### 10.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

## Design guidelines for COG modules with NXP monochrome drivers

## 11. Tables

| Table 1. | Maximum ITO track resistance for display        |

|----------|-------------------------------------------------|

|          | drivers                                         |

| Table 2. | SYNC (cascade synchronization input and output) |

|          | contact resistance5                             |

| Table 3. | Exception                                       |

## Design guidelines for COG modules with NXP monochrome drivers

## 12. Figures

| Fig 1. | $V_{DD1} = V_{DD2} = V_{DD3} \dots 4$                                           |

|--------|---------------------------------------------------------------------------------|

| Fig 2. | $V_{DD1} \neq V_{DD2} = V_{DD3} \dots 4$                                        |

| Fig 3. | ITO layout example for V <sub>SS</sub> , V <sub>DD</sub> and V <sub>LCD</sub> 6 |

| Fig 4. | Effects of the ITO resistance in the SDA line7                                  |

| Fig 5. | Typical configuration: direct connection to the                                 |

|        | microcontroller                                                                 |

| Fig 6. | Connection to a microcontroller using an open-drain                             |

|        | buffer                                                                          |

| Fig 7. | No connection to SDAOUT pin9                                                    |

| Fig 8. | Tie off for unused pins                                                         |

| Fig 9. | COG bonding12                                                                   |

## Design guidelines for COG modules with NXP monochrome drivers

## 13. Contents

| 1    | Introduction                                                           | 3  |

|------|------------------------------------------------------------------------|----|

| 1.1  | Who should read this application note?                                 | 3  |

| 2    | Guidelines for power supply lines V <sub>SS</sub> , V <sub>DD</sub> an | d  |

|      | V <sub>LCD</sub>                                                       | 3  |

| 2.1  | Exception to the general rule                                          | 6  |

| 3    | Guidelines for I/O lines                                               | 7  |

| 4    | Guidelines for I <sup>2</sup> C-bus pins SDA and SCL                   | 7  |

| 5    | Guidelines for ESD/EMC protection                                      | 9  |

| 5.1  | Dummy pads                                                             |    |

| 5.2  | Hardware reset pad                                                     |    |

| 5.3  | Power supply tracks V <sub>SS</sub> and V <sub>DD</sub>                | 9  |

| 5.4  | Unused pins                                                            | 9  |

| 6    | Hard and soft gold bumps                                               | 10 |

| 7    | Guidelines for COG mounting                                            | 12 |

| 7.1  | COG bonding conditions                                                 | 12 |

| 7.2  | COG Bonding parameters                                                 | 12 |

| 8    | Sensitivity to light                                                   | 13 |

| 9    | References                                                             | 14 |

| 10   | Legal information                                                      | 15 |

| 10.1 |                                                                        | 15 |

| 10.2 | Disclaimers                                                            | 15 |

| 10.3 | Trademarks                                                             | 15 |

| 11   | Tables                                                                 | 16 |

| 12   | Figures                                                                | 17 |

| 13   | Contents                                                               | 18 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.