# CAN SIC Transceiver with Partial Networking, CAN FD Data Rates Up to 8 Mbit/s

# TJA1465

Last Updated: Feb 7, 2025

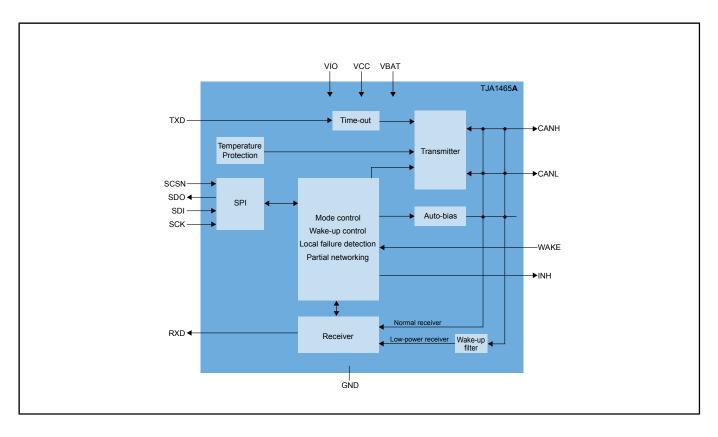

The TJA1465 CAN signal improvement capability (SIC) transceiver with partial networking sleep mode, is part of the TJA146x transceiver family that implements CAN SIC as defined in ISO11898-2:2024 parameter sets A-C. The TJA1465 is fully interoperable with the high-speed classical CAN and CAN FD protocols, and fully developed and certified to be ISO 26262 ASIL-B compliant.

CAN signal improvement significantly reduces signal ringing on a network, allowing reliable CAN FD communication at 5 Mbit/s in larger topologies, and due to a much tighter bit timing symmetry performance even enables CAN FD communication up to 8 Mbit/s.

The TJA1465 supports CAN partial networking by means of selective wake-up functionality as specified in ISO 11898-2:2024, allowing the transceiver to remain in sleep mode even when CAN bus traffic is running, when it is not required to be active.

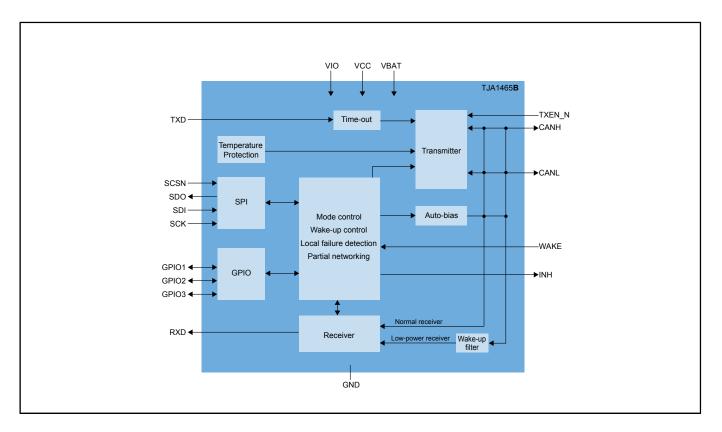

The TJA1465B offers an extended feature set on top of the TJA1465A, including a TXEN\_N pin for disabling the transmitter through an external pin, and three GPIO pins which can be configured to an extended set of functionalities, including, e.g., a second TXD/ RXD channel.

The TJA1465 offers a CAN FD/ CAN XL passive feature, which in sleep mode prevents the transceiver from waking up and shields the CAN controller from CAN FD and CAN XL messages when running a mixed bus communication.

### TJA1465A Block Diagram

## TJA1465B Block Diagram

#### View additional information for CAN SIC Transceiver with Partial Networking, CAN FD Data Rates Up to 8 Mbit/s.

Note: The information on this document is subject to change without notice.

#### www.nxp.com

NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2025 NXP B.V.