## S32K3 Automotive Telematics Box (T-Box) Reference Design Board

S32K3-T-BOX

Last Updated: Dec 6, 2024

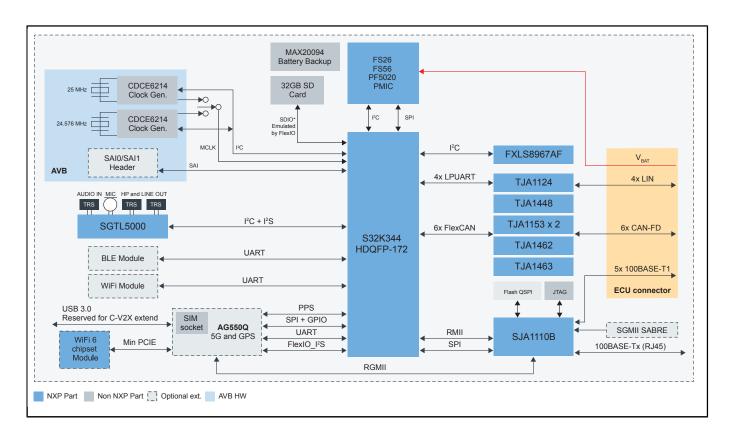

The S32K3 Automotive Telematics Box (T-BOX) is a compact, highly-optimized reference design board engineered to develop cost-effective vehicle networking and telematics applications.

Based on the S32K344 MCU with lockstep Arm® Cortex®-M7, the S32K3-T-BOX provides a reference for automotive applications such as 5G telematics box plus gateway and automotive Ethernet AVB with remote diagnostic, low-predictable latency, TSN Ethernet support and a wealth of communication interfaces (CAN FD/LIN/Ethernet/SJA1110). It can be directly used by carmakers, suppliers and software ecosystem partners to accelerate the development and shorten time-to-market.

## S32K3 Telematics Box (T-Box) Reference Design Board Block Diagram

S32K3 Family Overview Block Diagram

| K311                                                     | K312       | K314                         | Common<br>Features                                                                                      | K322                      | K324                     | K341                           | K342                     | K344                     | K328                              | K338                       | K348                        | K358                                    |

|----------------------------------------------------------|------------|------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------|--------------------------|--------------------------------|--------------------------|--------------------------|-----------------------------------|----------------------------|-----------------------------|-----------------------------------------|

| 1 x Arm <sup>o</sup> Cortex <sup>o</sup> -M7<br>@120 MHz |            | 1x Cortex-M7<br>@240 MHz     | AEC-Q100, 125 °C, 3,3/5 V                                                                               | 2 x Cortex-M7 @240 MHz    |                          | 1 Lockstep Cortex-M7 @ 240 MHz |                          |                          | 2 x Cortex-M7<br>@ 240 MHz        | 3 x Cortex-M7<br>@ 240 MHz | 1 LS Cortex-M7<br>@ 240 MHz | 1 LS Cortex-I<br>1 Cortex-N<br>@ 240 MH |

| 1 MB Flash 2 MB Flash                                    |            | 4 MB Flash                   | HSE-B<br>Crypto Security Engine                                                                         | 2 MB Flash                | 4 MB Flash               | 1 MB Flash                     | 2 MB Flash               | 4 MB Flash               |                                   | 8 MB                       | Flash                       |                                         |

| 128 K SRAM                                               | 192 K SRAM | 512 K SRAM                   | FOTA<br>(Firmware Over-the-Air)                                                                         | 256 k SRAM                | 512 k SRAM               | 256 k SRAM                     | 256 k SRAM               | 512 k SRAM               | 1152 KB SRAM                      | 1152 KB SRAM               | 1152 KB SRAM                | 1152 KB SR                              |

| up to 84 I/Os up to 143 I/Os                             |            | up to 218 I/Os               | Low Power Constitu                                                                                      | up to 143 I/Os            | up to 218 I/Os           | up to 143 I/Os                 | up to 143 I/Os           | up to 218 I/Os           | up to 218 I/Os                    |                            |                             |                                         |

| 16-ch. eDMA                                              |            | 32-ch. eDMA                  | Low-Power Operating<br>Modes and Peripherals<br>(LP UART, FlexIO)                                       |                           |                          | 32-ch. eDMA                    |                          |                          |                                   | 32-ch.                     |                             |                                         |

| 3 x CAN 6 x CAI<br>(3 x FD) 6 x CAI                      |            | N (6 x FD)                   | ASIL B/D Safety:<br>(ECC Memories, MPU,<br>CRC, Watchdogs)                                              | 4 x CAN<br>(4 x FD)       | 6 x CAN<br>(6 x FD)      | 4 x CAN<br>(4 x FD)            | 4 x CAN<br>(4 x FD)      | 6 x CAN<br>(6 x FD)      | 8 x CAN<br>(8 x FD)               | 8 x CAN<br>(8 x FD)        | 8 x CAN<br>(8 x FD)         | 8 x CAN<br>(8 x FD)                     |

|                                                          |            | 100 Mbit/s<br>Ethernet (TSN) |                                                                                                         | 100 Mbit/s Ethernet (TSN) |                          |                                |                          |                          | 1 Gbit/s Ethernet (TSN)           |                            |                             |                                         |

| 2 x FC 2 x FC                                            |            | 2 x FC                       | eMIOS Timers, Analogue<br>Comparator, Logic Control<br>Unit, Body Cross Triggering<br>Unit, Trigger Mux | 2 x FC                    | 2 x FC                   | 2 x FC                         | 2 x FC                   | 2×I <sup>2</sup> C       | 2×FC                              |                            |                             |                                         |

| 4 x SPI*                                                 |            | 6 x SP <b>I</b> *            |                                                                                                         | 4 x SP <b>I*</b>          | 6 x SPI*                 | 4 x SP <b>I</b> *              | 4 x SP <b>I*</b>         | 6 x SP <b>I*</b>         | 6 x SPI*                          |                            |                             |                                         |

| 2 x 24-ch.<br>12-bit ADC                                 |            | 3 x 24-ch.<br>12-bit ADC     |                                                                                                         | 2 x 24-ch.<br>12-bit ADC  | 3 x 24-ch.<br>12-bit ADC | 2 x 24-ch.<br>12-bit ADC       | 2 x 24-ch.<br>12-bit ADC | 3 x 24-ch.<br>12-bit ADC | 3 x 24-ch.<br>12-bit ADC          |                            |                             |                                         |

|                                                          |            | 2 x SAI (I²S)                | JTAG<br>S32 Design Studio IDE                                                                           | 2 x SAI (FS)              |                          |                                |                          | 2 x SAI (FS)             |                                   |                            |                             |                                         |

| LQFP-48 HDQFP-17                                         |            | Quad SPI                     |                                                                                                         |                           |                          | Quad SPI HDQFP-172             |                          |                          | Quad SPI + SDHC (SDIO)  HDQFP-172 |                            |                             |                                         |

| HDQFP-100                                                |            | FP-172                       | Real-Time Drivers<br>(AUTOSAR® and<br>Non-AUTOSAR)                                                      | HDQFP-100                 |                          | HDQFP-100                      | HDQFP-100                |                          |                                   |                            |                             |                                         |

|                                                          |            | MAPBGA-257                   | Security F/W Safety<br>Software Framework                                                               | MAPBGA-257                |                          |                                |                          | MAPBGA-257               |                                   | MAPB                       | GA-289                      |                                         |

|                                                          |            |                              | Application Software                                                                                    |                           |                          |                                |                          |                          |                                   |                            |                             |                                         |

View additional information for S32K3 Automotive Telematics Box (T-Box) Reference Design Board.

Note: The information on this document is subject to change without notice.

## www.nxp.com

NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2025 NXP B.V.