## 18 V Tolerant SPI 16-Bit/8-Bit GPI with INT

## PCA9701\_PCA9702

Last Updated: Dec 15, 2024

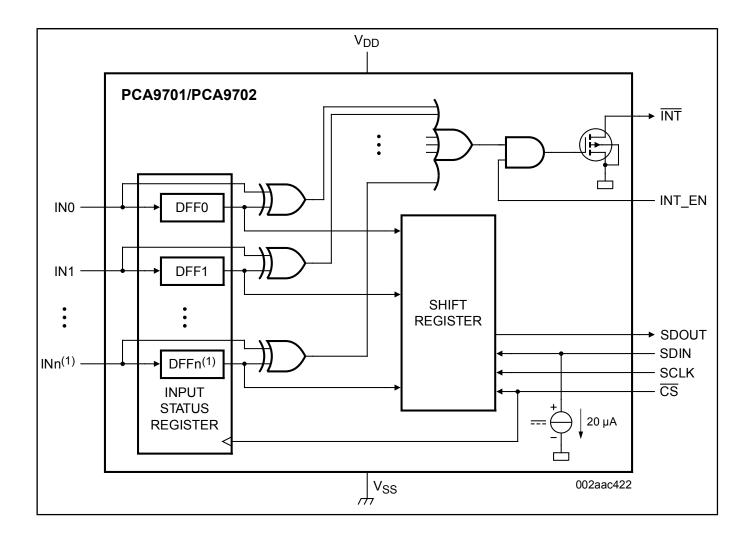

The PCA9701/PCA9702 are low power 18 V tolerant SPI General Purpose Input (GPI) shift register designed to monitor the status of switch inputs. It generates an interrupt when one or more of the switch inputs change state. The input level is recognized as a HIGH when it is greater than 0.7 x VDD and as a LOW when it is less than 0.4 x VDD (minimum threshold of 2 V at 5 V node). The PCA9701 can monitor up to 16 switch inputs and the PCA9702 can monitor up to 8 switch inputs.

The falling edge of the CS pin samples the input port status and clears the interrupt. When CS is LOW, the rising edge of the SCLK loads the shift register and shifts the value out of the shift register. The serial input is sampled on the falling edge of SCLK.

Each of the input ports has a 18 V breakdown ESD protection circuit. When used with a series resistor (minimum 100 k $\Omega$ ), the input can connect to a 12 V battery and support double battery, reverse battery, 27 V jump start and 40 V load dump conditions in automotive applications. Higher voltages can be tolerated on the inputs depending on the series resistor used to limit the input current.

With both the high breakdown voltage and high ESD, these devices are useful for both automotive and mobile applications.

The PCA9703/PCA9704 are new pin compatible devices for the PCA9701/PCA9702 which have an interrupt masking feature allowing selected inputs to not generate interrupts and provides higher ground offset of 0.55 x VDD (minimum of 2.5 V at 5 V node) with minimum hysteresis of 0.05 x VDD (minimum of 225 mV at 5 V node).

View additional information for 18 V Tolerant SPI 16-Bit/8-Bit GPI with INT.

Note: The information on this document is subject to change without notice.

## www.nxp.com

NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2025 NXP B.V.