## **Dual Bidirectional Bus Buffer**

## **PCA9601**

Last Updated: Dec 15, 2024

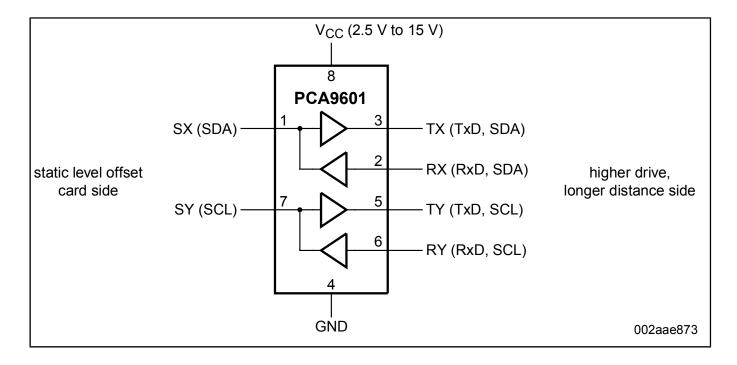

The PCA9601 is designed to isolate I<sup>2</sup>C-bus capacitance, allowing long buses to be driven in point-to-point or multipoint applications of up to 4000 pF. The PCA9601 is a higher-speed version of the P82B96 and a higher drive version of the PCA9600 that allows many more Fast-mode Plus (Fm+) targets on remote daughter cards in applications with temperature range of 0 °C to 85 °C.

It creates a non-latching, bidirectional, logic interface between a normal I<sup>2</sup>C-bus and a range of other higher capacitance or different voltage bus configurations. It can operate at speeds up to at least 1 MHz, and the high drive side is compatible with the Fast-mode Plus specifications.

The PCA9601 features temperature-stabilized logic voltage levels at its SX/SY interface making it suitable for interfacing with buses that have non I<sup>2</sup>C-bus-compliant logic levels such as SMBus, PMBus, or with microprocessors that use those same TTL logic levels.

15 mA drive capability over 0 °C to 85 °C at SX/SY allows driving a 5 V Fm+ bus with 470 pF loading.

The separation of the bidirectional I<sup>2</sup>C-bus signals into unidirectional TX and RX signals enables the SDA and SCL signals to be transmitted via balanced transmission lines (twisted pairs), or with galvanic isolation using opto or magnetic coupling. The TX and RX signals may be connected together to provide a normal bidirectional signal.

## PCA9601 Block Diagram Block Diagram

View additional information for Dual Bidirectional Bus Buffer.

Note: The information on this document is subject to change without notice.

## www.nxp.com

NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2025 NXP B.V.