# QorlQ<sup>®</sup> P5020 and P5010 64bit Dual- and Single-Core Communications Processors

## P5020

#### **Not Recommended for New Designs**

This page contains information on a product that is not recommended for new designs.

Last Updated: Dec 16, 2024

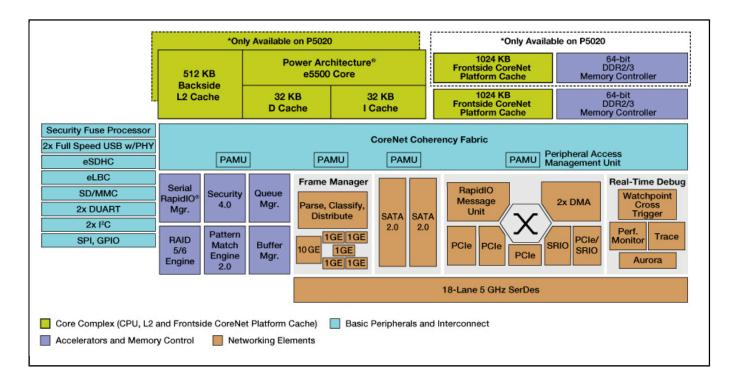

The dual-core P5020 and single-core P5010 processors deliver 64-bit processing, based on the e5500 core built on Power Architecture® technology. With frequencies scalable to 2.0 GHz, large caches and high per-cycle efficiency, these products target control plane and computer applications that require high single-threaded performance.

The P5 platform leverages architectural features pioneered in the P4 platform, including the three-level cache hierarchy for low latencies, hardware hypervisor for robust virtualization support, data path acceleration architecture (DPAA) for offloading packet handling tasks from the core and the CoreNet® switch fabric that eliminates internal bottlenecks. This enables architectural compatibility from the P5 platform to the P4 platform as well as to the P3 platform.

### P5020 BD Block Diagram

View additional information for QorlQ® P5020 and P5010 64-bit Dual- and Single-Core Communications Processors.

Note: The information on this document is subject to change without notice.

#### www.nxp.com

NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2025 NXP B.V.