# Single-chip 16/32-bit microcontrollers; 64/128/256 kB ISP/IAP flash with 10-bit ADC and CAN

## LPC2129FBD64

#### Not Recommended for New Designs

This page contains information on a product that is not recommended for new designs.

Last Updated: Apr 8, 2022

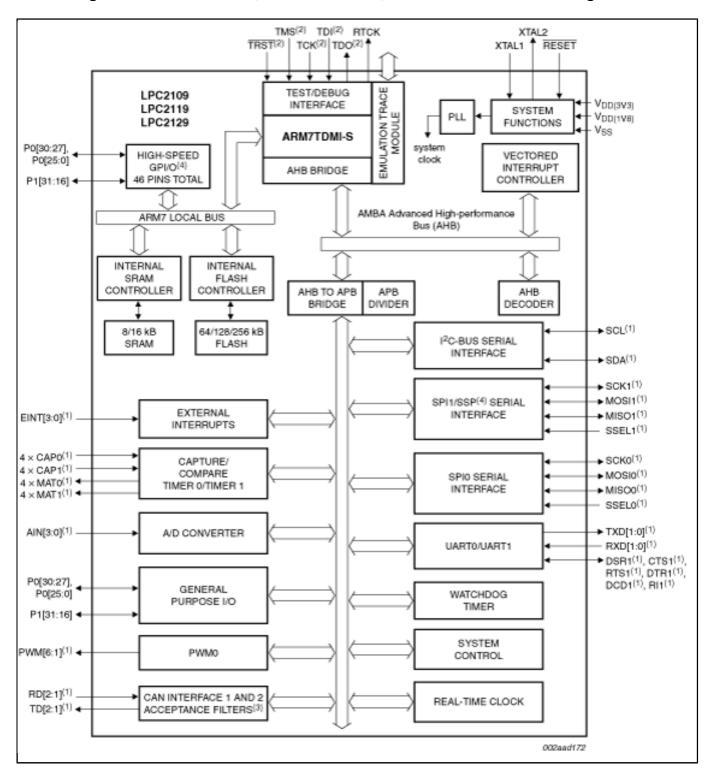

The LPC2109/2119/2129 are based on a 16/32-bit Arm7TDMI-S<sup>™</sup> CPU with real-time emulation and embedded trace support, together with 64/128/256 kB of embedded high-speed flash memory. A 128-bit wide memory interface and a accelerator architecture enable 32-bit code execution at maximum clock rate. For critical code size applications, the alternative 16-bit Thumb mode reduces code by more than 30 % with minimal performance penalty.

With their compact 64-pin package, low power consumption, various 32-bit timers, 4-channel 10-bit ADC, two advanced CAN channels, PWM channels and 46 fast GPIO lines with up to nine external interrupt pins these microcontrollers are particularly suitable for automotive and industrial control applications, as well as medical systems and fault-tolerant maintenance buses. With a wide range of additional serial communications interfaces, they are also suited for communication gateways and protocol converters as well as many other general-purpose applications.

Remark: Throughout the data sheet, the term LPC2109/2119/2129 will apply to devices with and without the /00 or /01 suffixes. The /00 or the /01 suffix will be used to differentiate from other devices only when necessary.

### Block diagram: LPC2109FBD64, LPC2119FBD64, LPC2129FBD64 Block Diagram

View additional information for Single-chip 16/32-bit microcontrollers; 64/128/256 kB ISP/IAP flash with 10-bit ADC and CAN.

Note: The information on this document is subject to change without notice.

www.nxp.com NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2025 NXP B.V.