# AN5384

# Implementation of IEEE Standard 1149.6<sup>TM</sup> on QorlQ LS1088A Processor

Rev. 0 — 19 May 2022 Application Note

## 1 Introduction

This document describes how to implement the IEEE standard 1149.6 $^{^{\text{TM}}}$  on NXPs QorIQ LS1088A processor.

The IEEE standard 1149.6 fully complies with the existing IEEE standard 1149.1. Still, it also requires the following new and mandatory public JTAG instructions that are supported by the NXPs SerDes implementation on the LS1088A processor:

- EXTEST\_PULSE

- EXTEST TRAIN

To provide an implementation of the IEEE standard 1149.6, NXP offers an additional custom public JTAG instruction, INIT\_SETUP.

The INIT\_SETUP instruction is similar, but not identical to the INITIALIZE instruction described in the *IEEE standard 1149.6*, *Annex E*. Although, here the references are made to the two of the IEEE 1149.6 mandatory instructions, EXTEST\_PULSE and EXTEST\_TRAIN. But, the primary focus is on the INIT\_SETUP instruction.

On the LS1088A, the pins listed in Table 7 are defined as IEEE 1149.6 advanced I/O pins. All other I/O pins are defined as standard I/O and comply only with IEEE 1149.1.

#### Contents

| 1        | Introduction                 |      |

|----------|------------------------------|------|

| 2        | Mandatory IEEE 1149.6 public |      |

|          | instructions                 | 1    |

| 2.1      | EXTEST_PULSE                 | 1    |

| 2.2      | EXTEST_TRAIN                 | 2    |

| 3        | INIT_SETUP instruction       | 3    |

| 3.1      | INIT_SETUP and JTAG TAP      | ,    |

|          | state machine                | 3    |

| 3.2      | JTAG opcodes                 | 4    |

| 3.3      | Test Data Register           | 4    |

| 3.3.1    | TDR global configuration     | 4    |

| 3.3.2    | TDR SerDes lane protocol     |      |

|          | configuration                | 5    |

| 3.3.3    | TDR SerDes reference clock   |      |

|          | configuration                | 6    |

| 3.3.4    | Full TDR layout              | 6    |

| 3.4      | BSDL file                    |      |

| 4        | IEEE 1149.6 compliant pins   | 34   |

| 4.1      | Compliance pins              | .35  |

| 4.2      | Unsupported USB pins         | .35  |

| 4.3      | USB reset counter            | .35  |

| 5        | Revision history             | . 36 |

| Legal in | formation                    |      |

#### NOTE

This document is not intended to serve as an introduction to IEEE 1149.6 or its motivations. For a thorough description of testing AC coupled differential nets, see 1149.6 -2003, IEEE Standard for Boundary-Scan Testing of Advanced Digital Networks.

When USB is not in use and all USB power supplies connect to GND, the JTAG IEEE Std 1149.6 Boundary Scan Register (BSR) does not shift data between TDI and TDO. To shift USB BSR cells, power on the USB\_SVDD. Here, the USB boundary cells cannot observe or control USB pins, affecting the USB BSR cells during EXTEST, EXTEST\_PULSE, EXTEST\_TRAIN, CLAMP, and SAMPLE. The only fails are related to USB IOs when USB\_SVDD is powered on and USB\_SDVDD and USB\_HVDD are powered off. If all USB power supplies connect to GND, the other 1149.1 JTAG or DAP debug instructions still operate.

## 2 Mandatory IEEE 1149.6 public instructions

The SerDes JTAG logic on the LS1088A fully complies with the two mandatory IEEE 1149.6 instructions, EXTEST\_PULSE and EXTEST\_TRAIN. See 1149.6 ™-2003, IEEE Standard for Boundary-Scan Testing of Advanced Digital Networks for a thorough description of these specific instructions.

## 2.1 EXTEST\_PULSE

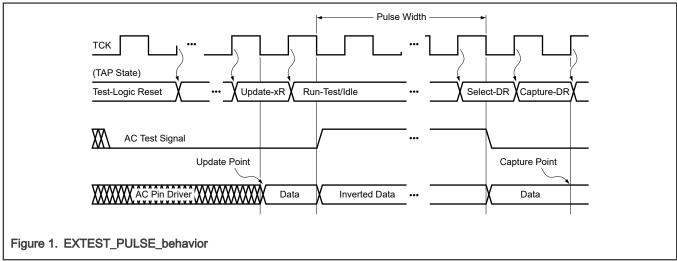

According to the *IEEE 1149.6*<sup>™</sup>-2003, Section 5.3, EXTEST\_PULSE is a mandatory instruction. It becomes effective at the falling edge of TCK in the UpdateIR TAP controller state. The Boundary Scan Register (BSR) is placed between the Test-Data Input (TDI)

and Test-Data Output (TDO) in a manner similar to the IEEE 1149.1 EXTEST instruction. The timing diagram from the official IEEE 1149.6 document is depicted in Figure 1.

A high-level description of behavior during the EXTEST\_PULSE instruction is as follows:

- Normal DC pins behave in the same manner as the EXTEST instruction

- Select AC Behavior for each differential SerDes TX/TX\_B pin pair and enable the driver. This condition then drives the logic value in the BSR on the pin pair onto the pins at the falling edge of Test Clock (TCK) in the UpdateIR or UpdateDR states. When Run-Test/Idle is entered, the differential pin drives the inverted data signal starting at the falling edge of TCK. The differential pin drivers transition back to the original, non-inverted state at the falling edge of TCK when Run-Test/Idle state is exited, as shown in Figure 1 on the AC pin driver signals. This event generates a pulse of inverted data on a driver that is as wide as the time spent in the Run-Test/Idle TAP controller state.

- If the Run-Test/Idle TAP controller state is not entered, the output behavior of the SerDes TX pins is not distinguishable from the (DC) EXTEST instruction.

- If AC Behavior is not selected, then each differential SerDes TX/TX\_B pin behaves the same as with the EXTEST instruction.

- The SerDes RX/RX\_B pins are equipped with test receivers. The differential SerDes channels have one test receiver per leg.

When either the EXTEST\_PULSE or EXTEST\_TRAIN instructions are in effect, it is the responsibility of the test receiver to

reconstruct the test waveform driven by the upstream driver when either AC-coupling or DC-coupling is used. It does so by

reacting to the edges and not the levels of the input waveform. When (DC) EXTEST is in effect, the test receiver behaves as

a level detector.

For a thorough description of this instruction, see *1149.6*<sup>™</sup>-2003, IEEE Standard for Boundary-Scan Testing of Advanced Digital Networks.

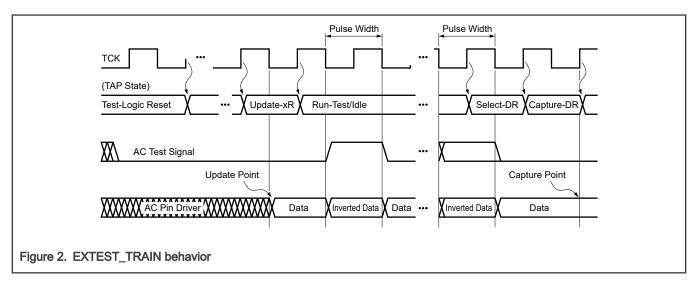

#### 2.2 EXTEST\_TRAIN

EXTEST\_TRAIN is a mandatory instruction according to the *IEEE 1149.6* <sup>™</sup> *Section 5.4*. It becomes effective at the falling edge of TCK in the UpdateIR TAP controller state. The boundary register is placed between TDI and TDO, similar to the IEEE 1149.1 EXTEST instruction. The timing diagram from the official IEEE 1149.6 document is depicted in Figure 2.

Implementation of IEEE Standard 1149.6<sup>TM</sup> on QorlQ LS1088A Processor, Rev. 0, 19 May 2022

EXTEST\_TRAIN is similar to EXTEST\_PULSE except in AC Behavior mode. It enables SerDes TX/TX\_B pins to toggle between inverted BSR and non-inverted BSR states for each falling edge of TCK while remaining in the Run-Test/Idle state. This process is shown in the Figure 2 on the AC pin driver signals.

For a thorough description of these instructions, see  $1149.6^{\text{TM}}$ -2003, IEEE Standard for Boundary-Scan Testing of Advanced Digital Networks.

## 3 INIT SETUP instruction

The SerDes channels on the LS1088A are configurable to support the signaling levels required for different interface protocols. To ensure correct electrical behavior, the LS1088A provides the INIT\_SETUP instruction and an associated Test Data Register (TDR). These two components allow for the correct configuration of the SerDes pins based on the board configuration where an IEEE 1149.6<sup>™</sup> compliant board interconnect test would be applied.

The INIT\_SETUP instruction is a custom public JTAG instruction. It is similar to, yet different from, the INITIALIZE instruction discussed in *IEEE 1149.6*, *ANNEX E*. This instruction is used to preconfigure the electrical parameters of the SerDes RX receivers and TX transmitters to support testing across multiple electrical or physical protocols. Few combinations of signaling levels used by an LS1088A SerDes channel at a given time can potentially be incompatible with SerDes channel signaling of another part on the board. This incompatibility happens due to the difference between the signaling levels of the different protocols. This necessitated the creation of a new instruction to set up the proper voltage levels for the desired protocol during the testing process.

The INIT\_SETUP instruction places the TDR between TDI and TDO of the SoC. The proper I/O configuration is shifted-in to set up the correct voltage levels for a given SerDes protocol on a per TX or RX channel basis. Most industrial JTAG board-level interconnect tools support the use of such an instruction to handle multiple physical protocols over a high-speed serial interface.

The INIT\_SETUP instruction should be executed as a "preamble" instruction when needed, prior to the execution of other IEEE 1149.1 or IEEE 1149.6 instructions that control the SerDes pins. These instructions are EXTEST, EXTEST\_PULSE, EXTEST\_TRAIN, and CLAMP. The other IEEE 1149.1-supported instructions (BYPASS, IDCODE, and PRELOAD) always run correctly without the use of the INIT\_SETUP instruction.

The SAMPLE instruction is a special case. The INIT\_SETUP TDR per-channel settings do not apply during SAMPLE by default, but they are in effect on the TX/TX\_B pairs and RX/RX\_B pairs if the TDR[sd\_sample\_override] bit is set. For more information, see the Full TDR layout.

#### 3.1 INIT\_SETUP and JTAG TAP state machine

As with prior JTAG implementations, there are two independent sets of controls over the electrical behavior of the SerDes RX and TX analog circuits. The first is the normal, functional "mission" mode, which is how the SerDes lanes are configured in actual production use. The second is JTAG 1149.1/1149.6 test mode where JTAG instructions take priority and control the SerDes RX/TX configurations when the EXTEST instructions are being executed.

Application Note 3 / 39

When INIT\_SETUP is the active instruction, the bits of a new TDR are not clocked during the CaptureDR JTAG state. During Shift-DR, the TDR is placed between TDI and TDO of the SoC. The bits shift through the ports of the functional flip-flops of each SerDes lane to load the desired INIT\_SETUP data.

NOTE

During the TestLogicReset state or TRST\_B assertion, the INIT\_SETUP TDR is reset to a default condition (all zeros). The default protocol is PCI Express for SerDes lanes and the SATA-equivalent 200 mV levels for the PLL reference clock lanes, until changed by a subsequent Shift-DR of the INIT\_SETUP instruction. There is no action taken during other states of the TAP state machine or during other instructions. When configured, the settings remain undisturbed until either TSRT\_B is asserted, the Test Logic Reset State is entered, or the TDR is changed by another Shift-DR of the INIT\_SETUP instruction.

#### 3.2 JTAG opcodes

The new IEEE 1149.6<sup>™</sup> JTAG opcodes, as defined in the BSDL file, are shown in Table 1.

Table 1. JTAG 1149.6 public opcodes

| JTAG mnemonic | Category         | Opcode   |      |

|---------------|------------------|----------|------|

|               |                  | Binary   | Hex  |

| EXTEST_PULSE  | Public mandatory | 11110101 | 0xF5 |

| EXTEST_TRAIN  |                  | 11110110 | 0xF6 |

| INIT_SETUP    | Public custom    | 11010000 | 0xD0 |

## 3.3 Test Data Register

The TDR is implemented as a serial scan chain. The TDR, described in Table 5, consists of 456 bits. Non-reserved bits contain the bit fields which must configure the platform of SerDes logic for the IEEE 1149.6<sup>™</sup> operation. Reserved bits must be set to 0. Behavior is not guaranteed for non-zero settings of reserved bits. Bit 0 connects to TDO, and bit 405 connects to TDI during INIT\_SETUP Shift-DR.

#### 3.3.1 TDR global configuration

The TDR has two global configuration bits that apply to all lanes and five individual control bits for each lane. The global configuration bits are TDR[DDR\_vsel\_override], TDR[jtag\_xpad\_lo\_volt\_sel], and TDR[jtag\_sample\_override], as follows:

- TDR[DDR\_vsel\_override] determines the DDR G1VDD voltage level, which is 1.2 V or 1.35 V. See the *LS1088A QorIQ Integrated Processor Hardware Specifications* for the specific voltage ranges.

- TDR[jtag\_xpad\_lo\_volt\_sel] is fixed to select SerDes XVDD voltage level to 1.35 V. See the LS1088A QorlQ Integrated Processor Hardware Specifications for the specific voltage ranges.

- TDR[jtag\_sample\_override] indicates whether explicit protocol control should be employed during the execution of the SAMPLE instruction to override the mission protocol configuration for the purposes of running a test scenario.

Application Note 4 / 39

#### NOTE

The advanced I/O pins are compliant with the IEEE 1149.6<sup>™</sup> except that there are limitations placed on SAMPLE. These limitations are due to the inherent practical issues associated with capturing the value of gigabit signaling of the slow and asynchronous TCK at the IEEE 1149.6 test receivers across the externally AC-coupled interfaces.

When the TDR[jtag\_sample\_override] bit is set, the SD1\_RXn capture values on the pins during SAMPLE. Unless the value driven is slow or static, the value cannot be predicted. If the lanes are running at a selected protocol frequency, the use of SAMPLE can affect the signal integrity of the functional data transmissions.

When the TDR[jtag\_sample\_override] bit is set, the SerDes receive and transmit signals using an internal DC-coupled sample configuration based on electrical settings from the TDR register. When the TDR[jtag\_sample\_override] bit is not set, the SerDes receive and transmit signals using an internal AC-coupled sample configuration based on their normal electrical settings from the functional mission logic during SAMPLE.

An inherent limitation for SAMPLE is that the IEEE 1149.6 test receivers reject high-speed signals as high-frequency 'noise'. Hence, the protocol data rate must be slow enough to pass through this glitch rejection filtering. In addition, it must be fast enough not to decay below the threshold of the test receivers due to the presence of external AC-coupling at the external interface.

#### 3.3.2 TDR SerDes lane protocol configuration

There is a TDR bit field composed of five bits for each lane, shown in the Figure 3. This field is further subdivided into two subfields. The first three bits [4:2] specify the configuration for the RX protocol. The final two bits [1:0] specify the configuration of the TX protocol for the same lane. Fully mapped bit field decode values for configuring the RX and TX protocols are defined in Table 2 and Table 3.

| 90                       | 89  | 88 | 87 | 86 |        | 75       | 74       | 73 | 72 | 71 |

|--------------------------|-----|----|----|----|--------|----------|----------|----|----|----|

| SerDes 1 lane A initdata |     |    |    |    | SerDes | 1 lane D | initdata |    |    |    |

|                          | RX  |    | TX |    | +      |          | RX       |    | Т  | X  |

|                          | IVA |    |    | ^  |        |          |          |    |    |    |

Figure 3. SerDes INIT\_SETUP TDR fields for RX and TX

The first three bits specify the decode values for the RX protocol, shown in Table 2.

Table 2. RX configuration protocol decode

| RX protocols                                                | INIT_SETUP settings |

|-------------------------------------------------------------|---------------------|

| PEX3, PEX2, PEX, 1000BaseKX                                 | 000                 |

| Reserved                                                    | 001                 |

| SRIO Short, SGMII 2.5x, QSGMII, JEDEC, SATA, XFI, 10GBaseKR | 010                 |

| SGMII                                                       | 011                 |

| Reserved                                                    | 1xx                 |

The final two bits specify the decode values for the TX protocol, shown in Table 3.

Table 3. TX configuration protocol decode

| TX protocols                                                               | INIT_SETUP settings |

|----------------------------------------------------------------------------|---------------------|

| PEX3, PEX2, PEX, SGMII 2.5x, HiGig, 10GBaseKR, 1000BaseKX (1.0*full swing) | 00                  |

| SRIO Short, QSGMII, JEDEC (0.75*full swing)                                | 01                  |

Table continues on the next page...

Application Note 5/39

Table 3. TX configuration protocol decode (continued)

| TX protocols                                                          | INIT_SETUP settings |

|-----------------------------------------------------------------------|---------------------|

| SATA, Interlaken 10G, Interlaken Short, JEDEC, XFI (0.585*full swing) | 10                  |

| SGMII, JDEC (0.667*full swing)                                        | 11                  |

The RX and TX settings of a given lane are independent of the settings of all other lanes and also of each other. It is up to the user to program both RX and TX to the same protocol values.

#### 3.3.3 TDR SerDes reference clock configuration

The setting of the configuration bits for the reference clock receivers for SerDes bank is specified in TDR[pll1\_config] and TDR[pll2\_config] as described in Figure 4 and Table 4.

The final two bits are cleared (set to zero) for the two SerDes reference clock settings because there are no associated TX/TX\_B pins.

| SerDes bank b |          |       |      |   |  |  |  |

|---------------|----------|-------|------|---|--|--|--|

| R             | ef Clock | Clea  | ared |   |  |  |  |

| Bit 4         | Bit 3    | Bit 2 | 0    | 0 |  |  |  |

Figure 4. SerDes INIT\_SETUP TDR fields for ref clocks

Table 4 shows the decode values for the reference clocks for SerDes banks.

Table 4. SerDes bank reference clock decode values

| Reference clock configuration                                                                    | INIT_SETUP settings<br>PLL1/2 initdata[4:2] | INIT_SETUP settings<br>PLL1/2 initdata[1:0] |

|--------------------------------------------------------------------------------------------------|---------------------------------------------|---------------------------------------------|

| Reference Clock 400 mV min, shunts on-chip AC coupling, used when board is externally AC-Coupled | 000                                         | 00 Reserved                                 |

| Reference Clock 200 mV min, shunts on-chip AC coupling, used when board is externally AC-Coupled | 010                                         | 00 Reserved                                 |

| Reference Clock 400 mV min, on-chip AC coupling, used when board is externally DC-Coupled        | 100                                         | 00 Reserved                                 |

| Reference Clock 200 mV min, on-chip AC coupling, used when board is externally DC-Coupled        | 110                                         | 00 Reserved                                 |

| All other values are reserved                                                                    | -                                           | 00 Reserved                                 |

## 3.3.4 Full TDR layout

It is recommended to use the standard INIT\_SETUP instruction before doing any testing in Boundary SCAN. It is mandatory to use INIT\_SETUP for any checking of IO pad.

Table 5 lists the format of the entire TDR and the contents of each field.

Table 5. TDR layout

| Block | INIT_S ETUP/ TDR Bit | Description     | Default |                                            | Note |

|-------|----------------------|-----------------|---------|--------------------------------------------|------|

|       | 455                  | ref_ssp_en      | 1       | Set to 0 for JTAG operations per IP vendor |      |

|       | 454                  | ref_clkdiv2     | 0       |                                            |      |

|       | 453                  |                 | 0       |                                            |      |

|       | 452                  |                 | 0       |                                            |      |

|       | 451                  |                 | 0       |                                            |      |

|       | 450                  | mpll_multiplier | 0       |                                            |      |

|       | 449                  | 48              | 0       |                                            |      |

|       | 448                  |                 | 0       |                                            |      |

|       | 447                  |                 | 0       |                                            |      |

|       | 446                  |                 | 1       |                                            |      |

|       | 445                  | tx_vboost_lvl   | 0       | Set to 3'b100 per IP vendor                |      |

| USB   | 444                  |                 | 0       |                                            |      |

|       | 443                  |                 | 0       |                                            |      |

|       | 442                  |                 | 0       |                                            |      |

|       | 441                  |                 | 0       |                                            |      |

|       | 440                  |                 | 0       |                                            |      |

|       | 439                  | ssc_ref_clk_sel | 0       |                                            |      |

|       | 438                  |                 | 0       |                                            |      |

|       | 437                  |                 | 0       |                                            |      |

|       | 436                  |                 | 0       |                                            |      |

|       | 435                  |                 | 0       |                                            |      |

|       | 434                  |                 | 0       |                                            |      |

|       | 433                  | ssc_range       | 0       |                                            |      |

|       | 432                  |                 | 0       |                                            |      |

Table 5. TDR layout (continued)

| Block | INIT_S<br>ETUP/<br>TDR Bit | Description           | Default | Note                       |

|-------|----------------------------|-----------------------|---------|----------------------------|

|       | 431                        |                       | 0       |                            |

|       | 430                        |                       | 0       |                            |

|       | 429                        | acjt_level            | 0       |                            |

|       | 428                        |                       | 0       |                            |

|       | 427                        |                       | 0       |                            |

|       | 426                        |                       | 0       |                            |

|       | 425                        |                       | 0       |                            |

|       | 424                        |                       | 0       |                            |

|       | 423                        |                       | 0       |                            |

|       | 422                        | pcs_rx_los_mask_val   | 0       |                            |

|       | 421                        | pcs_ix_ios_iiiask_vai | 0       |                            |

|       | 420                        |                       | 0       |                            |

|       | 419                        |                       | 0       |                            |

|       | 418                        |                       | 0       |                            |

|       | 417                        |                       | 0       |                            |

|       | 416                        |                       | 1       |                            |

|       | 415                        |                       | 1       |                            |

|       | 414                        |                       | 1       |                            |

|       | 413                        | pcs_tx_swing_full     | 1       | Set to 'd127 per IP vendor |

|       | 412                        |                       | 1       |                            |

|       | 411                        |                       | 0       |                            |

|       | 410                        |                       | 0       |                            |

|       | 409                        |                       | 1       |                            |

|       | 408                        | pcs_tx_deemph_6db     | 0       |                            |

|       | 407                        |                       | 0       |                            |

9/39

Table 5. TDR layout (continued)

| Block | INIT_S<br>ETUP/<br>TDR Bit | Description           | Default | Note                        |

|-------|----------------------------|-----------------------|---------|-----------------------------|

|       | 406                        |                       | 0       |                             |

|       | 405                        |                       | 1       |                             |

|       | 404                        |                       | 1       |                             |

|       | 403                        |                       | 0       |                             |

|       | 402                        |                       | 1       |                             |

|       | 401                        | nos ty doomph 2nEdh   | 1       | Sat to 1/1/24 nor ID yandar |

|       | 400                        | pcs_tx_deemph_3p5db   | 0       | Set to 'd24 per IP vendor   |

|       | 399                        |                       | 0       |                             |

|       | 398                        |                       | 0       |                             |

|       | 397                        |                       | 1       |                             |

|       | 396                        | los_bias              | 0       |                             |

|       | 395                        |                       | 1       |                             |

|       | 394                        | VATESTENB             | 0       |                             |

|       | 393                        | VATESTEND             | 0       |                             |

|       | 392                        | TXPREEMPPULSETUN<br>E | 0       |                             |

|       | 391                        |                       | 1       |                             |

|       | 390                        | TV/DEETLINEO          | 0       |                             |

|       | 389                        | TXVREFTUNE0           | 0       |                             |

|       | 388                        |                       | 1       |                             |

|       | 387                        | TXRISETUNE0           | 0       |                             |

|       | 386                        | TAINIGETUNEU          | 1       |                             |

|       | 385                        | TXRESTUNE0            | 0       |                             |

|       | 384                        | IANESTUNEU            | 1       |                             |

|       | 383                        | TXPREEMPAMPTUNE 0     | 0       |                             |

Table 5. TDR layout (continued)

| Block          | INIT_S<br>ETUP/<br>TDR Bit | Description         | Default | Note                                               |

|----------------|----------------------------|---------------------|---------|----------------------------------------------------|

|                | 382                        |                     | 1       |                                                    |

|                | 381                        | TXHSXVTUNE0         | 1       |                                                    |

|                | 380                        | INFONTONEO          | 1       |                                                    |

|                | 379                        |                     | 0       |                                                    |

|                | 378                        | TXFSLSTUNE0         | 0       |                                                    |

|                | 377                        | TAPSESTUNEO         | 1       |                                                    |

|                | 376                        |                     | 1       |                                                    |

|                | 375                        |                     | 0       |                                                    |

|                | 374                        | SQRXTUNE0           | 0       |                                                    |

|                | 373                        |                     | 0       |                                                    |

|                | 372                        |                     | 1       |                                                    |

|                | 371                        | OTGTUNE0            | 0       |                                                    |

|                | 370                        |                     | 0       |                                                    |

|                | 369                        |                     | 1       |                                                    |

|                | 368                        | COMPDISTUNE0        | 0       |                                                    |

|                | 367                        |                     | 0       |                                                    |

|                | 366                        |                     | 0       | 00 = 3.3 V (do not use)                            |

|                | 365                        | TVDD Voltage Select | 0       | 01 = 2.5 V<br>10 = 2.5 V<br>11 = 1.2 V/1.8 V       |

| Din            | 364                        |                     | 0       | 00 = 3.3 V (do not use)                            |

| Pin<br>Control | 363                        | LVDD Voltage Select | 0       | 01 = 2.5 V<br>10 = 2.5 V<br>11 = 1.2 V/1.8 V       |

|                | 362                        |                     | 0       | 00 = 3.3 V                                         |

|                | 361                        | EVDD Voltage Select | 0       | 01 = 2.5 V (do not use)<br>10 = 2.5 V (do not use) |

Table 5. TDR layout (continued)

| Block | INIT_S<br>ETUP/<br>TDR Bit | Description                         | Default |                                                                                             | Note |

|-------|----------------------------|-------------------------------------|---------|---------------------------------------------------------------------------------------------|------|

|       |                            |                                     |         | 11 = 1.2 V/1.8 V                                                                            |      |

|       | 360                        |                                     | 0       | 00 = 3.3 V                                                                                  |      |

|       | 359                        | DVDD Voltage Select                 | 0       | 01 = 2.5 V (do not use)<br>10 = 2.5 V (do not use)<br>11 = 1.2 V/1.8 V                      |      |

|       | 358                        | Auto-Detect Voltage                 | 0       | 0 = auto (Voltage Select<br>bits are don't care)<br>1 = manual (Use Voltage<br>Select bits) |      |

|       | 357                        | LVTTL control for ec2_rx_dv         | 0       |                                                                                             |      |

|       | 356                        | LVTTL control for ec2_rx_clk        | 0       |                                                                                             |      |

|       | 355                        | LVTTL control for ec2_rxd3          | 0       |                                                                                             |      |

|       | 354                        | LVTTL control for ec2_rxd2          | 0       |                                                                                             |      |

|       | 353                        | LVTTL control for ec2_rxd1          | 0       |                                                                                             |      |

|       | 352                        | LVTTL control for ec2_rxd0          | 0       | 0 = LVCMOS input levels                                                                     |      |

|       | 351                        | LVTTL control<br>for ec2_gtx_clk125 | 0       | 1 = LVTTL input levels                                                                      |      |

|       | 350                        | LVTTL control for ec2_gtx_clk       | 0       |                                                                                             |      |

|       | 349                        | LVTTL control for ec2_tx_en         | 0       |                                                                                             |      |

|       | 348                        | LVTTL control for ec2_txd3          | 0       |                                                                                             |      |

|       | 347                        | LVTTL control for ec2_txd2          | 0       |                                                                                             |      |

Table 5. TDR layout (continued)

| Block | INIT_S<br>ETUP/<br>TDR Bit | Description                         | Default |

|-------|----------------------------|-------------------------------------|---------|

|       | 346                        | LVTTL control for ec2_txd1          | 0       |

|       | 345                        | LVTTL control for ec2_txd0          | 0       |

|       | 344                        | LVTTL control for ec1_rx_dv         | 0       |

|       | 343                        | LVTTL control for ec1_rx_clk        | 0       |

|       | 342                        | LVTTL control for ec1_rxd3          | 0       |

|       | 341                        | LVTTL control for ec1_rxd2          | 0       |

|       | 340                        | LVTTL control for ec1_rxd1          | 0       |

|       | 339                        | LVTTL control for ec1_rxd0          | 0       |

|       | 338                        | LVTTL control<br>for ec1_gtx_clk125 | 0       |

|       | 337                        | LVTTL control for ec1_gtx_clk       | 0       |

|       | 336                        | LVTTL control for ec1_tx_en         | 0       |

|       | 335                        | LVTTL control for ec1_txd3          | 0       |

|       | 334                        | LVTTL control for ec1_txd2          | 0       |

|       | 333                        | LVTTL control for ec1_txd1          | 0       |

|       | 332                        | LVTTL control for ec1_txd0          | 0       |

|       | 331                        | LVTTL control for usb_pwrfault      | 0       |

Table 5. TDR layout (continued)

| Block | INIT_S<br>ETUP/<br>TDR Bit | Description                   | Default |

|-------|----------------------------|-------------------------------|---------|

|       | 330                        | LVTTL control for usb_drvvbus | 0       |

|       | 329                        | LVTTL control for iic4_sda    | 0       |

|       | 328                        | LVTTL control for iic4_scl    | 0       |

|       | 327                        | LVTTL control for iic3_sda    | 0       |

|       | 326                        | LVTTL control for iic3_scl    | 0       |

|       | 325                        | LVTTL control for emi_mdio    | 0       |

|       | 324                        | LVTTL control for emi_mdc     | 0       |

|       | 323                        | LVTTL control for irq11       | 0       |

|       | 322                        | LVTTL control for irq10       | 0       |

|       | 321                        | LVTTL control for irq9        | 0       |

|       | 320                        | LVTTL control for irq8        | 0       |

|       | 319                        | LVTTL control for irq7        | 0       |

|       | 318                        | LVTTL control for irq6        | 0       |

|       | 317                        | LVTTL control for irq5        | 0       |

|       | 316                        | LVTTL control for irq4        | 0       |

|       | 315                        | LVTTL control for irq3        | 0       |

|       | 314                        | LVTTL control for sdhc_clk    | 0       |

|       | 313                        | LVTTL control for sdhc_dat3   | 0       |

|       | 312                        | LVTTL control for sdhc_dat2   | 0       |

Table 5. TDR layout (continued)

| Block | INIT_S<br>ETUP/<br>TDR Bit | Description                   | Default |

|-------|----------------------------|-------------------------------|---------|

|       | 311                        | LVTTL control for sdhc_dat1   | 0       |

|       | 310                        | LVTTL control for sdhc_dat0   | 0       |

|       | 309                        | LVTTL control for sdhc_cmd    | 0       |

|       | 308                        | LVTTL control for iic2_sda    | 0       |

|       | 307                        | LVTTL control for iic2_scl    | 0       |

|       | 306                        | LVTTL control<br>for iic1_sda | 0       |

|       | 305                        | LVTTL control for iic1_scl    | 0       |

|       | 304                        | LVTTL control for uart2_cts_b | 0       |

|       | 303                        | LVTTL control for uart1_cts_b | 0       |

|       | 302                        | LVTTL control for uart2_rts_b | 0       |

|       | 301                        | LVTTL control for uart1_rts_b | 0       |

|       | 300                        | LVTTL control for uart2_sin   | 0       |

|       | 299                        | LVTTL control for uart1_sin   | 0       |

|       | 298                        | LVTTL control for uart2_sout  | 0       |

|       | 297                        | LVTTL control for uart1_sout  | 0       |

Table 5. TDR layout (continued)

| Block | INIT_S<br>ETUP/<br>TDR Bit | Description | Default |                                                                                                                                   | Note                                                                                                                                                                                                                                                            |

|-------|----------------------------|-------------|---------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 296<br>295                 |             | 0       | Drive Strength Enable group F,  000 - output driver disabled                                                                      |                                                                                                                                                                                                                                                                 |

|       | 294                        | dse_grp_f   | 0       | 001 = 240 Ohms<br>010 = 120 Ohms<br>011 = 80 Ohms<br>100 = 60 Ohms<br>101 = 48 Ohms<br>110 = 40 Ohms<br>111 = 34 Ohms (max drive) | Includes pins irq11, irq10, irq9, irq8, irq7, irq6, irq5, irq4, irq3, usb_drvvbus, usb_pwrfault                                                                                                                                                                 |

|       | 293                        |             | 1       | Drive Strength Enable group E,                                                                                                    |                                                                                                                                                                                                                                                                 |

|       | 292                        |             | 1       |                                                                                                                                   | Includes pins ec1_gtx_clk125,                                                                                                                                                                                                                                   |

|       | 291                        | dse_grp_e   | 0       | 001 = 240 Ohms<br>010 = 120 Ohms<br>011 = 80 Ohms<br>100 = 60 Ohms<br>101 = 48 Ohms<br>110 = 40 Ohms<br>111 = 34 Ohms (max drive) | ec1_rx_clk, ec1_rx_dv, ec1_rxd0, ec1_rxd1, ec1_rxd2, ex1_rxd3, ec1_tx_en, ec1_txd0, ec1_txd1, ec1_txd2, ec1_txd3, ec2_gtx_clk, ec2_gtx_clk125, ec2_rx_clk, ec2_rx_dv, ec2_rxd0, ec2_rxd1, ec2_rxd2, ec2_rxd3, ex2_tx_en, ec2_txd0, ec2_txd1, ec2_txd2, ec2_txd3 |

|       | 290                        |             | 1       | Drive Strength Enable group D,                                                                                                    |                                                                                                                                                                                                                                                                 |

|       | 289                        |             | 1       | 000 - output driver disabled                                                                                                      |                                                                                                                                                                                                                                                                 |

|       | 288                        | dse_grp_d   | 1       | 001 = 240 Ohms<br>010 = 120 Ohms<br>011 = 80 Ohms<br>100 = 60 Ohms<br>101 = 48 Ohms<br>110 = 40 Ohms<br>111 = 34 Ohms (max drive) | Includes pins emi2_mdio                                                                                                                                                                                                                                         |

Application Note 15 / 39

Table 5. TDR layout (continued)

| Block | INIT_S<br>ETUP/<br>TDR Bit | Description | Default |                                                                                                                                                                   | Note                                                                                                                                                                                                      |

|-------|----------------------------|-------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 287<br>286                 |             | 1       | Drive Strength Enable group C, 000 - output driver disabled                                                                                                       |                                                                                                                                                                                                           |

|       | 285                        | dse_grp_c   | 1       | 000 - Output driver disabled<br>001 = 240 Ohms<br>010 = 120 Ohms<br>011 = 80 Ohms<br>100 = 60 Ohms<br>101 = 48 Ohms<br>110 = 40 Ohms<br>111 = 34 Ohms (max drive) | Includes pins emi2_mdc                                                                                                                                                                                    |

|       | 284                        |             | 1       | Drive Strength Enable group B,                                                                                                                                    |                                                                                                                                                                                                           |

|       | 283                        |             | 1       | 000 - output driver disabled                                                                                                                                      |                                                                                                                                                                                                           |

|       | 282                        | dse_grp_b   | 1       | 001 = 240 Ohms<br>010 = 120 Ohms<br>011 = 80 Ohms<br>100 = 60 Ohms<br>101 = 48 Ohms<br>110 = 40 Ohms<br>111 = 34 Ohms (max drive)                                 | Includes pins sdhc_clk,<br>sdhc_cmd, sdhc_dat0, sdhc_dat1,<br>sdhc_dat2, sdhc_dat3                                                                                                                        |

|       | 281                        |             | 1       | Drive Strength Enable                                                                                                                                             |                                                                                                                                                                                                           |

|       | 280                        |             | 0       | group A, 000 = output                                                                                                                                             |                                                                                                                                                                                                           |

|       | 279                        | dse_grp_a   | 1       | driver disabled<br>001 = 240 Ohms<br>010 = 120 Ohms<br>011 = 80 Ohms<br>100 = 60 Ohms<br>101 = 48 Ohms<br>110 = 40 Ohms<br>111 = 34 Ohms (max drive)              | Includes pins iic1_scl, iic1_sda, iic2_scl, iic2_sda, iic3_scl, iic3_sda, iic4_scl, iic4_sda, uart1_cts_b, uart1_rts_b, uart1_sin, uart1_sout, uart2_cts_b, uart2_rts_b, uart2_sin, uart2_sin, uart2_sout |

Application Note 16 / 39

Table 5. TDR layout (continued)

| Block | INIT_S<br>ETUP/<br>TDR Bit | Description                           | Default | Note                          |

|-------|----------------------------|---------------------------------------|---------|-------------------------------|

|       | 278                        | Hysterisis control for ec2_rx_dv      | 0       |                               |

|       | 277                        | Hysterisis control for ec2_rx_clk     | 0       |                               |

|       | 276                        | Hysterisis control for ec2_rxd3       | 0       |                               |

|       | 275                        | Hysterisis control for ec2_rxd2       | 0       |                               |

|       | 274                        | Hysterisis control for ec2_rxd1       | 0       |                               |

|       | 273                        | Hysterisis control for ec2_rxd0       | 0       |                               |

|       | 272                        | Hysterisis control for ec2_gtx_clk125 | 0       |                               |

|       | 271                        | Hysterisis control for ec2_gtx_clk    | 0       | 0=off (CMOS input)            |

|       | 270                        | Hysterisis control for ec2_tx_en      | 0       | 1= on (Schmitt trigger input) |

|       | 269                        | Hysterisis control for ec2_txd3       | 0       |                               |

|       | 268                        | Hysterisis control for ec2_txd2       | 0       |                               |

|       | 267                        | Hysterisis control for ec2_txd1       | 0       |                               |

|       | 266                        | Hysterisis control for ec2_txd0       | 0       |                               |

|       | 265                        | Hysterisis control for ec1_rx_dv      | 0       |                               |

|       | 264                        | Hysterisis control for ec1_rx_clk     | 0       |                               |

|       | 263                        | Hysterisis control for ec1_rxd3       | 0       |                               |

Table 5. TDR layout (continued)

| Block | INIT_S<br>ETUP/<br>TDR Bit | Description                           | Default |

|-------|----------------------------|---------------------------------------|---------|

|       | 262                        | Hysterisis control for ec1_rxd2       | 0       |

|       | 261                        | Hysterisis control for ec1_rxd1       | 0       |

|       | 260                        | Hysterisis control for ec1_rxd0       | 0       |

|       | 259                        | Hysterisis control for ec1_gtx_clk125 | 0       |

|       | 258                        | Hysterisis control for ec1_gtx_clk    | 0       |

|       | 257                        | Hysterisis control for ec1_tx_en      | 0       |

|       | 256                        | Hysterisis control for ec1_txd3       | 0       |

|       | 255                        | Hysterisis control for ec1_txd2       | 0       |

|       | 254                        | Hysterisis control for ec1_txd1       | 0       |

|       | 253                        | Hysterisis control for ec1_txd0       | 0       |

|       | 252                        | Hysterisis control for usb_pwrfault   | 0       |

|       | 251                        | Hysterisis control for usb_drvvbus    | 0       |

|       | 250                        | Hysterisis control for iic4_sda       | 0       |

|       | 249                        | Hysterisis control for iic4_scl       | 0       |

|       | 248                        | Hysterisis control for iic3_sda       | 0       |

|       | 247                        | Hysterisis control for iic3_scl       | 0       |

Application Note 18 / 39

Table 5. TDR layout (continued)

| Block | INIT_S<br>ETUP/<br>TDR Bit | Description                      | Default |

|-------|----------------------------|----------------------------------|---------|

|       | 246                        | Hysterisis control for emi_mdio  | 0       |

|       | 245                        | Hysterisis control for emi_mdc   | 0       |

|       | 244                        | Hysterisis control for irq11     | 0       |

|       | 243                        | Hysterisis control for irq10     | 0       |

|       | 242                        | Hysterisis control for irq9      | 0       |

|       | 241                        | Hysterisis control for irq8      | 0       |

|       | 240                        | Hysterisis control for irq7      | 0       |

|       | 239                        | Hysterisis control for irq6      | 0       |

|       | 238                        | Hysterisis control for irq5      | 0       |

|       | 237                        | Hysterisis control for irq4      | 0       |

|       | 236                        | Hysterisis control for irq3      | 0       |

|       | 235                        | Hysterisis control for sdhc_clk  | 0       |

|       | 234                        | Hysterisis control for sdhc_dat3 | 0       |

|       | 233                        | Hysterisis control for sdhc_dat2 | 0       |

|       | 232                        | Hysterisis control for sdhc_dat1 | 0       |

|       | 231                        | Hysterisis control for sdhc_dat0 | 0       |

|       | 230                        | Hysterisis control for sdhc_cmd  | 0       |

|       | 229                        | Hysterisis control for iic2_sda  | 0       |

Table 5. TDR layout (continued)

| Block | INIT_S<br>ETUP/<br>TDR Bit | Description                        | Default | Note                                      |

|-------|----------------------------|------------------------------------|---------|-------------------------------------------|

|       | 228                        | Hysterisis control for iic2_scl    | 0       |                                           |

|       | 227                        | Hysterisis control for iic1_sda    | 0       |                                           |

|       | 226                        | Hysterisis control for iic1_scl    | 0       |                                           |

|       | 225                        | Hysterisis control for uart2_cts_b | 0       |                                           |

|       | 224                        | Hysterisis control for uart1_cts_b | 0       |                                           |

|       | 223                        | Hysterisis control for uart2_rts_b | 0       |                                           |

|       | 222                        | Hysterisis control for uart1_rts_b | 0       |                                           |

|       | 221                        | Hysterisis control for uart2_sin   | 0       |                                           |

|       | 220                        | Hysterisis control for uart1_sin   | 0       |                                           |

|       | 219                        | Hysterisis control for uart2_sout  | 0       |                                           |

|       | 218                        | Hysterisis control for uart1_sout  | 0       |                                           |

|       | 217                        | Slewrate control                   | 1       |                                           |

|       | 216                        | for ec2_rx_dv                      | 0       |                                           |

|       | 215                        | Slewrate control                   | 1       |                                           |

|       | 214                        | for ec2_rx_clk                     | 0       | 00 = Slow slew rate 01 = Medium slew rate |

|       | 213                        | Slewrate control                   | 1       | 10 = Fast slew rate                       |

|       | 212                        | for ec2_rxd3                       | 0       | 11 = Max slew rate                        |

|       | 211                        | Slewrate control                   | 1       |                                           |

|       | 210                        | for ec2_rxd2                       | 0       |                                           |

Table 5. TDR layout (continued)

| Block | INIT_S<br>ETUP/<br>TDR Bit | Description                   | Default |

|-------|----------------------------|-------------------------------|---------|

|       | 209                        | Slewrate control              | 1       |

|       | 208                        | for ec2_rxd1                  | 0       |

|       | 207                        | Slewrate control              | 1       |

|       | 206                        | for ec2_rxd0                  | 0       |

|       | 205                        | Slewrate control              | 1       |

|       | 204                        | for ec2_gtx_clk125            | 0       |

|       | 203                        | Slewrate control              | 1       |

|       | 202                        | for ec2_gtx_clk               | 0       |

|       | 201                        | Slewrate control              | 1       |

|       | 200                        | for ec2_tx_en                 | 0       |

|       | 199                        | Slewrate control              | 1       |

|       | 198                        | for ec2_txd3                  | 0       |

|       | 197                        | Slewrate control              | 1       |

|       | 196                        | for ec2_txd2                  | 0       |

|       | 195                        | Slewrate control              | 1       |

|       | 194                        | for ec2_txd1                  | 0       |

|       | 193                        | Slewrate control              | 1       |

|       | 192                        | for ec2_txd0                  | 0       |

|       | 191                        | Slewrate control              | 1       |

|       | 190                        | for ec1_rx_dv                 | 0       |

|       | 189                        | Slewrate control              | 1       |

|       | 188                        | for ec1_rx_clk                | 0       |

|       | 187                        |                               | 1       |

|       | 186                        | Slewrate control for ec1_rxd3 | 0       |

Table 5. TDR layout (continued)

| Block | INIT_S<br>ETUP/<br>TDR Bit | Description                      | Default |  |

|-------|----------------------------|----------------------------------|---------|--|

|       | 185                        | Slewrate control                 | 1       |  |

|       | 184                        | for ec1_rxd2                     | 0       |  |

|       | 183                        | Slewrate control                 | 1       |  |

|       | 182                        | for ec1_rxd1                     | 0       |  |

|       | 181                        | Slewrate control                 | 1       |  |

|       | 180                        | for ec1_rxd0                     | 0       |  |

|       | 179                        | Slewrate control                 | 1       |  |

|       | 178                        | for ec1_gtx_clk125               | 0       |  |

|       | 177                        | Slewrate control                 | 1       |  |

|       | 176                        | for ec1_gtx_clk                  | 0       |  |

|       | 175                        | Slewrate control                 | 1       |  |

|       | 174                        | for ec1_tx_en                    | 0       |  |

|       | 173                        | Slewrate control                 | 1       |  |

|       | 172                        | for ec1_txd3                     | 0       |  |

|       | 171                        | Slewrate control                 | 1       |  |

|       | 170                        | for ec1_txd2                     | 0       |  |

|       | 169                        | Slewrate control                 | 1       |  |

|       | 168                        | for ec1_txd1                     | 0       |  |

|       | 167                        | Slewrate control                 | 1       |  |

|       | 166                        | for ec1_txd0                     | 0       |  |

|       | 165                        | Slewrate control                 | 0       |  |

|       | 164                        | for usb_pwrfault                 | 0       |  |

|       | 163                        |                                  | 0       |  |

|       | 162                        | Slewrate control for usb_drvvbus | 0       |  |

Table 5. TDR layout (continued)

| Block | INIT_S<br>ETUP/<br>TDR Bit | Description                      | Default |

|-------|----------------------------|----------------------------------|---------|

|       | 161                        | Slewrate control                 | 0       |

|       | 160                        | for iic4_sda                     | 0       |

|       | 159                        | Slewrate control                 | 0       |

|       | 158                        | Slewrate control<br>for iic4_scl | 0       |

|       | 157                        | Slewrate control                 | 0       |

|       | 156                        | for iic3_sda                     | 0       |

|       | 155                        | Slewrate control                 | 0       |

|       | 154                        | for iic3_scl                     | 0       |

|       | 153                        | Slewrate control                 | 1       |

|       | 152                        | for emi_mdio                     | 0       |

|       | 151                        | Slewrate control                 | 1       |

|       | 150                        | for emi_mdc                      | 0       |

|       | 149                        |                                  | 0       |

|       | 148                        | Slewrate control for irq11       | 0       |

|       | 147                        |                                  | 0       |

|       | 146                        | Slewrate control for irq10       | 0       |

|       | 145                        |                                  | 0       |

|       | 144                        | Slewrate control for irq9        | 0       |

|       | 143                        |                                  | 0       |

|       | 142                        | Slewrate control for irq8        | 0       |

|       | 141                        |                                  | 0       |

|       | 140                        | Slewrate control for irq7        | 0       |

|       | 139                        |                                  | 0       |

|       | 138                        | Slewrate control for irq6        | 0       |

|       | 137                        | Slewrate control for irq5        | 0       |

Table 5. TDR layout (continued)

| Block | INIT_S<br>ETUP/<br>TDR Bit | Description               | Default |

|-------|----------------------------|---------------------------|---------|

|       | 136                        |                           | 0       |

|       | 135                        | Slewrate control for irq4 | 0       |

|       | 134                        | Slewrate control for irq4 | 0       |

|       | 133                        |                           | 0       |

|       | 132                        | Slewrate control for irq3 | 0       |

|       | 131                        | Slewrate control          | 1       |

|       | 130                        | for sdhc_clk              | 0       |

|       | 129                        | Slewrate control          | 1       |

|       | 128                        | for sdhc_cmd              | 0       |

|       | 127                        | Slewrate control          | 1       |

|       | 126                        | for sdhc_dat3             | 0       |

|       | 125                        | Slewrate control          | 1       |

|       | 124                        | for sdhc_dat2             | 0       |

|       | 123                        | Slewrate control          | 1       |

|       | 122                        | for sdhc_dat1             | 0       |

|       | 121                        | Slewrate control          | 1       |

|       | 120                        | for sdhc_dat0             | 0       |

|       | 119                        | Slewrate control          | 0       |

|       | 118                        | for iic2_sda              | 0       |

|       | 117                        | Slewrate control          | 0       |

|       | 116                        | for iic2_scl              | 0       |

|       | 115                        | Slewrate control          | 0       |

|       | 114                        | for iic1_sda              | 0       |

|       | 113                        | Slewrate control          | 0       |

|       | 112                        | for iic1_scl              | 0       |

Table 5. TDR layout (continued)

| Block       | INIT_S<br>ETUP/<br>TDR Bit | Description                                                        | Default |                        | Note                                                                                                         |

|-------------|----------------------------|--------------------------------------------------------------------|---------|------------------------|--------------------------------------------------------------------------------------------------------------|

|             | 111                        | Slewrate control                                                   | 0       |                        |                                                                                                              |

|             | 110                        | for uart2_cts_b                                                    | 0       |                        |                                                                                                              |

|             | 109                        | Slewrate control for uart1_cts_b                                   | 0       |                        |                                                                                                              |

|             | 108                        |                                                                    | 0       |                        |                                                                                                              |

|             | 107                        | Slewrate control for uart2_rts_b  Slewrate control for uart1_rts_b | 0       |                        |                                                                                                              |

|             | 106                        |                                                                    | 0       |                        |                                                                                                              |

|             | 105                        |                                                                    | 0       |                        |                                                                                                              |

|             | 104                        |                                                                    | 0       |                        |                                                                                                              |

|             | 103                        | Slewrate control                                                   | 0       |                        |                                                                                                              |

|             | 102                        | for uart2_sin                                                      | 0       |                        |                                                                                                              |

|             | 101                        | Slewrate control for uart1_sin Slewrate control                    | 0       |                        |                                                                                                              |

|             | 100                        |                                                                    | 0       |                        |                                                                                                              |

|             | 99                         |                                                                    | 0       |                        |                                                                                                              |

|             | 98                         | for uart2_sout                                                     | 0       |                        |                                                                                                              |

|             | 97                         | Slewrate control                                                   | 0       |                        |                                                                                                              |

|             | 96                         | for uart1_sout                                                     | 0       |                        |                                                                                                              |

|             | 95                         |                                                                    | 0       | [4] REF Clock ioconfig | 111 = Reserved                                                                                               |

|             | 94                         |                                                                    | 0       | [3] REF Clock ioconfig | 110 = Reference Clock 200 mV min, on-<br>chip AC coupling, used when board is<br>externally DC-Coupled       |

|             |                            |                                                                    |         |                        | 101 = Reserved                                                                                               |

| SerDes<br>1 |                            | PLL1 initdata                                                      |         |                        | 100 = Reference Clock 400 mV min, on-<br>chip AC coupling, used when board is<br>externally DC-Coupled       |

|             | 93                         |                                                                    | 0       | [2] REF Clock ioconfig | 011 = Reserved                                                                                               |

|             |                            |                                                                    |         |                        | 010 = Reference Clock 200 mV min,<br>shunts on-chip AC coupling, used when<br>board is externally AC-Coupled |

|             |                            |                                                                    |         |                        | 001 = Reserved                                                                                               |

Table 5. TDR layout (continued)

| Block | INIT_S<br>ETUP/<br>TDR Bit | Description     | Default |                 | Note                                                                                                                                 |

|-------|----------------------------|-----------------|---------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------|

|       |                            |                 |         |                 | 000 = Reference Clock 400 mV min,<br>shunts on-chip AC coupling, used when<br>board is externally AC-Coupled                         |

|       | 92                         |                 | 0       | [1] reserved    |                                                                                                                                      |

|       | 91                         |                 | 0       | [0] reserved    |                                                                                                                                      |

|       | 90                         |                 | 0       | [4] RX ioconfig | 111 = Reserved                                                                                                                       |

|       | 89                         |                 | 0       | [3] RX ioconfig | 110 = Reserved                                                                                                                       |

|       |                            |                 |         | [o] rociocomig  | 101 = Reserved                                                                                                                       |

|       |                            |                 |         |                 | 100 = Reserved                                                                                                                       |

|       |                            |                 |         |                 | 011 = SGMII                                                                                                                          |

|       | 88                         | Lane A initdata | 0       | [2] RX ioconfig | 010 = SRIO Short, SGMII 2.5x, QSGMII, JEDEC, SATA, XFI, Interlaken Short, Interlaken 10G, 10GBaseKR                                  |

|       |                            |                 |         |                 | 001 = Reserved                                                                                                                       |

|       |                            |                 |         |                 | 000 = PEX3, PEX2, PEX, 1000BaseKX                                                                                                    |

|       | 87                         |                 | 0       | [1] TX ioconfig | 11= SGMII, JDEC (0.667*full swing)                                                                                                   |

|       |                            |                 |         | [0] TX ioconfig | 10 = SATA, Interlaken 10G, Interlaken<br>Short, JEDEC, XFI (0.585*full swing)<br>01 = SRIO Short, QSGMII, JEDEC<br>(0.75*full swing) |

|       | 86                         |                 | 0       |                 | 00 = PEX3, PEX2, PEX, SGMII<br>2.5x, 10GBaseKR, 1000BaseKX<br>(1.0*full swing)                                                       |

|       | 85                         |                 | 0       | [4] RX ioconfig | 111 = Reserved                                                                                                                       |

|       | 84                         |                 | 0       | [3] RX ioconfig | 110 = Reserved                                                                                                                       |

|       |                            |                 |         |                 | 101 = Reserved                                                                                                                       |

|       |                            |                 |         |                 | 100 = Reserved                                                                                                                       |

|       | Lane B                     | Lane B initdata |         |                 | 011 = SGMII                                                                                                                          |

|       |                            |                 | 0       | [2] RX ioconfig | 010 = SRIO Short, SGMII 2.5x, QSGMII, JEDEC, SATA, XFI, Interlaken Short, Interlaken 10G, 10GBaseKR                                  |