# AN12866

# Fault Collection and Control Unit (FCCU) Usage on S32V23x

Rev. 0 — November, 2020 Application Note

by: NXP Semiconductors

### 1 Introduction

The Fault Collection and Control Unit (FCCU) offers a hardware channel to collect faults and to place the device into a safe state when a failure in the device is detected. The FCCU offers a systematic approach to fault collection and control. No CPU intervention is required for fault collection and control operation, unless the FCCU is specifically configured to cause software intervention (by triggering IRQs or NMIs).

#### Contents

| 1 | Introduction                | <i>'</i> |

|---|-----------------------------|----------|

| 2 | FCCU functional description | 2        |

| 3 | MCAL FCCU configurations    |          |

| 4 | Mcem APIs descriptions      |          |

| 5 | Use case examples           |          |

| 6 | Summary                     |          |

| 7 | Reference                   |          |

This application note describes how to use FCCU based on MCAL SW product for <u>S32V23x</u>. Please install <u>EB21.0</u> and <u>S32V234\_MCAL4\_2\_RTM\_HF1\_1\_0\_1</u> on your computer before using the MCAL FCCU driver. EB and MCAL development environment setup are out of the scope of this document. It assumes that you are familiar with the MCAL software development environment and the document focuses on FCCU configurations in EB and usage in the application. FCCU also depends on other MCAL modules such as MCU, DET (see [1]for more details).

This document contains the following sections:

- FCCU functional description: This section introduces FCCU state machine and fault reaction mechanism.

- · MCAL FCCU configuration: This section introduces how to config FCCU and different fault reactions in EB.

- · Mcem APIs descriptions: This section describes functionalities of Mcem APIs.

- · Use case examples: This section describes two use cases based on alarm interrupt and reset reaction of fault.

- Summary: This section describes the document scope and provides some implementation hints about FCCU usage for target application.

The following abbreviations are used in the application note.

Table 1. Acronyms and abbreviations

| Abbreviations | Description                      |

|---------------|----------------------------------|

| EOUT          | Error Out                        |

| FOSU          | FCCU output supervision unit     |

| FSM           | Finite state machine             |

| INTC          | Interrupt controller             |

| intf          | Interface                        |

| IRQ           | Interrupt request                |

| NCF           | Noncritical fault                |

| NMI           | Nonmaskable interrupt            |

| WKPU          | Wake-up unit                     |

| МСЕМ          | Microcontroller Error Management |

# 2 FCCU functional description

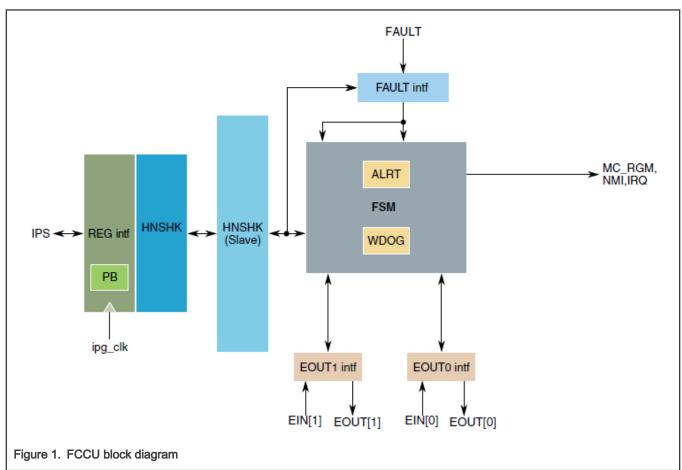

The following figure shows the architecture of FCCU module. At the heart of the FCCU is a Finite State Machine (FSM) around which, various signaling connections and logic modules are connected.

Table 2. FCCU submodules

| Submodule                              | Submodule Description                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REG intf                               | Includes the register file, the IPS bus interface, the IRQ interface and the parity block (PB) for the configuration registers                                                                                                                                                                                                                                                                                         |

| HNSHK blocks (master and slave blocks) | Includes the FSM's ability to support the handshake between the REG interface and the FSM unit due to the usage of two asynchronous clocks(IPS system clock and RC oscillator clock)                                                                                                                                                                                                                                   |

| FSM unit                               | <ul> <li>Implements the main functions of the FCCU. The FSM also includes the:</li> <li>Watchdog timer (WDG): for reconfiguration phase, FCCU automatically leaves Configuration state and enters Normal state if WDG timeouts.</li> <li>Alarm timer (ALRT): the timer starts when FCCU enters ALARM state if the faults are not removed in timer interval, FCCU leaves ALARM state and enters FAULT state.</li> </ul> |

Table continues on the next page...

Application Note 2 / 12

Table 2. FCCU submodules (continued)

| Submodule   | Submodule Description                                              |

|-------------|--------------------------------------------------------------------|

| FAULT intf  | Implements the interface for the fault conditioning and management |

| EOUTx units | Implement the output stage to manage the EOUT interfaces           |

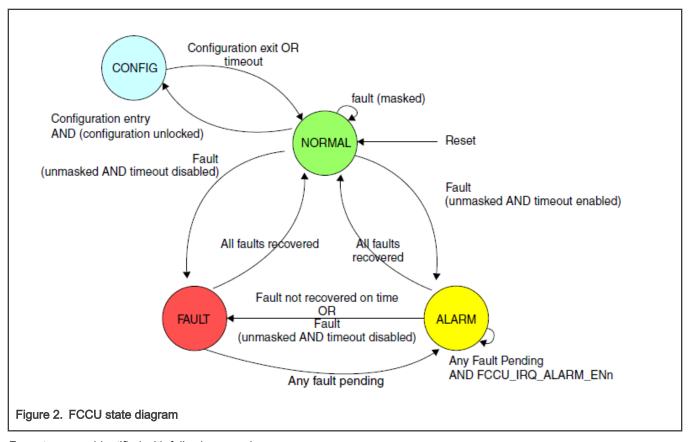

FCCU functionality is depicted by the finite state machine (FSM) state diagram.

Four stares are identified with following meaning:

- CONFIG: Put FCCU in configuration state to change its configuration. A subset of FCCU registers, dedicated to FCCU configuration can be accessed in write mode only in Configuration state.

- NORMAL: This is FCCU's operating state when no faults are occurring or all faults have been recovered. It is also the default state on the reset exit.

- ALARM: : FCCU moves into Alarm state when an unmasked noncritical fault occurs and the timeout is enabled. The transition to Alarm state goes along with an interrupt alarm, if enabled. By definition, this fault may be recovered within a programmable timeout period, before it generates a transition to Fault state. The timeout is reinitialized if FCCU enters Normal state following the recovery from Fault state.

- FAULT: FCCU moves into Fault state:

- 1. Timeout related to a noncritical fault when FCCU is in Alarm state.

- 2. Unmasked noncritical faults with the timeout disabled.

The transition from Normal/Alarm to Fault state goes along with the generation of:

• NMI interrupt (optional): Sends a nonmaskable interrupt request to the processor core or cores when FCCU enters Fault state as the result of a noncritical fault for which NMI is enabled as the reaction.

- EOUT signaling (optional): EOUT[1:0] signals used to indicate FCCU's condition to off-chip logic. Different fault-output modes (protocols) for the fault-output (EOUT) pins are supported: Dual-Rail, Time-Switching, Bistable and Test (see section 73.8.8 of S32V234 RM for details).

- SW option: Soft reaction (Short functional reset).

- · SW option: Hard reaction (Long functional reset).

MC\_RGM will generate a short/long functional reset if a fault occurrs and configured with short/long reset reaction.

## 3 MCAL FCCU configurations

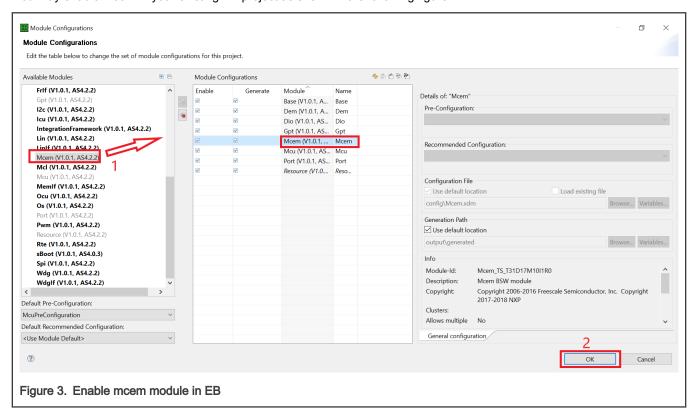

The FCCU and MEMU IPs of the S32V23x are used by MCEM driver. In this note, only the FCCU is discussed. FCCU driver is released as a part of the Mcem module in the MCAL package. FCCU configurations and the fault management could be configured in EB if the module is imported into a tresos project.

The MCEM plugin supports configuring the reaction to the faults in the system. The MCEM driver has the following major features:

- 1. Set the reaction time for faults.

- 2. Set the reaction type for each fault.

- 3. Set the recovery type for each fault.

- 4. Set the User Callback for ALARM state.

- 5. Set the type of external reporting of the error.

Mcem driver provides the functionality of initializing FCCU, clear FCCU fault, inject fake fault, FCCU alarm interrupt callback function definition and etc.

## 3.1 Configuring FCCU

You may enable Mcem in your existing EB project as shown in the following figure.

Fault Collection and Control Unit (FCCU) Usage on S32V23x, Rev. 0, November, 2020

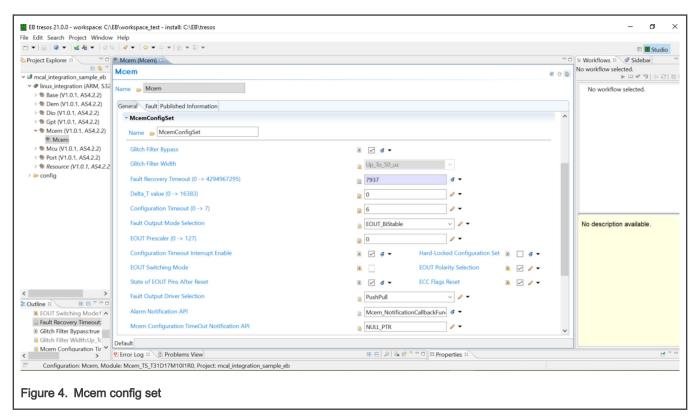

After enabling Mcem in the EB project, Mcem is now configurable. FCCU system parameters are configured in the McemConfigSet interface.

Fault Recovery Timeout – Non-critical fault timeout. If the fault with enabled recovery timeout is not recovered within the timeout inteval, the FCCU moves from the ALARM state to the FAULT state. NCF timeout can be computed using the following equations:

Timeout = TRC16 MHz × FaultTimeout

Timeout =  $0.0625 \times FaultTimeout [\mu s]$

Please note that the timeout value shall always be less than FOCU count, which is fixed preprogrammed as 0x1F40. Otherwise, a destructive reset will be generated by a FOSU time-out (A 'destructive' reset indicates that an event has occurred after which critical register or memory content can no longer be guaranteed). This ensures that the FOSU reacts only when the FCCU fails to react to any particular fault.

Configuration Timeout - FCCU configuration timeout.

Fault Output Mode Selection - Select fault output mode as Daul-Rail, Time Switching or Bi-Stable.

Configuration Timeout Interrupt Enable – Enable timeout interrupt during mode configuration. If this item is checked, the timeout shall notify the application using this callback in **Mcem Configuration TimeOut Notification API**.

**Alarm Notification API** – This callback is used to notify the application in case of a failure event, whose reaction is configured as an alarm interrupt.

Application Note 5 / 12

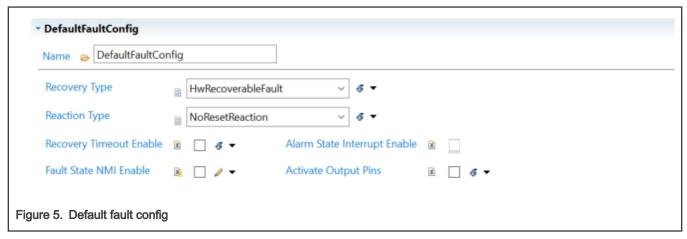

If the faults are not configured in the Fault panel, they are configured as enabled in DefaultFaultConfig by default. It is recommended to disable the fault in Fault panel if you are not intended to enable this fault.

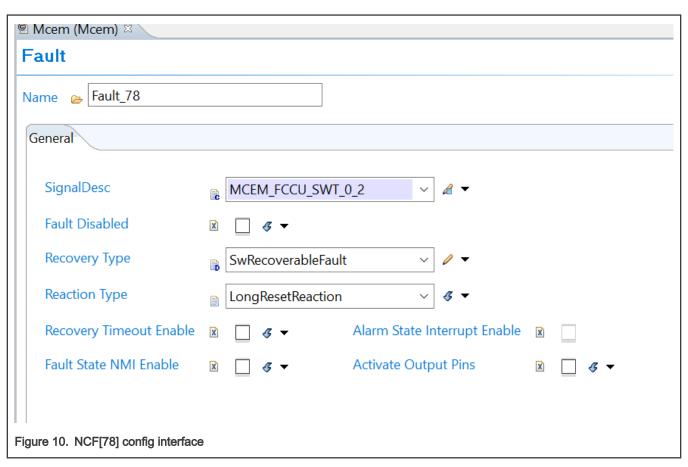

## 3.2 Configuring NCF reaction

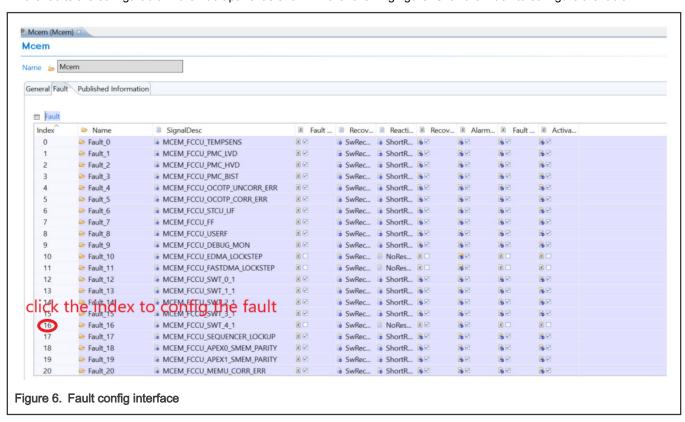

All the faults are configurable in the Fault panel as shown in the following figure. Click the index to configure the fault.

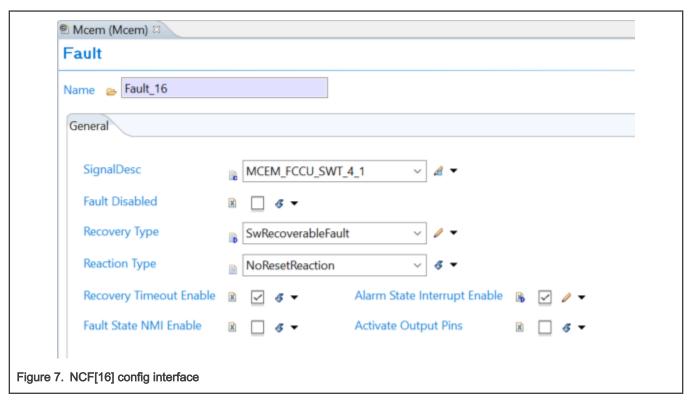

Take an example of NCF[16], it is a fault caused by SWT4 first timeout.

- SignalDesc Fault is selected here.

- Fault Disabled Check to disable a fault, uncheck means enable the fault.

- Recovery Type Defines fault recovery mode as hardware recoverable or software recoverable.

HW recoverable faults are self-recovered (status flag clearing and related) if the root cause (input fault)has been removed.

SW recoverable faults are recovered (status flag clearing) by SW clearing of the related status flag.

- Reaction Type Set the fault state reaction type for fault. There are three reaction types for fault state no reaction, short reset

reaction and long reset reaction.

- Recovery Timeout Enable Enable/disable recovery timeout. FCCU transitions form ALARM to FAULT state if the respective fault is not recovered within the Recovery Timeout.

- Alarm State Interrupt Enable Enable/disable alarm state interrupt for fault source.

If you want to config fault reaction as IRQ, both Recovery Timeout Enable and ALARM State Interrupt Enable shall be enabled.

• Fault State NMI Enable - Enable/disable NMI for fault source.

NOTE

If FCCU faults are managed on M4 and configured as NMI reaction, please enable the bitfield FCCU\_NMI\_DIS of register SRC\_GPR16 for M4.

Active Output Pins – Enable/disable EOUT signal for fault source in fault state. The EOUT protocol is set in Fault Output Mode Selection.

# 4 Mcem APIs descriptions

Functionality of all APIs supported by the driver are as per AUTOSAR MCEM Driver software specification Version 4.2 Rev002. This section introduces the basic APIs, for the full specification please see [3].

- Mcem\_Init() Initializes the MCEM driver according to the configuration parameters passed as an input.

- Mcem\_CheckNMI() Checks whether the initialized MCEM module is the source of the NMI request.

Application Note 7/12

- Mcem\_GetErrors() Return logged error status. This function stores status of each NCF into a container provided by the application.

- Mcem\_ClearFaults() Clear software recoverable fault. When a software recoverable fault occurs, a software routine resolves the fault cause, then it clears the fault status using this function.

- Mcem\_InjectFaults() Inject a fake fault.

- Mcem\_GetVersionInfo() Get software version.

## 5 Use case examples

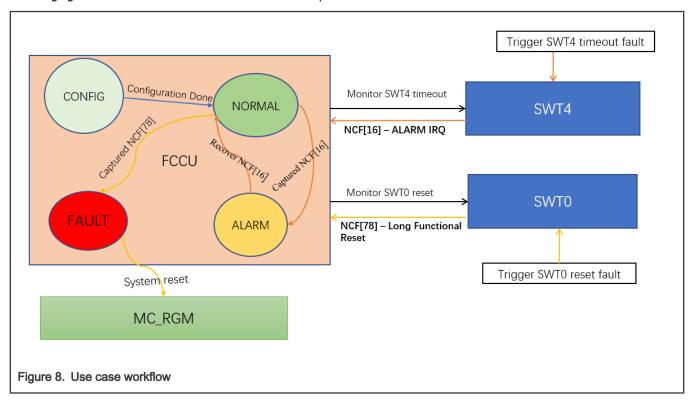

This section demonstrates the use of two fault reaction types, Fault reaction with ALARM IRQ and fault reaction with reset. The following figure shows the work flow of the use case examples.

#### 5.1 ALARM IRQ reaction

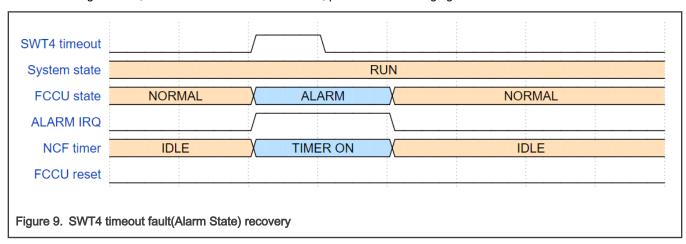

This section describes the process to handle a Mcem IRQ reaction fault, take an example of SWT4 timeout fault (NCF[16]). SWT4 is enabled via MCAL wdg driver, the timeout value is set as 500 ms and SWT4 is serviced every 200 ms.

```

/* Initialize SWT4 */

Wdg 43 Instance4 Init( &WdgSettingsConfig 4 );

Wdg 43 Instance4 SetMode( WDGIF SLOW MODE );

```

Firstly, Mcem shall be initallized. Mcem is configured as shown in Figure 4, Mcem is used to configure the SWT4 first timeout fault reaction as IRQ as per Figure 7.

```

/* Initialize Mcem */

Mcem Init(&McemConfigSet);

```

Fault Collection and Control Unit (FCCU) Usage on S32V23x, Rev. 0, November, 2020 **Application Note** 8 / 12 If there is a fault configured with its reaction as IRQ, please enable FCCU ALARM interrupt, and Mcem interrupt service routine(ISR) FCCU\_ALARM\_ISR shall also be registered, e.g.

```

/* Register Handler of interrupt 74 */

NVIC SetPriority ( 74, 0xf0 );

RegisterISRHandler( 74, &FCCU ALARM ISR );

NVIC EnableIRQ( 74 );

```

SWT4 timeout fault can be triggered manually, by modifying the SWT Time-out (SWT\_TO) register to make the periodic cycle smaller than 200ms. If such a fault was injected, FCCU will capture such a fault, and trigger the ALARM IRQ.

As Alarm Notification API is configured as *Mcem NotificationCallbackFunction*, and the prototype for the function is as follow.

```

void Mcem NotificationCallbackFunction( Mcem FaultType FaultID );

```

FaultID is the fault source caused FCCU entered ALARM state, the ID is consistent with S32V234 NCF List.xslx. If removed the reference link in reference section, just add the description for its location as (is present as an attachment in the [2]) when it occurs firstly in this document. In this case, FaultID is 16.

Please clear the fault as the column "Fault Clearing Mechanism" described in S32V234\_NCF\_List.xlsx. For MCEM FCCU SWT 4\_1, the fault shall be recovered first, then clear the corresponding fault status FCCU NCF S0[16]. The pseudocode is as follows.

```

/* disable swt4 */

(&INTERNAL SWT4) -> CR.B.WEN = false;

/* re-set swt4 timeout value */

(&INTERNAL SWT4) ->TO.B.WTO = SWT TO VALUE;

/* clear swt4 timeout interrupt flag */

(&INTERNAL SWT4) -> IR.B.TIF = 1;

/* re-enable swt4 */

(&INTERNAL SWT4) -> CR.B.WEN = true;

/*clear fault status*/

Mcem ClearFaults (Fault Id )

```

After recovering the fault, FCCU transitions to Normal state, please see following figure for more details.

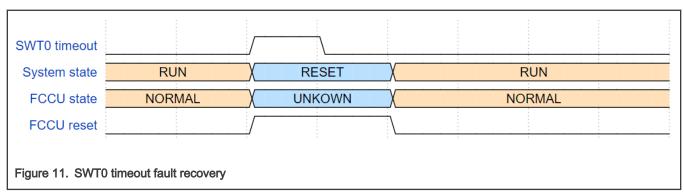

#### 5.2 Reset reaction

This section describes the use case of a Mcem reset reaction fault, take an example of SWT0 reset fault(SWT0 System Reset Request-NCF[78]).

NCF[78] shall be configured as the following figure. Here the reaction type is configured as Long Reset Reaction.

SWT0 shall be enabled before Mcem initialization.

```

/* Initialize SWT0 */

Wdg_43_Instance0_Init( &WdgSettingsConfig_0 );

Wdg_43_Instance0_SetMode( WDGIF_SLOW_MODE );

/* Initialize Mcem */

Mcem_Init(&McemConfigSet);

```

Assuming that the fault is triggered by swt0 timeout, after the FCCU captures this fault, the system will reset, as shown in the following figure. To validate the correct reset reaction, the MC\_RGM\_FESS register can be checked after system restart, SS\_FCCU\_HARD bit will be set. When the SS\_FCCU\_HARD bit is set, the FCCU has successfully triggered a long functional reset.

Application Note 10 / 12

## 6 Summary

FCCU features can be enabled and integrated in various software environments. NXP provides a FCCU driver in the S32V234 ISO26262 MCAL product, which is developed according to the SEooC requirements of ISO26262. This document describes the usage of FCCU based on MCAL. If you are intended to implement FCCU features in other software environments, please refer to section 73.11 in [2] for more guidelines and recommendations.

All faults detected by hardware measures are reported to the FCCU. There are total of 128 NCFs which could be monitored by FCCU. Depending on the type of fault, the FCCU places the device into an appropriate safe state. To achieve this, application software is required to configure FCCU appropriately.

The details of 128 NCFs are described in S32V234\_NCF\_List.xlsx, including the fault clearing mechanism and recommended reactions for each fault.

In this document, the implementations of alarm reaction and reset reaction for two faults are introduced. About the EOUT reaction, failure of the S32V23x is signaled to one or two pins (FCCU\_F0 and FCCU\_F1) for external failure indication. If the S32V23x signals an internal failure on its error out signals, the system may no longer rely on the integrity of the other S32V23x outputs for safety functions. The overall system needs to include measures to monitor FCCU\_Fn of the S32V23x and move the system to a safe state when an error is indicated.

In summary, FCCU provides a flexible mechanism for users to manage faults. It is the responsibility of the application software to manage the fault reaction according to the specific safety requirements.

#### 7 Reference

- Integration Manual for S32V234 Mcem Driver, IM17MCEMASR4.2 Rev002R1.0.1,Rev. 1.0 (included in AUTOSAR 4.2 MCAL (ISO 26262) for S32V234)

- 2. S32V234 Reference Manual, S32V234RM, Rev. 5, 11/2019

- User Manual for S32V234 Mcem Driver, UM17MCEMASR4.2 Rev002R1.0.1, Rev. 1.0(included in AUTOSAR 4.2 MCAL (ISO 26262) for S32V234)

Application Note 11 / 12

How To Reach Us

Home Page:

nxp.com

Web Support:

nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

While NXP has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities on customer's applications and products, and NXP accepts no liability for any vulnerability that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorlQ, QorlQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamlQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, μVision, Versatile are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© NXP B.V. 2020.

All rights reserved.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: November, 2020 Document identifier: AN12866