# Software Defined Radio Processor for V2X Communication

# SAF5100

Last Updated: Jun 7, 2023

The SAF5100 is available in a Ball Grid Array (BGA) package occupying small Printed-Circuit Board (PCB) real estate and is suitable for multi-layer PCBs.

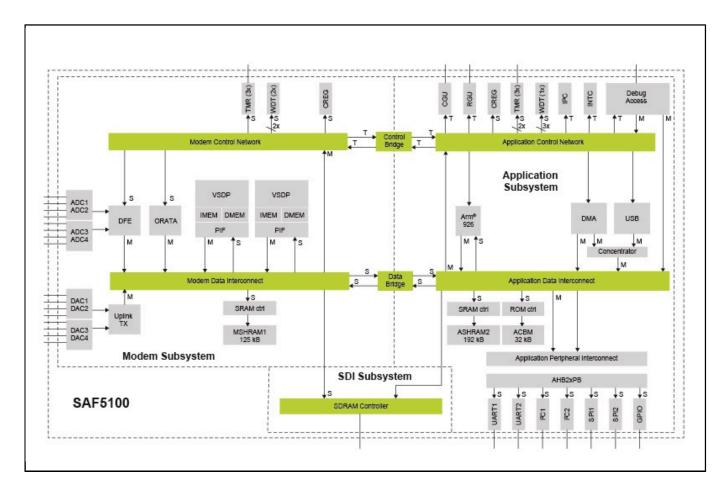

The SAF5100 this baseband processor includes Analog-to-Digital Converters (ADC) and Digitalto-Analog Converters (DAC) for interfacing with an external transceiver. Digital components included are:

- Digital Signal Processors (DSP) for advanced radio (de)modulation

- Hardware Accelerators (HWA) for IEEE 802.11p WiFi standard PHYsical layer (PHY) reception

- A microcontroller core for IEEE 1609.4 Medium Access Control (MAC)/Logical Link Control (LLC) processing

- Several standard interfaces such as Universal Serial Bus (USB) and SPI are included for connecting to an external host

The SAF5100 is available with an executable of a firmware comprising PHY/MAC (IEEE 802.11p and ETSI EN 302 663) and LLC (IEEE 1609.4 and ETSI EN 302 663) to be loaded into the RAM of the SAF5100.

## Software Defined Radio Processor for V2X Communication Block Diagram Block Diagram

### View additional information for Software Defined Radio Processor for V2X Communication.

Note: The information on this document is subject to change without notice.

#### www.nxp.com

NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2024 NXP B.V.